电子时钟控制系统设计——来自光与电的浪漫

实验题目:电子时钟控制系统设计

——来自光与电的浪漫

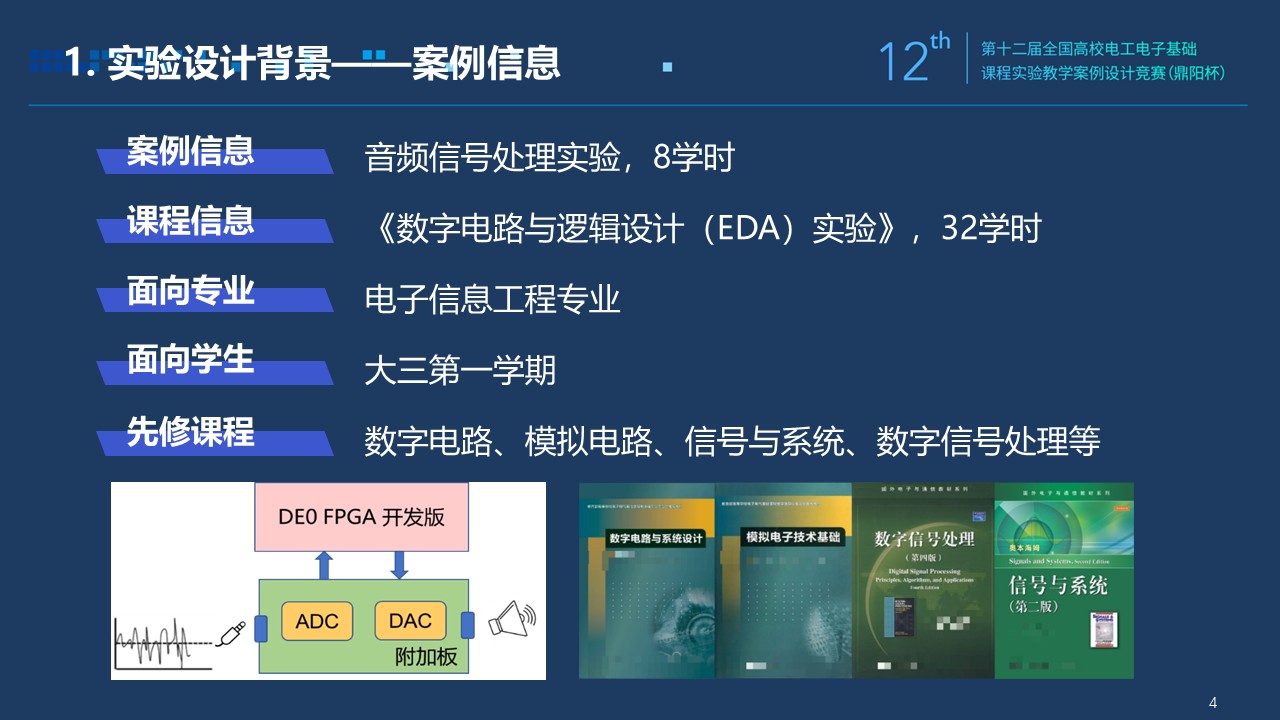

课程简要信息

课程名称:电子时钟控制系统设计——来自光与电的浪漫

项目学时:12学时

适用专业:通信工程、电子信息工程

学生年级:三年级、第五学期

实验内容与任务

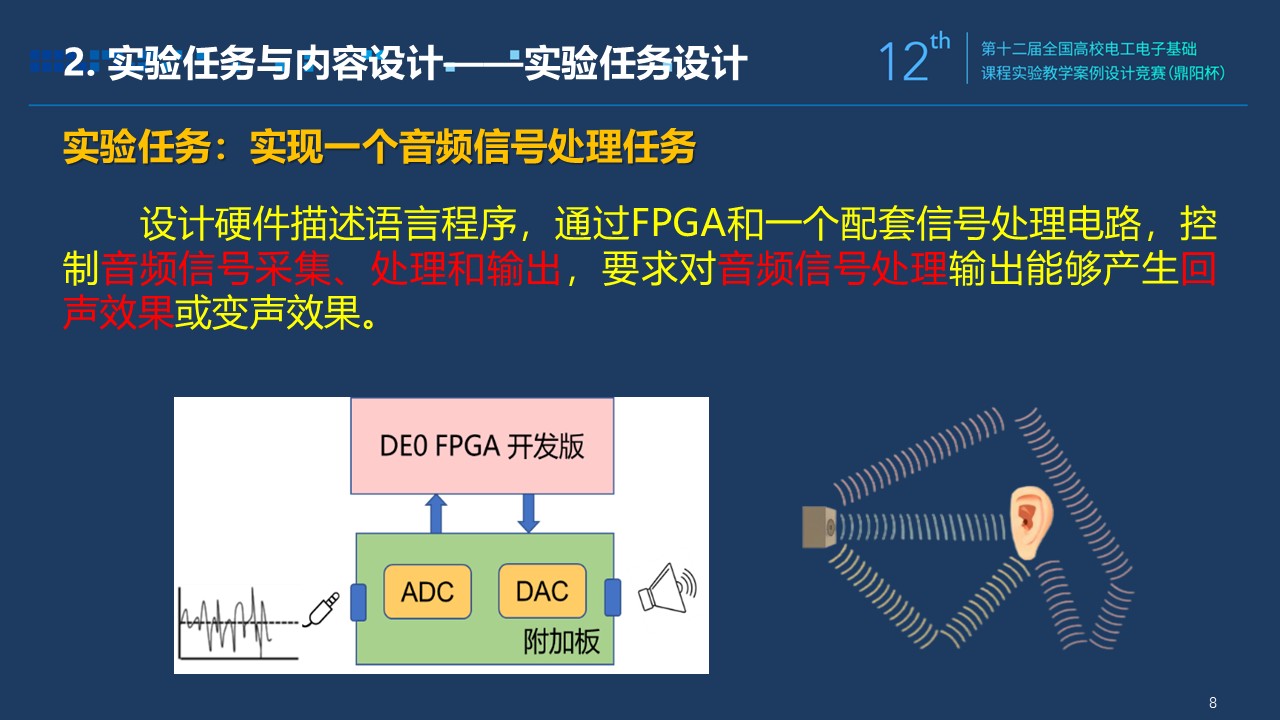

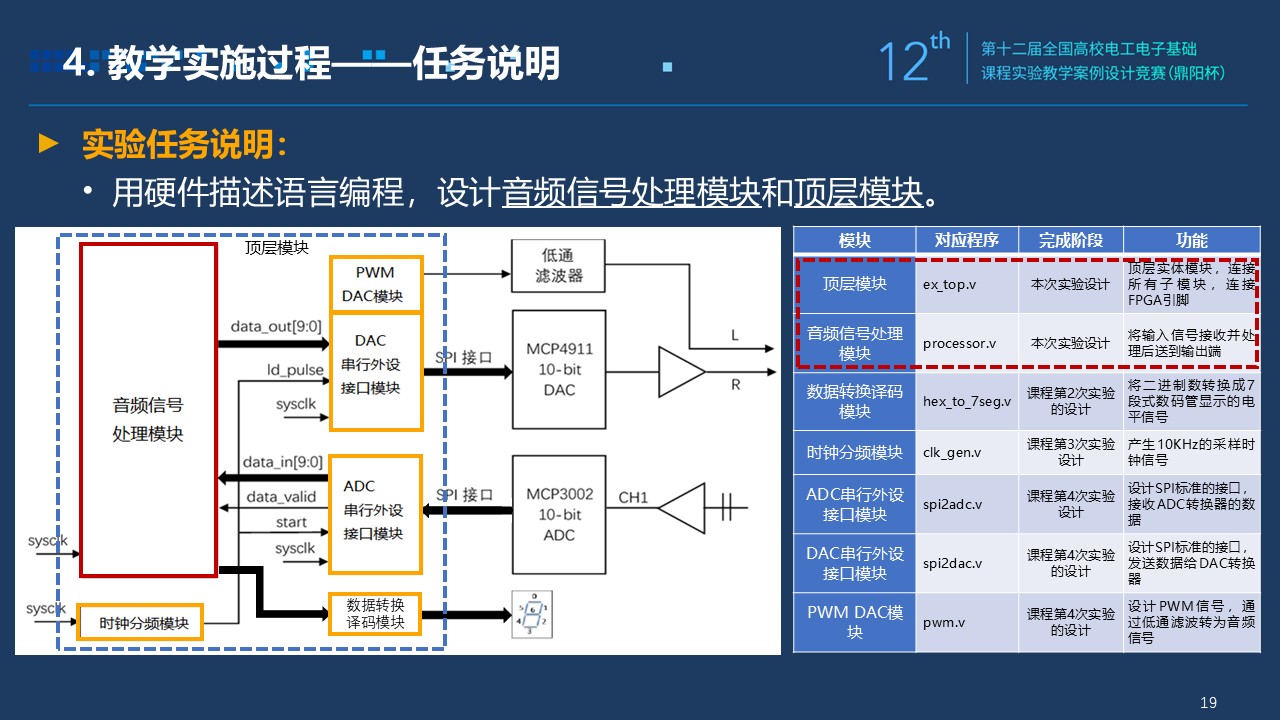

任务:项目综合了模拟电子技术、电子设计技术基础、FPGA技术及应用、通信原理课程内容,依托XILINX实验开发板、VAVADO软件、altium designer软件、元器件焊接等进行开发设计。

项目功能电路分为电传输部分和光传输部分。电传输部分基于FPGA开发板进行开发,包括:数据与控制输入模块、电子时钟模块、载波产生模块、显示模块、发送模块。光电路部分包含了光电转换发送模块电路、光电转换接收模块电路、滤波电路、整形电路、信号接收放大电路、电源电路。

电传输部分将通过FPGA分频电路产生出多个不同频率的数字载波信号,传输数据由拨码开关选择,并在系统中设计电子时钟功能,使数据在电子时钟跳变和拨码开关选择不同的共同控制下,以不同数字载波频率发送给光传输电路,光传输电路通过激光传递信号,在接收端通过光电转换电路将接收到的信号转成电信号并在数码管上显示相应的信息,本任务分为以下几个模块:

(1)数据与控制输入模块:当按下BTN0时对系统进行复位,用八位拨码开关作为数据输入,4位拨码开关sw0~sw3输入的数据输出到数据发送模块进行数据发送,4位拨码开关sw4~sw7表示载波控制组组数。

(2)载波产生模块功能:由于采用的数字载波频率不同,数据的传输速率是不同的。不同的数字载波频率由开发板50MHz时钟经过分频获得。考虑到收发载频不同步的问题,采用16位采样时钟对接收数据进行采样,故用5000×2=10000个脉冲作为最高采样时钟,5000为主低电平持续的时钟个数。设计采用10种载波频率,分频比2R分别为10000、9000、8000、7000、6000、5000、4000、3000、2000、1000。R为分频比的一半,载波信号占空比为50%。

(3)电子时钟模块功能:同时将晶振产生的50MHz时钟驱动信号进行分频,生成具有时、分、秒的数字钟电路,按24小时制计时,用于控制发送方与接收方的载波频率同频跳变。以每秒选频1次,不同的时、分、秒控制选用不同的载波频率。

(4)显示模块:收发双发分别用4个数码管显示系统工作过程。要求:第1个数码管显示发送的数据,第2个数码管显示接收的数据,第3个数码管显示载波频率的组数,第4个数码管显示控制频率切换的同步信号。

(5)光电转换发送电路将电信号转成光信号,通过激光管发射,将不同频率的电信号搬移到光频谱上进行传输,实现光传输。

(6)光电转换接收电路、信号接收放大模块电路、滤波模块电路、整形模块电路是将接收到的激光信号恢复成电信号传递给FPGA开发板,将接收到的电信号恢复成原始信号送到数据显示模块进行显示。

实验过程及要求(限300字)

-

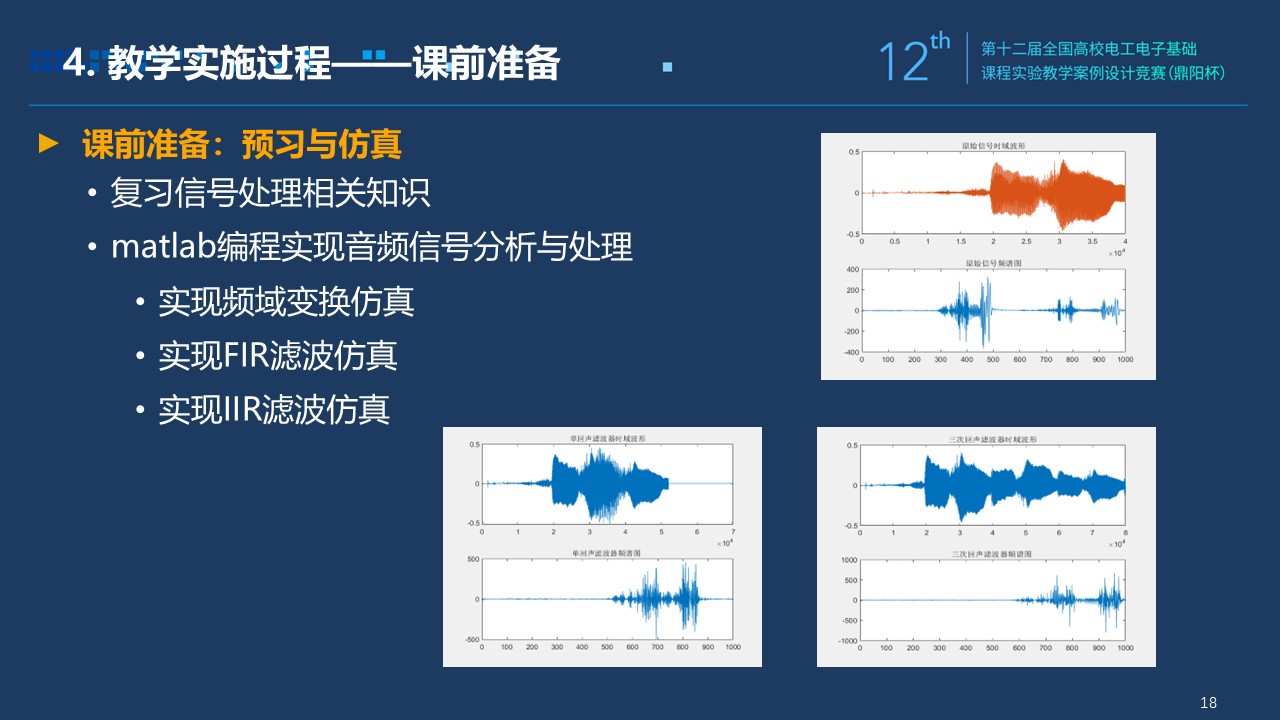

实验前在超星平台发布任务,学生做好课前预习。回顾模拟电子技术知识、焊接要领、查询跳频相关原理等,掌握Verilog HDL硬件编程语言、VIVADO和Modelsim软件的使用方法,了解不同型号FPGA开发板的使用方法。

-

实验要求2-3人一组,分工协作,自行制定实现方案,详细记录实验问题及解决方法。

-

学习数据与控制输入模块、基带跳频控制模块、显示模块、解基带跳频模块的设计方法,运用Verilog HDL硬件描述语言实现仿真并下载。

-

课余时间对电转换发送模块电路、光电转换接收模块电路、滤波模块电路、整形模块电路、信号接收放大模块电路、电源电路进行焊接调试并进行数据记录。

-

撰写设计总结报告,包含了设计原理、设计方案、设计流程、设计结果。

-

录制作品展示视频,要求对视频进行字幕添加和特效的编辑。

-

答辩展示作品视频,老师现场根据仿真测试的结果进行提问,不同组的同学也可以随机提问,现场作答,学习交流不同解决方案的特点。

相关知识及背景(限150字)

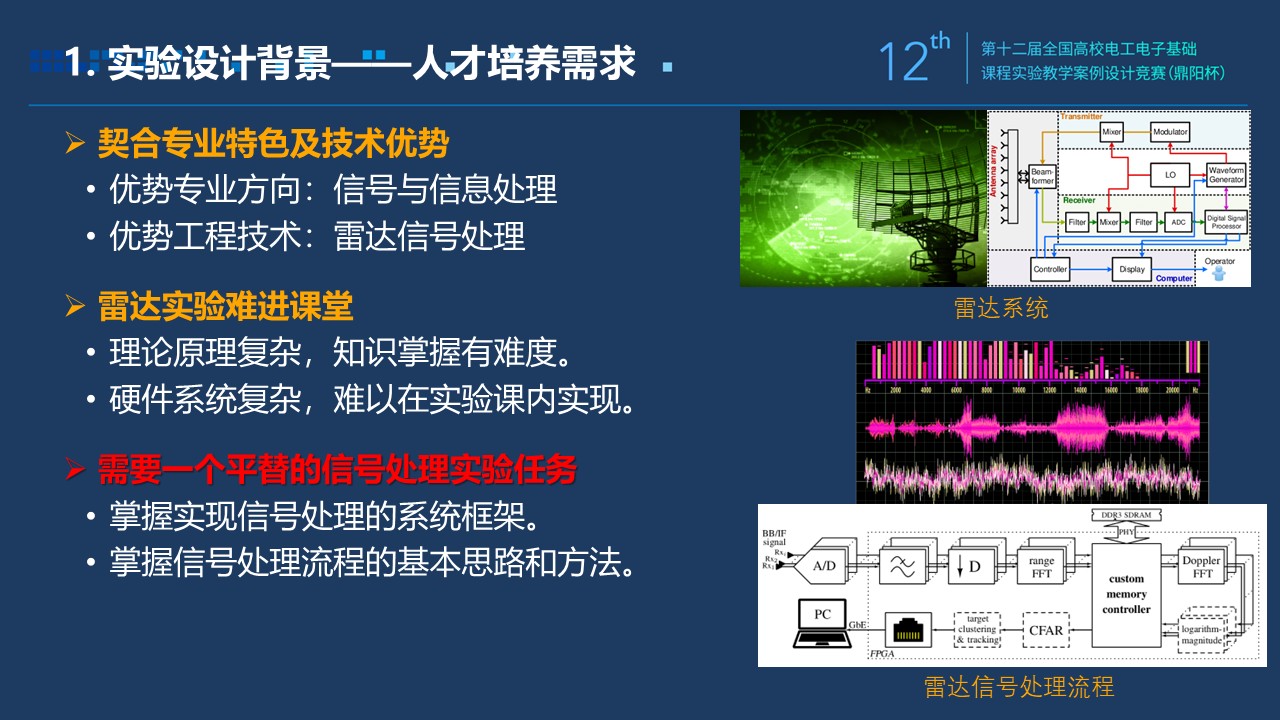

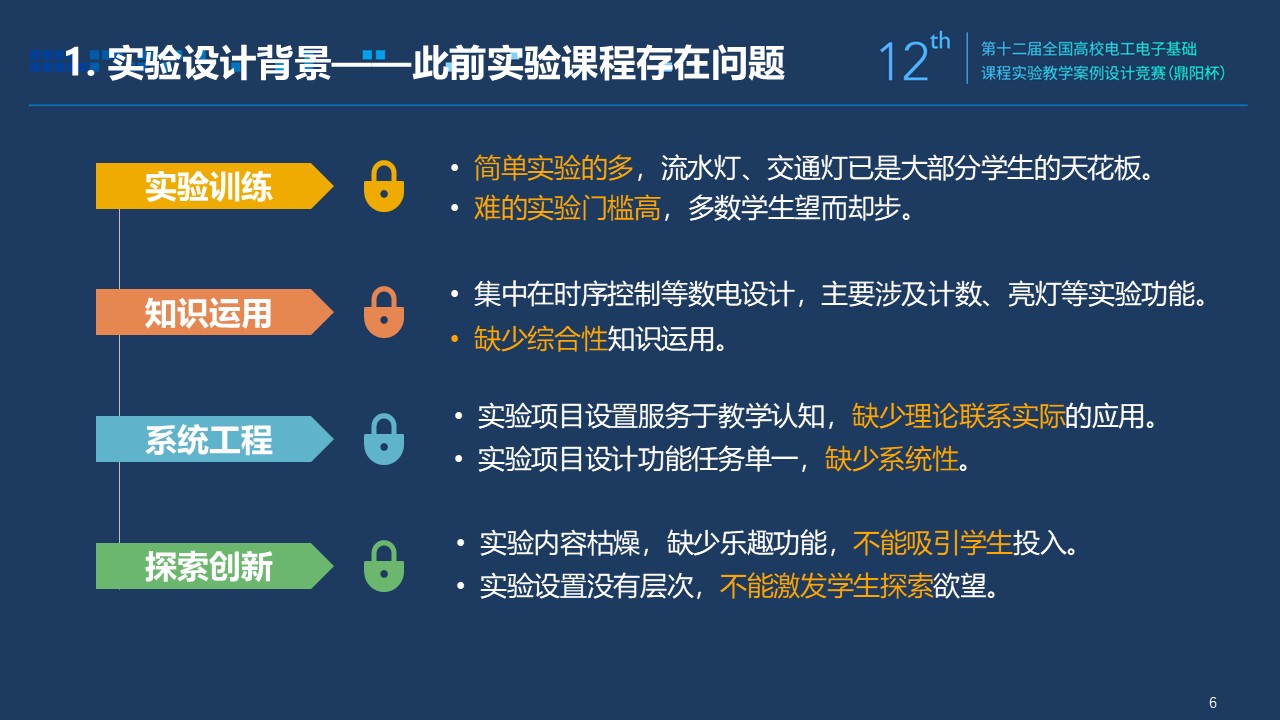

传统FPGA技术及应用课程以讲授教学型的中小规模电路为主,与产业和技术应用趋势严重脱节,无法培养学生的创新思维和知识迁移能力,导致培养的学生不具备胜任FPGA岗位工程师能力。课堂中所学的知识与科技发明、实际的技术应用、脱钩,前序课程学完就忘,无法在专业领域进行综合应用。

为了进一步在高校教学中落实习主席在2023年9月提出的推进新质生产力发展的方针与政策,在教学中融入创新、协调、开放、共享、绿色理念。紧跟激光通信应用与海洋遥感领域的科技发展,提出了基于激光和时钟自动跟踪控制二次跳频系统设计,将科技、通信、教学有机融合,组成一个即可以提高学生认知、扩展学生思维,又可以培训学生兴趣、锻炼学生动手能力的项目,为后续创新实践和入职FPGA岗位工程师打好基础。

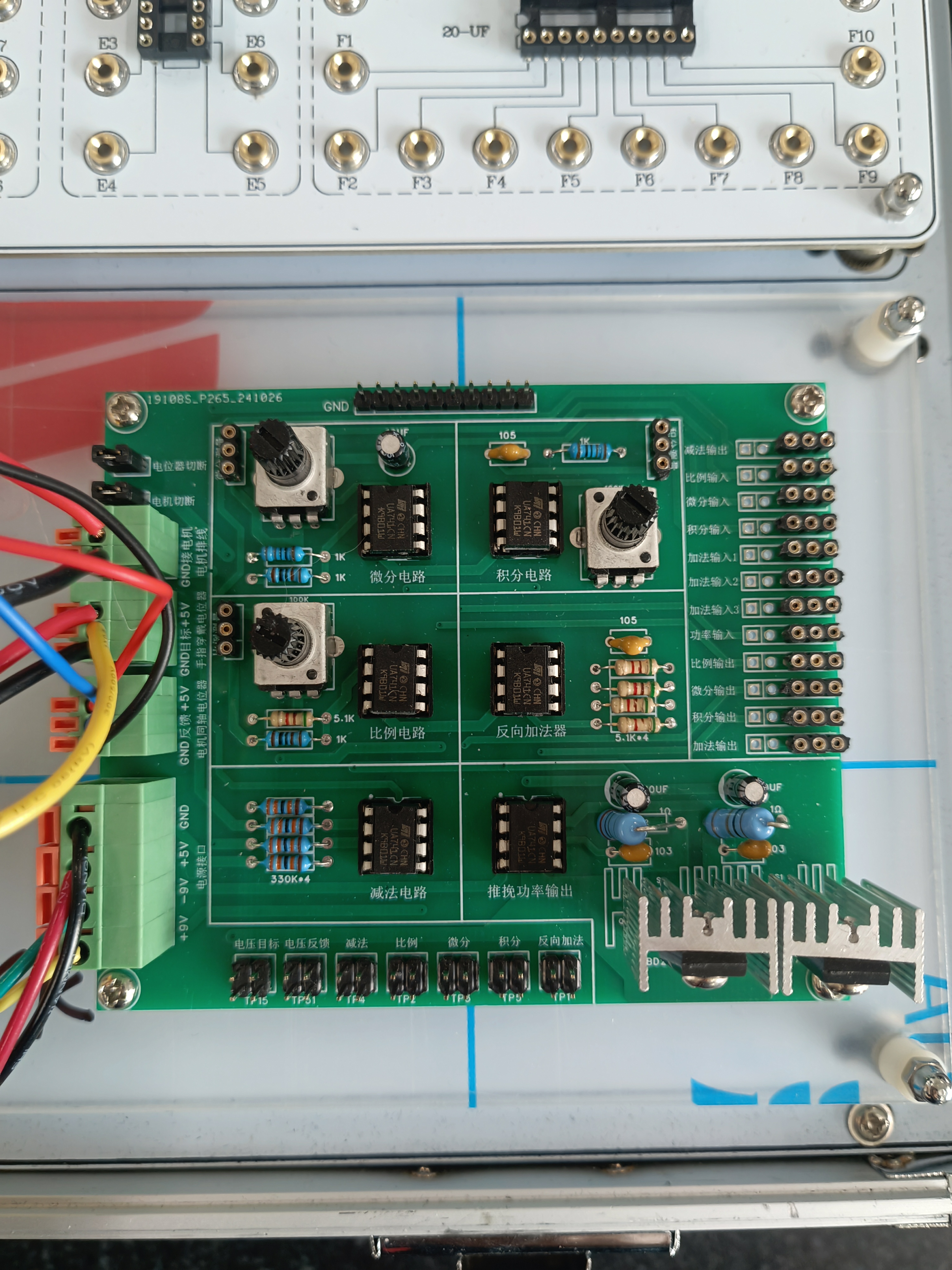

实验环境条件

学生实验环境如图1,主要包含有基础仪器,DS1102ES数字示波器、SFG-1003信号发生器

GPS-3303C稳压电源,另外包括电烙铁、焊接放大器、FPGA开发板,每个试验台配有云端桌面,安装有Xilinx公司的Vivado

2019.2软件、高云的Gowin云源软件,学生可通过FPGA开发软件进行项目设计,老师针对实验课程的实验参考资料上传到试验台电脑共享,学生打开电脑可以进行实验参考资料的访问和阅读。

学生实验环境如图1,主要包含有基础仪器,DS1102ES数字示波器、SFG-1003信号发生器

GPS-3303C稳压电源,另外包括电烙铁、焊接放大器、FPGA开发板,每个试验台配有云端桌面,安装有Xilinx公司的Vivado

2019.2软件、高云的Gowin云源软件,学生可通过FPGA开发软件进行项目设计,老师针对实验课程的实验参考资料上传到试验台电脑共享,学生打开电脑可以进行实验参考资料的访问和阅读。

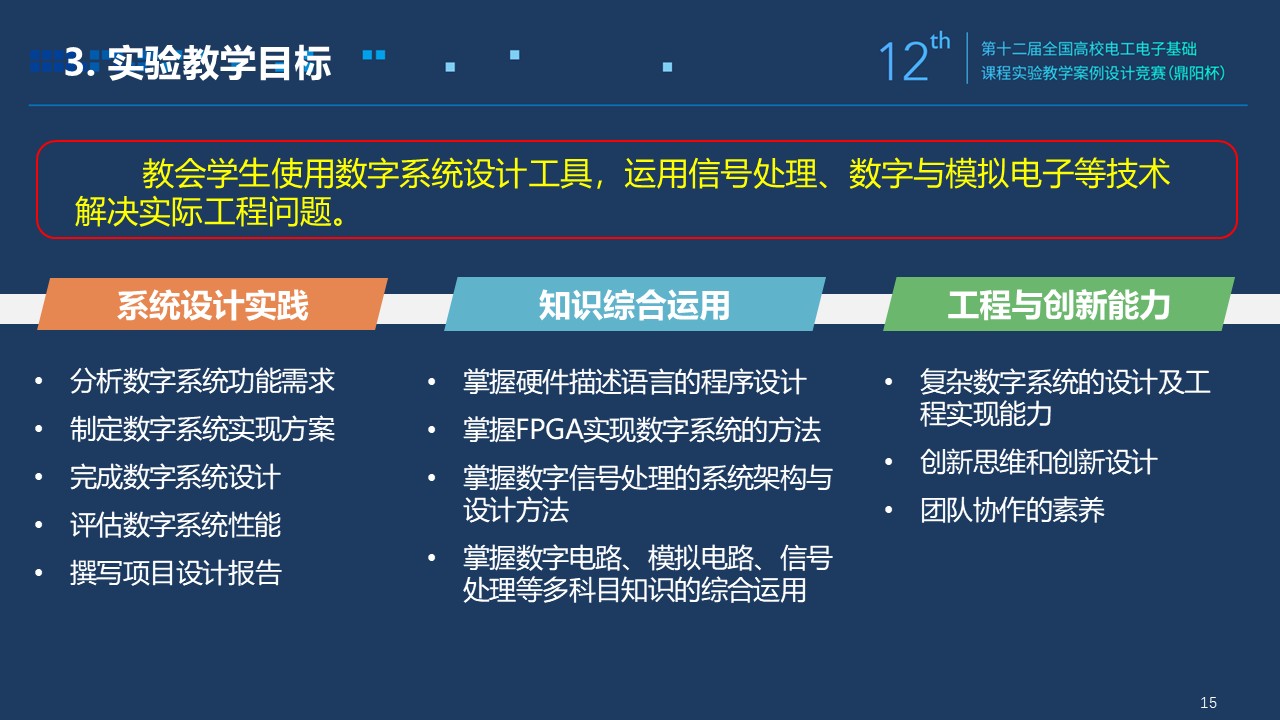

教学目标与目的(限150字)

通过此项目的学习和实践,学生可以复习模拟电子技术、电工与电子技术、通信原理课程中所学到的知识并进行综合的应用与实现。其次学生能够在该项目中学到电路的模块化设计、自顶向下的设计方法,可以通过Verilog HDL语言实现电路的设计以及程序仿真验证、芯片约束、综合、实现、生成位流文件并下载,并通过测试与分析对项目做出技术评价,学生能够体会到严谨的学科素养和开拓进取的创新精神。最后,学生通过对项目报告的撰写和答辩,学生的辩证思维能力、表达能力、团队合作能力得到了训练。

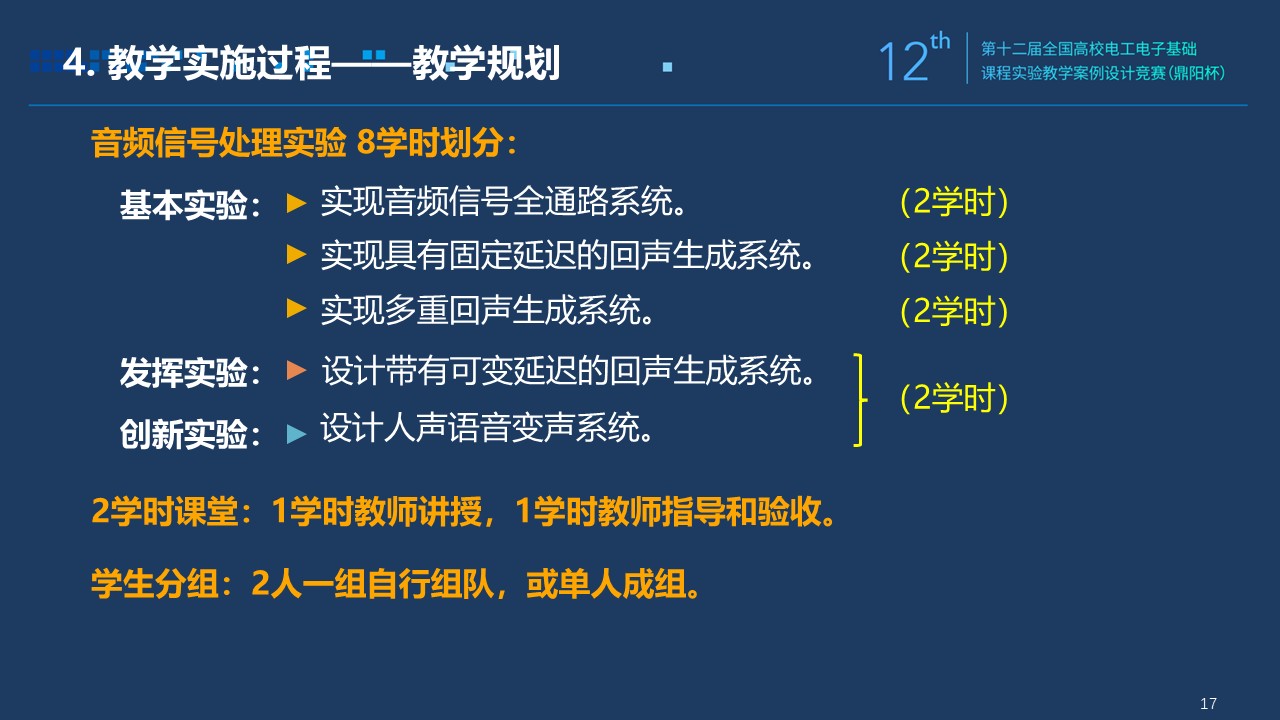

教学设计与实施进程

(1)本实验是《FPGA技术及应用》课程设计的综合实践项目,教学主要思路包括:

- 科技反哺教学,培养科技创造者和使用者。

本项目是发明专利的低阶版,属于综合性实验案例。将电子信息专业的《模拟电子技术》、《电工与电子工艺》、《通信原理》、《FPGA技术及应用》知识体系融会贯通,学生通过该项目的实践可以深入的理解数字逻辑系统的开发流程、FPGA技术设计原理、数字跳频通信等原理,明白了相关知识的联系,融会贯通的实现的功能设计。

- 企业案例教学,探索多元人才并因材施教。

实践中检测理论,学生通过企业真实案例项目的学习能够熟悉实际工程案例中的方案设计、程序开发、软件仿真、调试优化、报告输出计、答辩汇报等工程环节,在实践过程中体会团队合作的重要性和团队成员共同完成一个项目的互补性。

- 应用导向牵引,把控新兴战略及发展趋势。

对准我国自主研发的北斗卫星的工程在授时方面的应用和“威海一号”激光通信项目依托高精度瞄准捕获跟踪创造性地架起星间、星地高速激光传输“桥梁”,实现了大容量海洋遥感数据、渔船检测数据的实时回传,可将星地激光通信速率提升至40Gbps的大国工匠科技信息,向学生强化科技兴国的理念,同时科普该项目用我国自主研发的北斗卫星替换教学项目中的电子时钟功能,通过激光传输信息,可以大大提升通信的安全、加快通信速率。

(2)本实验的过程是一个比较完整的实践工程,需要经历学习研究、方案论证、系统设计、各子模块设计功能分配、程序编写、软件调试、功能仿真、芯片约束、设计综合、设计实现、位流文件生成和下载、硬件焊接测试、设计报告撰写、项目答辩等过程。在实验教学中,我们通过以下几个方面加强对学生的引导:

- 布置任务(课前)

该阶段老师在超星平台布置任务,让学生查阅时事科技新闻,同时复习通信专业课程中所学习过的载波通信以及模拟电子技术中的基础电路知识,引导学生通过自制的在线视频熟悉FPGA开发环境。

- 任务分析(2学时)

该阶段主要以教师讲授为主,分析该项目的背景、实践内容、实践原理、实验要求,最终完成的实践作品效果、实践成绩评定方式等。使学生明白本实验课程所要完成的工程目标和内容,在学生建立起对将要完成项目基本概念基础上,讲解如何实现系统的基本设计思路、可以采用的设计方法和手段,让学生根据自己特点自行选取,调动学生参与的主动性和积极性。

- 仿真设计(4学时)

该阶段以学生分组研讨设计为主,学生2~3人自由组合,要求学生先进行方案设计,功能模块划分,集中研究、分析、讨论完成项目的内容、步骤,进行工作内容分工,用 Verilog HDL硬件描述语言对各模块进行仿真设计,以此培养学生团结协作的团队精神和意识。每人独立完成各模块的设计,使每个人都能掌握设计方法、技能。老师解答设计中出现的共性问题。

- 焊接实物(课外完成)

该阶段电训实验室全天开放,由学生课外完成,实现光电转换接收电路、信号接收放大电路、滤波电路、整形电路进行焊接调试。

- 板上调试(4学时)

该阶段学生将仿真成功的程序代码下载到开发板进行调试。仔细核对查验预定功能的完成情况,实验功能的准确性、可靠性。为提高和区分学生设计的质量,还可通过软件平台提供的分析报告,比较各组学生设计所占用的芯片资源统计表。鼓励学生精益求精,不断优化设计,扩展功能,开拓本项目的应用领域。

- 答辩汇报(2学时)

汇报时提交设计报告和通过PPT向全班同时进行展示项目实践效果,小组与小组之间随机提出问题,通过相互交流取长补短,进一步提升对各设计环节的认识和对知识的深化,拓宽知识面。老师和同学根据其他组同学提交的设计报告和汇报情况进行打分。

(3)实验教学中,主要在以下几个方面加强对学生的引导:

-

引导学生自顶向下的设计思想,能够结合实际划分功能。

-

引导学生学习系统结构与功能模块构成,重点关注功能模块间的接口方式与参数传递。

-

引导学生注意工程素养,程序的注释、程序的可读性、各行的缩进等。

-

在调试中,引导学生学会分析错误、排查缺陷、寻找问题并解决问题的方法。

-

提醒学生注意安全用电,不要损坏实验电路板、按要求规范操作步骤。

实验原理及方案

(1)实验的基本原理

该系统将FPGA技术和模拟电子技术、通信技术知识进行整合,如图3所示,发送部分中的数据与控制输入模块、电子时钟控制模块、发送模块、显示模块均基于FPGA开发板实现电信号传输,光传输部分通过模拟电路设计实现,将数据利用激光进行传输。详细功能分析如下:

电传输部分以不同速率进行数据传输,即将原始数据搬移到不同的频率的数字载波上进行传输。通过FPGA可以产生N个不同频率数字载波信号,可将N个不同频率数字载波信号进行预定规则进行的排序,将排列不同的载波信号分配到不同的频率组中并对频率组进行编号,可通过拨码开关对频率组进行选择,选择的不同的频率组编号及选择了不同载波排序,再通过电子时钟秒的跳变对频率组中具体的频率进行预定顺序切换,以每秒改变数字载波1次为例,不同的时、分、秒控制选用不同的载波频率。

光传输部分将信号搬移到光谱上进行传输,通过光电转换发送电路、接收端光电转换接收电路、信号放大电路、滤波电路、整形电路、接收模块(串口)、显示模块进行设计实现功能。

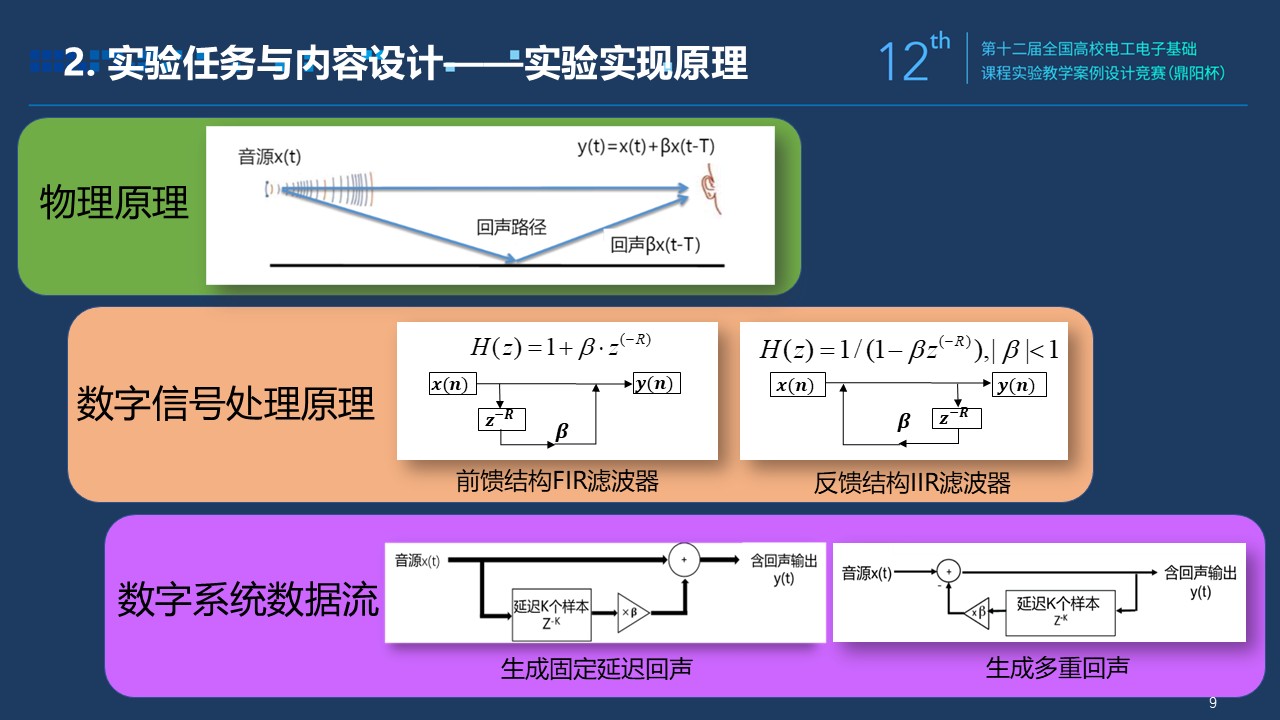

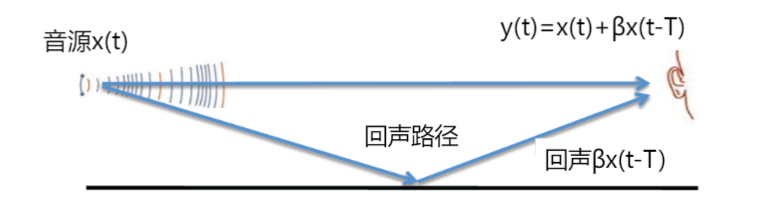

(2)设计依据

电传输部分,由于传输数据乘载数字载波频率中进行传输,发送端的数字载波在不断改变,接收端也应当做出相应的改变,否则无法正确还原发端信号,这使接收数据方实现变得困难。常用办法是收发双方预先确定一个频率跳转表,在约定的时间同时跳转。但这种方法跳转慢,控制复杂。为此提出一种利用收发双方都有的,经过预先校准好的电子时钟,利用电子时钟有相同钟点的特点,自动以钟点为准进行跳转,从而可以很好地实现收发双方同步切换数字载波。为使学生实验不致太复杂,本项目选取时钟的秒钟个位,即0、1、2、…9秒的循环作为信道循环跳变的控制信号。如图4所示。

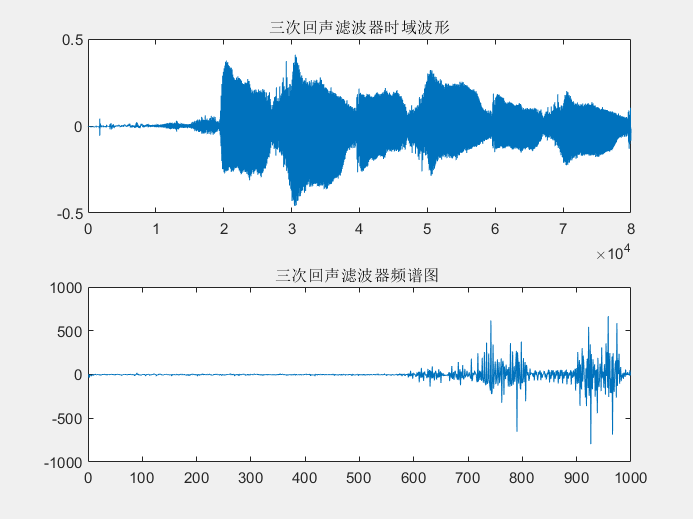

光传输部分,如图5、6、7,所示,通过光电转换发送模块,将电信号转换成光信号,不同频率的基带信号利用三极管开关作用,控制激光管是否发光,激光接收器接收到信号为1,未接收到信号为0。接收端通过信号放大电路、整形电路、滤波电路恢复成原来的基带信号传输给FPGA开发板。

(3)完成任务的思路方法

为便于通过肉眼观察检查学生的设计效果,可将设计任务所要完成的功能确定为:

(a)用拨码开关或者按钮输入待传输的数据,4位拨码开关选择数据,如果用按钮作为数据输入,则每按下一次,计数器加1,用一个4位寄存器暂存该信号,输出4位数据,如用2个按钮可输入2个4位数据构成8位数据。学生可选1个或2个按钮获得4位或8位数据。

(b)从开发板上获取50MHz晶振时钟作为系统的驱动时钟。

(c)用一个按钮作为系统的复位信号输入。

(d)用一个按钮作为系统发送数据的使能信号,每按下一次,发送一次数据,同时另外一开发板接收相应数据。

(e)用拨码开关作为载波频率的选择控制信号。设计中通过对时钟的分频获得10个载波频率:5000、4500、4000、3500、3000、2500、2000、1500、1000、500Hz。他们的选取可以任意组合,每一种组合称为一个跳频编组方案,如:2500、1500、3000、4000、500、3500、1000、4500、5000、2000 Hz可以是一种组合。用拨码开关选择数字频率组,学生至少应采用这个频率编组:5000、4500、4000、3500、3000、2500、2000、1500、1000、500Hz,通过10秒来分别选取这10个载波频率。学有余力的同学,可以编制多个频率编组,内涵不同顺序的频率,用时分秒来选取不同的载波频率。

(f)数据传输帧格式采用RS232协议的帧格式。即1位低电平起始位表示数据传输开始、4位或8位待传输数据、1位奇偶检验位、1位高电平停止位。空闲位用逻辑“1”状态表示当前线路上没有数据传送。帧格式如图8所示。

(g)用4个数码管显示系统工作过程。其中:用1个数码管显示秒钟的个位秒,变化范围0~9;用1位显示正在使用载波频率的编号;用1位显示发送数据,用1位显示接收数据。

(h)数据通过串口发送模块发送到光电转换发送模块,将信号用光进行传输。激光管亮表示发送1,熄灭表示0。

(j)在接收端,通过光电转换接收电路、整形电路、滤波电路进行信号处理后,转至FPGA开发板进行光传电设计,最后送至显示模块显示接收到的数据。

(i)开发板加电后,按下复位按钮时,系统应能复位到初始状态。按下数据输入按钮和发送使能按钮后,进入系统工作状态。

(4)完成任务的平台选取

为统一标准便于比较,依据实验现有设备进行项目的设计。软件平台采用Xilinx公司的Vivado 2019.2软件平发平台,硬件平台采用Spartan-3E系列的XC3S100E FPGA芯片,设计程序的编写选用Verilog HDL硬件描述语言。下载电缆采用14线JTAG接口。采用220V市电适配器为开发板供电。硬件电路可根据先修课程模拟电子技术自选。建议用激光管和硅光电池。

设计过程参考

(1)数据输入模块设计

拨码开关输入数据时,通过4位拨码开关,可以有16种不同数据的选择方案提供。编写数据输入模块程序,运行综合程序得电路如图9所示。

运行数据输入模块仿真程序图10所示。

从图11可见,每按下一次按钮key1,key2,key3,输入寄存器data8、fsel10就做一次加计数,从而获得8位和4位输入数据。

(2)数字载波产生模块

编写数字载波产生子模块的Verilog HDL程序。

经综合后的电路如图11所示。

编写仿真程序,运行程序得仿真波形如图12所示。

- 编写电子时钟产生模块程序,运行程序得电路如图13所示。

电子时钟产生模块在系统时钟驱动下,生成具有时、分、秒的电子数字钟数据,按24小时制计时。要求:

(a)准确计时,以数字形式显示时、分、秒的时间;

(b)按1Hz精度进行计数,按数据发送频率驱动数码管显示。

(c)时、分、秒均为高位和低位两位数字,分秒的低位为0~9计数,高位为0-5计数。

(d)低位计到9秒后清0,同时向高位进位。

(e)高位进位到5后再进位就清0。

(f)小时为24小时,在高位为0、1时,低位可计数范围为0~9,当高位为2时,低位只能计数到0~3,然后再有进位时就复位。

(g)单独运行电子时钟模块时,驱动显示为6个数码管显示两位的小时、分钟和秒钟。通过扫描使每个数码管轮流显示。在作为载波选取时,只使用秒钟的个位,并显示秒钟个位。

(g)单独运行电子时钟模块时,驱动显示为6个数码管显示两位的小时、分钟和秒钟。通过扫描使每个数码管轮流显示。在作为载波选取时,只使用秒钟的个位,并显示秒钟个位。

编写仿真程序,运行程序得仿真波形如图14所示。仿真中为便于观察,将分频次数作了减少。

- 编写载波选取控制模块程序设计

载波选取控制模块从载波产生模块输出的10个载波频率中选取其中一个作为载波输出信号,用作载波信号承载数据进行高速传输。控制信号来自电子时钟的时、分、秒输出信号,他们控制按发送与接收双方预先商定的方案选取载波信号。由于1天有24×3600=86400秒,故可在1天内提供86400个不同的频率跳变方案,而敌方无法获取这种方案,等刚捕获到某一频率在通信时,通信双方已跳转到其他载波频率上,因而难以截获通信内容。传输双方的信号在每个频率上停留的时间越短,传输越安全。例如还可以100毫秒、10毫秒、1毫秒等为载波持续的时间片。代价就是发送与接收方的时钟同步越困难。

本项目采用电子时钟切换传输频率的优点在于切换的频率跳变方案多,最重要的是同步切换简单可靠,只要通信收发双方将时钟校对,数据传输过程中的频率跳变可以随着双方时钟的变化自动可靠完成。

为便于肉眼观看跳频过程,本设计采取1秒更换一次载波的方式,由时钟的秒的个位输出进行控制,主要是方便利用开发板进行演示。而增加时、分、秒的高位的选频方法与演示中只选用秒的低位来控制载频的方法完全相同。尽管没有用到时、分、秒的高位这些信号,设计中还是将其作为输入,以方便今后利用这些信号进行控制方案的扩展。

编写载波选取控制模块,运行综合程序得电路如图15所示。

从图16可见,时、分、秒的高位这些信号没有连接,可用于扩展选频能力,这里只用到秒钟的个位对频率产生模块输出的10个频率进行选择。

编写载波选取控制模块仿真程序,运行载波选取控制模块仿真程序图16所示。

(3)数据发送模块程序设计

这里的参考发送程序以每帧数据中待传输数据位为8位进行设计。

数据发送程序的设计思路是在发送数据前先发送1个数据位的低电平,然后分别发送8个数据位、1个奇偶校验位和1个停止位,即每帧数据占用11个数据位。每个数据采用计数器进行控制,并且每个数据位占用16个计数脉冲。这样,每个位的发送时间由计数器对采样时钟计数个数确定,其起始位置分别为0、16、32、48、64、80、96、112、128、 144、160、168。数据的发送受起动信号txen控制,当其为高电平时,使缓冲信号txstart为高电平。发送开始时txen为低电平,使缓冲信号txstart为低电平。然后txen为高电平,并在同低电平的txstart的取反值相与后得到高电平txstart信号。该信号与低电平信道忙闲信号idle的取反值相与,得到高电平send数据发送标志信号。在整个数据发送期间该信号一直为高,当数据发送完后变为低电平表示一帧数据发送结束。完成数据发送程序编写,运行综合程序得电路如图17所示:

编写数据发送仿真程序,运行仿真数据发送程序得仿真波形如图18所示:

从图19可见,复位后,在时钟clksp驱动下,当发送使能信号txen为高电平时,若发送数据datain=10101011b时,txen先输出一个低电平表示数据发送开始,随后低位在前,高位在后发送数据10101011b。此后再发送1位停止位1。一帧中总计发送11位数据,此后一直发高电平表示线路空闲。由于发送使能信号txen再次输出一个低脉冲后,发送第二帧数据10101011b。

(4)数据接收程序设计

接收程序接收发端发来的8位一帧的串行数据。接收从检测到低电平开始,计数16位采样脉冲,并在第8个脉冲进行采样。这之后每隔16个脉冲对数据位进行一次采样。采样完8位数据后再采样一个奇偶校验位和1位停止位。每接收一位数据进行一次奇偶校验以判断接收数据是否正确。当8位接收数据判断为正确后输出到对外接口。

编写数据接收程序,运行综合程序所得电路如图19所示:

编写数据接收仿真程序,运行仿真数据接收程序所得仿真波形图20所示:

从图20可见,在采样时钟clksp驱动下,当接收信号rx为低电平后,开始接收数据。

当接收有效标志rdsig为高电平时,表示一帧接收数据dataout=10010101b接收完成。如果此后rx再次为低电平,以开始接收新的一帧数据。

(5)显示模块程序设计

4个数码管的驱动可分为单管显示驱动和4管同时显示驱动。单个数码管显示驱动电路设计方法是将待显示4位数据存入数码管显示寄存器,再将其调入驱动显示电路进行显示。然后设计一个七段译码器,将4位二进制数译为七段码seg7输送到七段数码管引脚。4待显示数据从右到左分别为第1个数码管显示待发送的4位数据、第2个数码管显示串行接收的4位数据、第3个数码管显示秒钟个位时间4位数据、第4个数码管显示载波编号4位数据。开发板输出每数码管显示程序编写运行程序后生成数码管驱动模块如图21所示。

图21 运行程序后生成数码管驱动显示模块

编写仿真程序,运行仿真程序后生成数码管驱动显示仿真波形图22所示:

图22 数码管驱动显示仿真输出波形

从图22可见:当复位信号rst为低电平时,输入数据寄存器、数码管扫描计数器清零,每个数码管显示0(七段编码为11000000)。当复位信号rst为高电平时,系统开始工作。4个数码管驱动信号依次变从计数器cntt_tub从0、1、2、3计数时,使数码管bit6依次轮流输入为0111、1110、1101、1011,这4组数据对应的七段编码1011-0000(3)、1000-0000(0)、1001-1001(4)、1010-0100(2)。设计达到预定要求。

(6)顶层模块程序设计

为便于观察电子时钟自动控制切换的工作过程,利用开发板的数码管、按钮进行显示和控制。本项目设计的电子时钟控制传输系统工作过程演示,是在系统50MHz晶振时钟驱动下,利用4位数码管的七段显示,以及复位按钮、数据输入开关、频率编组选择开关、发送使能按钮,分别进行系统复位控制、载频编号、电子时钟的秒个位、1位接收数据、1位发送数据的显示。

本设计主要利用复位按钮、8个拨码开关、晶振时钟引脚作为系统的数据输入和控制输入。采用按下reset时输出低电平时对系统进行复位操作,使用拨码开关sw0~sw3输入发送的串行数据,拨码开关sw4~sw7选择载波编组,按下按钮key时发送数据使能,开始发送数据。其系统工作资源分配如下:

(a)系统复位输入 当按下reset时对系统进行复位,4个数码管显示0。

(b)数据发送使能输入 使用拨码开关sw0~sw3输入发送的串行数据datax输出到发送模块进行发送。

(c)数据发送输出 从扩展口J10的1个端口输出发送数据tx。

(d)数据接收输出 从J10的另1个端口输入接收数据rx。

(e)发送数据的显示 用第0个数码管显示输出的发送数据datax[3:0] 。

(f)接收数据的显示 用第1个数码管显示接收的输入数据datar[3:0] 。

(g)秒钟个位数据的显示 用第3个数码管显示时钟秒钟个位数据send_l[3:0]。

(h)数字载波组编号的显示 用第2个数码管显示跳频编组编号sfn[3:0]。

将载波产生模块mfgen、电子时钟模块gen_clock、载波控制模块frqctr、串行发送模块uart232tx、串行接收模块uart232rx、数据显示模块tub6_sec8_show、数据输入模块、时钟产生模块、数据接收模块、数据发送模块、载波产生模块程组合起来就构成了系统总体结构的顶层文件,其功能为可按秒钟个位进行频率跳变、秒钟显示、载波编号显示、1位数据的发送、1位接收与显示。

编写系统顶层文件程序,运行综合程序后生成宽频带信道自动切换控制系统顶层模块结构如图23所示。

学生编写芯片约束文件,经综合、实现、生成位流文件jmpfrqtop.bit后下载到芯片,电路板操作和显示应达到预定要求。对有创新的学生,可酌情加分,以鼓励创新。

图23 电子时钟控制系统设计

如图23所示,载波产生模块mfgen_md输入信号为时钟信号50MHz,复位信号rst用一个按键控制,输出10个不同频率的载波信号;数据输入模块key_data_md输入信号为时钟、复位及四个按键,两个按钮可获得8位数据,第3位按钮输入获得对频率组合的选取,第4个按键为同步输出的发送使能信号txen,输出数据data8和选择频率信号fsel10,载波控制模块frqctr_md,输入为系统时钟、复位、10个不同载波频率信号,电子时钟秒的低位,输出信号clksp和跳频编组编号sfn;时钟产生模块gen_clock_md模块输入系统时钟和复位信号,输出1khz的扫频信号和秒时钟的低位信号;数据发送模块uart232tx_md在clkbps时钟的驱动下,txen使能有效时,开始传输datain数据,tx为该模块的串行输出;数据接收模块uart232rx_md在时钟clkbps的驱动下,接收完成dataout一帧数据;数据显示模块tub6_sec8_show_md输入信号有扫频信号clk_tub,跳屏编组信号fmo,复位,uart232接收的数据rxd_l和rxd_h,秒的低位s_l,发送数据txd_h,txd_l,输出为数码管的短码sec8和位码bit。经过下载测试得到以下效果图,如图24所示。以图上第一块开发板为例,数码管显示CE60,第一位数码管表示接收到的数据,第二数码管表示发送的数据,第三数码管表示频率组数,第四数码管表示电子时钟的低位。

图24 基于电子时钟的多载波控制系统下载效果图

实验报告要求

-

实验需求分析:查找资料,简述跳频通信的应用和价值。

-

实现方案论证:根据跳频通信技术要求,设计出系统总体构架和功能模块连接关联。

-

各模块指标分配:对各模块进行功能分配,提出各模块的技术指标。

-

各模块程序设计:编写各模块Verilog HDL应用程序,保存综合后的电路结构图。

-

各模块仿真测试:对各模块进行仿真波形测试,保存达到预定功能要求的波形图。

-

顶层文件设计:完成对各模块的连接,保存电路结构图,编写约束文件。

-

位流文件下载:经综合、实现、生成位流文件,连接JTAG电缆下载位流程序。

-

实验结果总结:观看结果,达到预定指标后写出实验总结和体会。

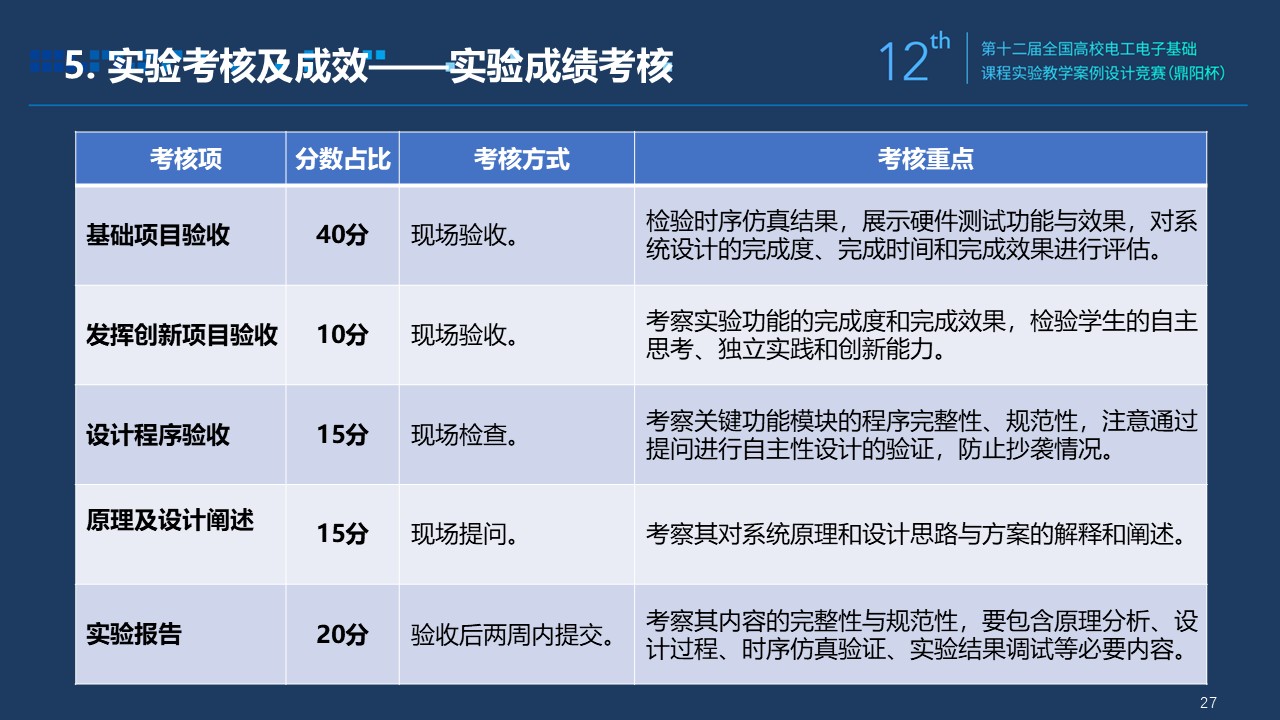

考核要求与方法(限300字)

(1)实物验收:实验课程结束后,提交实现预定功能的电路板,应能完成按钮的复位、输入数据、选择跳频组合、激光管发送接收、信号放大整形滤波功能,完成数码管显示时钟秒钟个位、频率组编号、1位发送数据和1位接收数据,且接收端显示的接收数据应与发送数据相同。

(2)实验质量:焊接电路板工艺性、FPGA电路总体方案中各下层模块功能指标分配应合理性,各模块电路图正确无错漏连接、各模块仿真波形正确。

(3)自主创新:有无在设计过程中体现的功能构思、电路设计的创新性,了解学生设计过程中有无自主思考与独立实践能力体现,如有可以考核加分。

(4)实验成本:检查有无对实验实验室平台、工具的损坏,通过对检测芯片资源的占用情况检测,评估设计的合理性和系统优程度。系统芯片资源占用少的可以适当加分。

(5)实验数据:通过检测查看电路板上按钮操作和数码管显示的可靠性,如时对时不对可酌情扣分。

(6)实验报告:审核实验报告的规范性与完整性。

(7)答辩汇报:答辩过程通过老师提问和同学提问环节,进行教师点评和生生互评。

项目特色或创新(可空缺,限150字)

多层教学内容协作,提升学生工程思维。多阶教学模式并进,提高学生自学习惯。

多维教学资源互补,打造协同教学模式。多层评价体系辅助,塑造因材施教范式。

图25 项目特色与创新

图25 项目特色与创新