PS2键盘识别显示

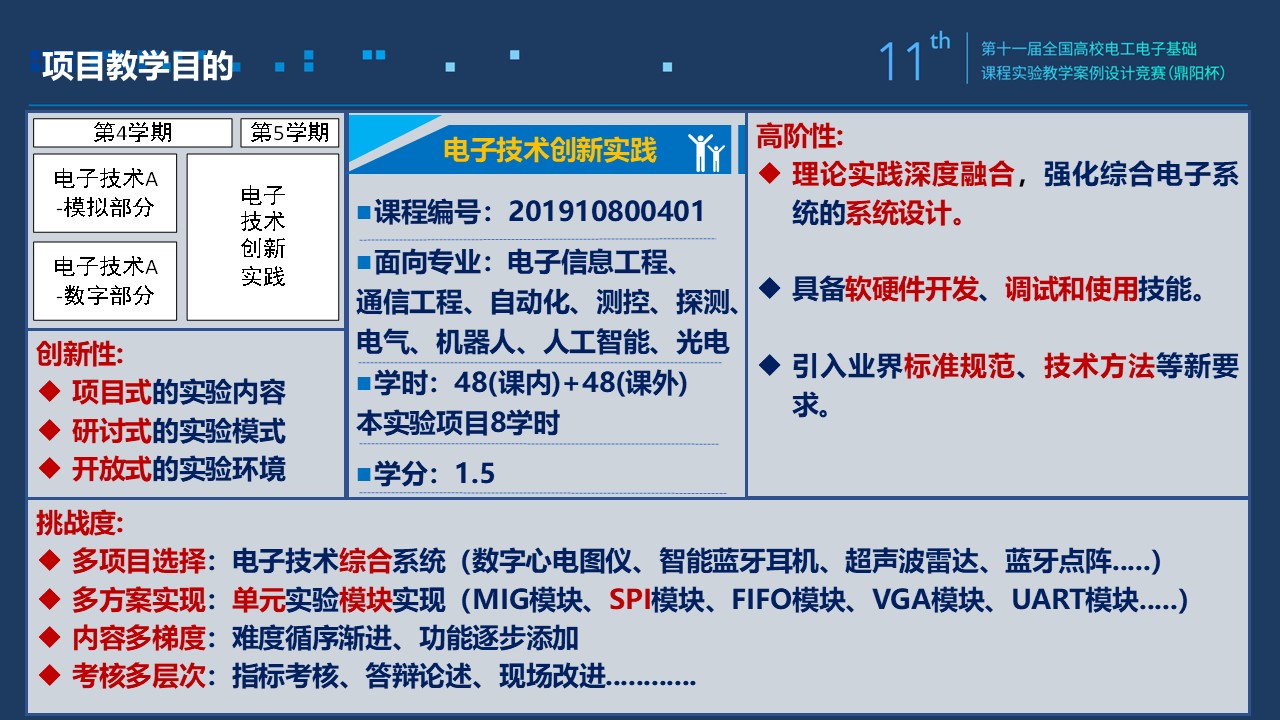

课程名称:电子技术创新实践

实验项目名称:综合逻辑电路的设计与实现--PS2键盘识别显示

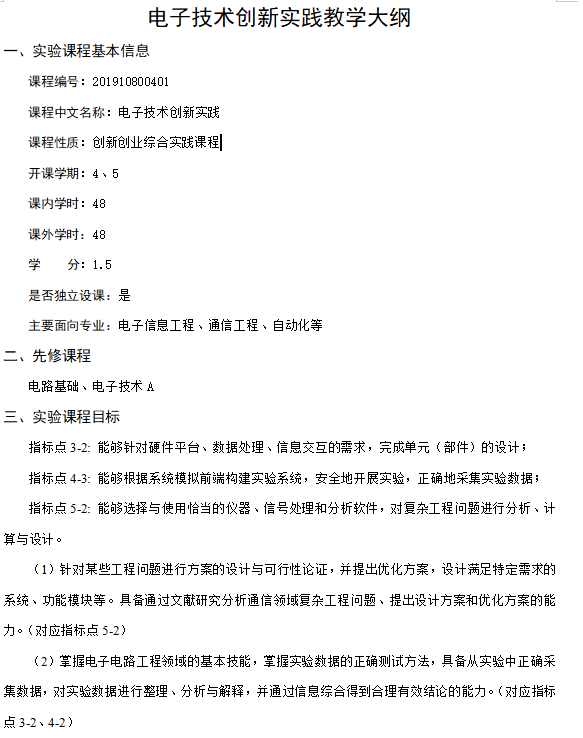

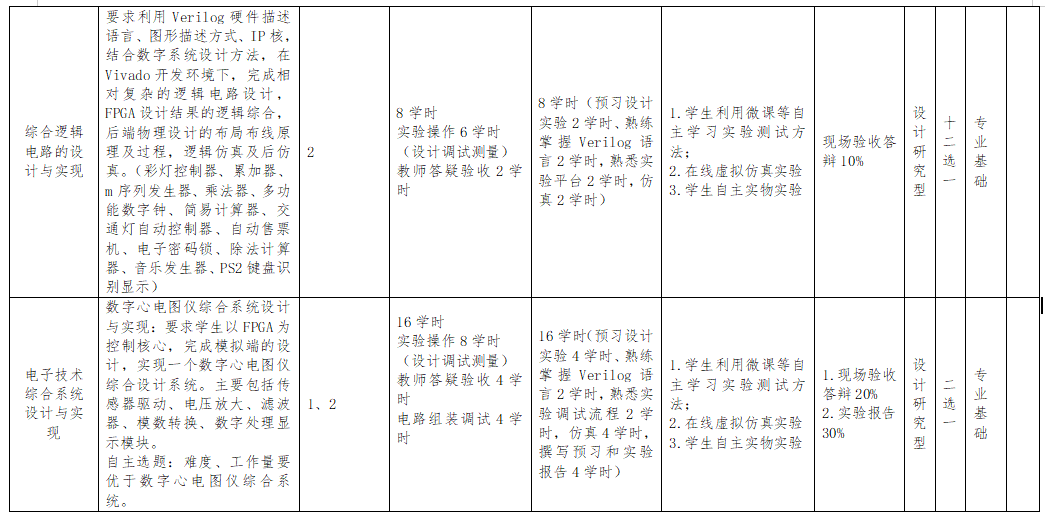

课程简要信息

课程名称:电子技术创新实践;

课程学时:课程共48学时(本项目8学时);

适用专业:电子信息工程、通信工程、自动化、测控、探测、电气、机器人、人工智能、光电等;

学生年级:课程大二下、大三上两学期(本项目发生在大二下学期);

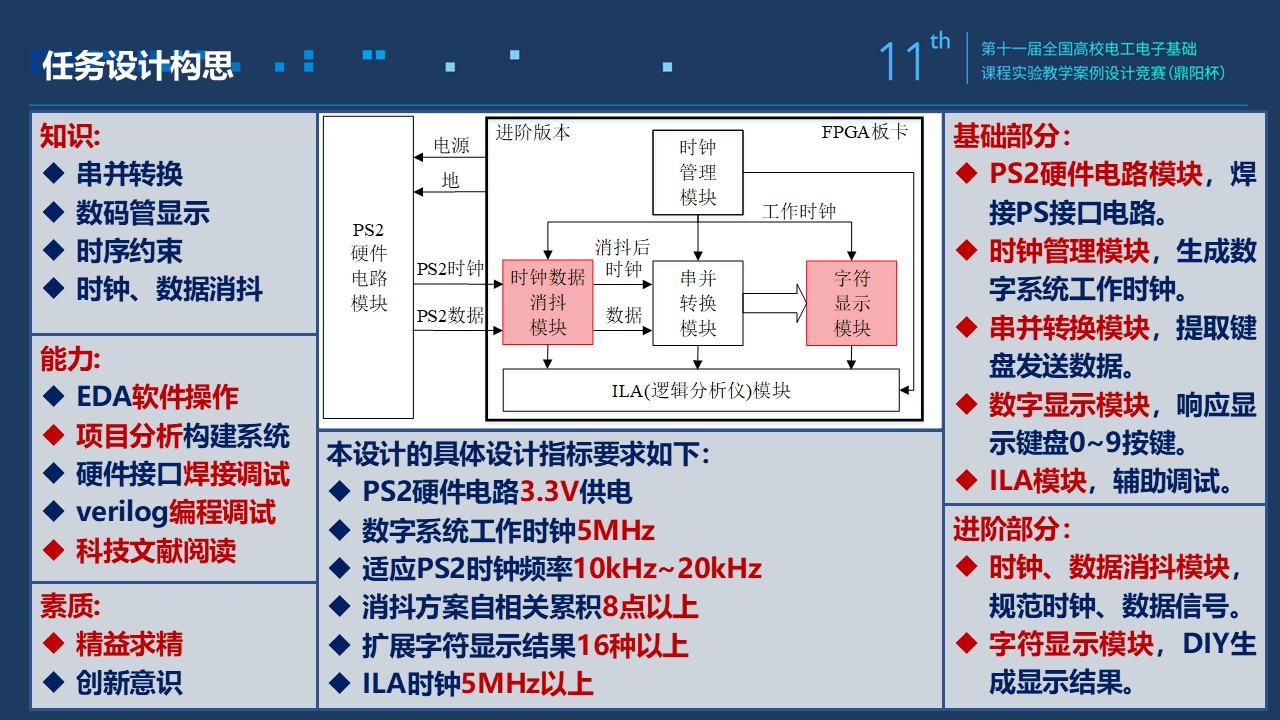

实验内容与任务

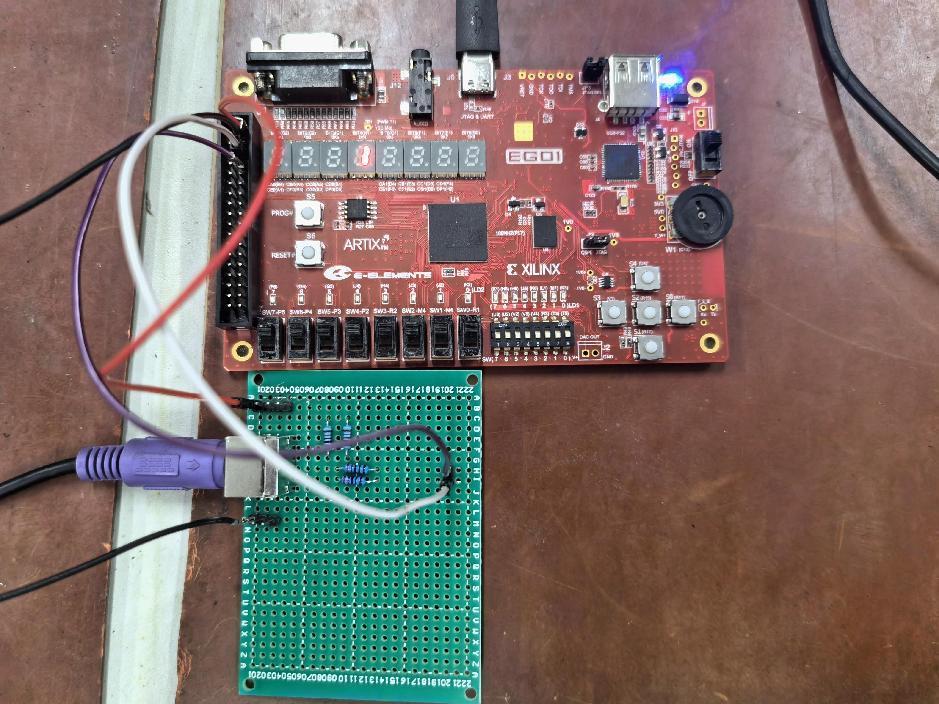

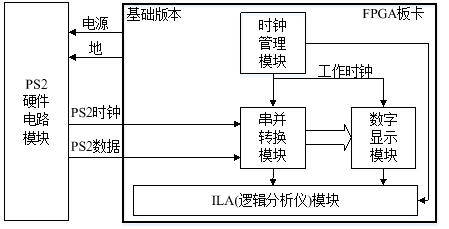

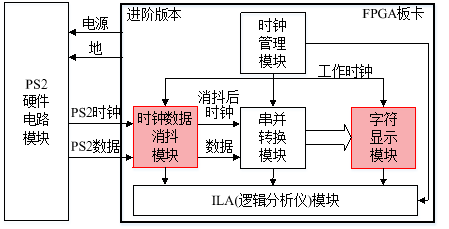

以FPGA口袋实验板(EGO1)为平台,设计一个能够识别PS2接口键盘键值电路,并在数码管上显示按键信息。

图1 PS2键盘识别系统结构框图

1)基础实验任务,焊接PS2接口电路,完成电路硬件连接。

2)基础实验任务,采用IP核调用方式,完成系统时钟频率变换。

3)基础实验任务,采用verilog硬件描述语言实现,设计串并转换模块,将PS2接口的同步串行数据转换成并行数据。

4)基础实验任务,采用verilog硬件描述语言实现,设计数字显示模块,解码PS2接口的8位数据,并将0~9数字按键的解码结果显示在数码管上。

5)进阶实验任务,采用ILA模块,辅助系统调试。

6)进阶实验任务,采用verilog硬件描述语言实现,在数码管上显示十六进制的数字、字母。

7)进阶实验任务,采用verilog硬件描述语言实现,同步系统时钟,提高系统稳定度。

8)进阶实验任务,采用verilog硬件描述语言实现,设计PS2同步时钟消抖电路模块,稳定PS2接口同步时钟,并提取时钟脉冲的下降沿。

本设计的具体设计指标要求如下:

1)PS2硬件电路3.3V供电

2)数字系统工作时钟5MHz

3)适应PS2时钟频率10kHz~20kHz

4)消抖方案自相关累积8点以上

5)扩展字符显示结果16种以上

6)ILA时钟5MHz以上

实验过程及要求

1)数字电路的实验是设计性的,学生课前完成设计,学习PS2通信协议,了解键盘电气特性和工作时序。

2)了解FPGA口袋实验板(EGO1)原理,依据实验板提供的100MHz系统时钟,完成分频模块设计。

3)依据FPGA芯片XC7A35T-1CSG324C的管脚资源进行合理的管脚分配,完成时序约束、管脚约束。

4)可以自行扩展,数码管实时显示自定义图形,消除抖动提高系统稳定性。

5)提出验收申请,演示实验成果,交流不同解决方案的特点。

相关知识及背景

键盘是重要输入工具,是实现人机交互的重要手段之一。标准PS2键盘技术成熟,价格低,可以在电子设计中用标准的PS2键盘取代扫描式矩阵式键盘。现在主流的PS2接口内嵌自动去除抖动的设计,自动地识别键的按下与释放,软硬件开发简便,价格便宜、稳定可靠,将PS2键盘作为嵌入式系统的输入设备实用、可行。

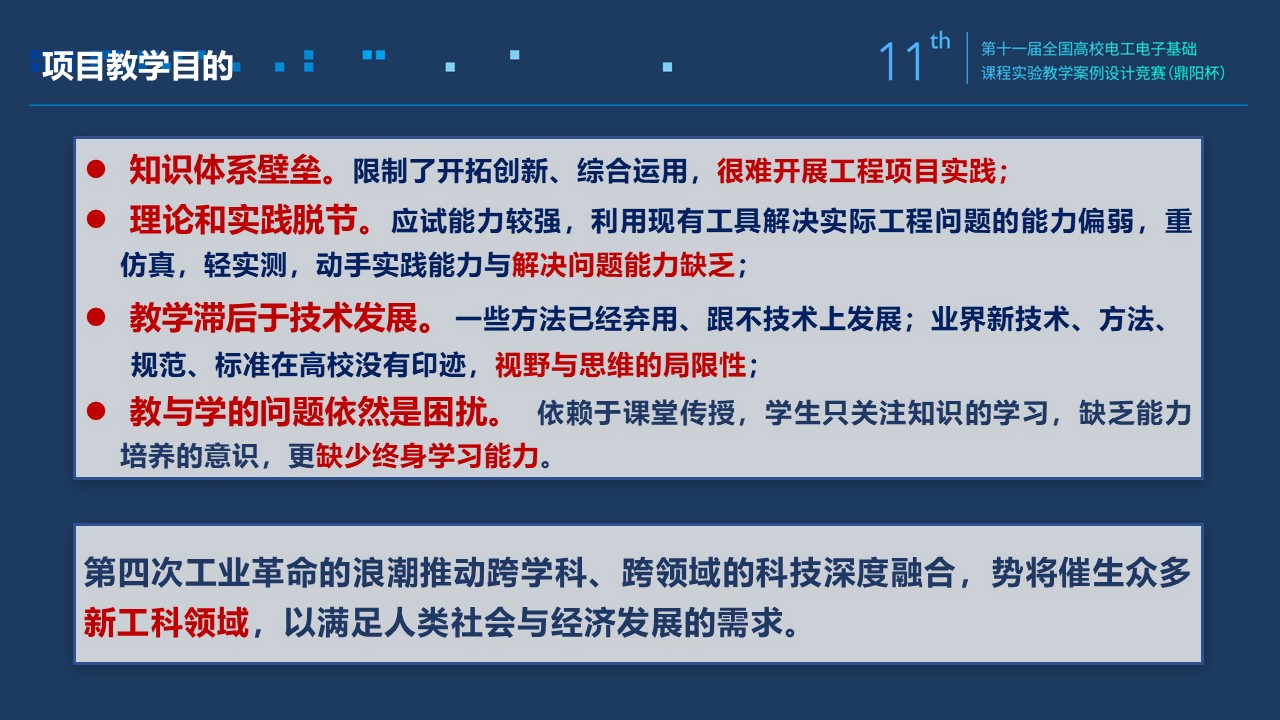

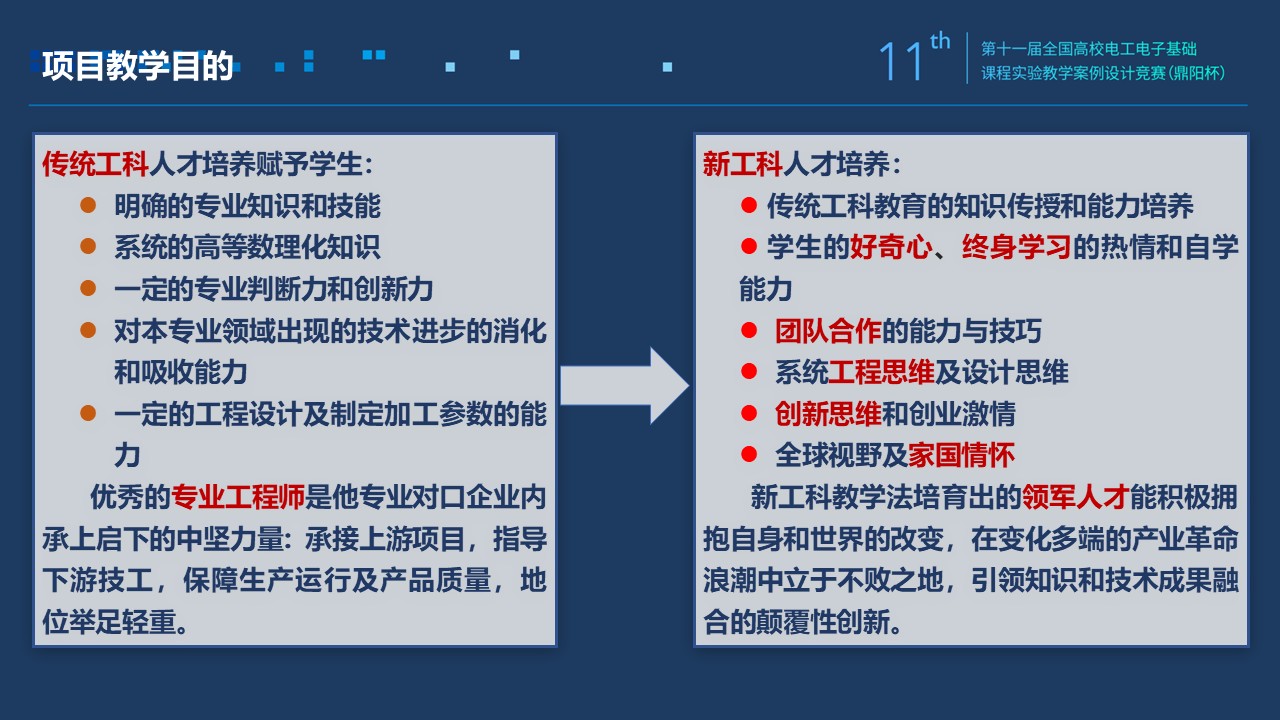

教学目标与目的

学习基于FPGA的数字电路设计以及Verilog HDL在PLD上的使用,学习阅读器件手册,掌握各种接口通信的工作时序控制。将数字电路基础实验和数字系统设计相结合,强调对未来工程技术人才的素质能力培养,针对工程问题进行方案的设计与可行性论证,并提出优化方案,设计满足特定需求的系统、功能模块等。培养具备通过文献研究分析通信领域复杂工程问题、提出设计方案和优化方案能力的工程技术人才。

教学设计与引导

本实验是一个比较完整的工程实践过程,需要经历学习研究、系统设计、整体调试、主观测试、总结报告等阶段。在实验教学中,在以下几个方面加强对学生的引导:

1) 学习数字电路设计的基本方法,学习Verilog HDL语言,了解硬件描述语言在数字系统设计方面的优势;

2)了解FPGA设计特点,了解各种接口的通信协议及如何用FPGA驱动各类接口,要求学生查找器件手册,了解PS2工作时序;

3)在系统设计、搭试、调试完成后,可以直观的体验设计结果,根据实际效果对系统进行优化;

4)实验过程中随时指导,设置指导教师提问环节,既是为了考核也是为了引导,促进学生思考和对实验内容的把握;

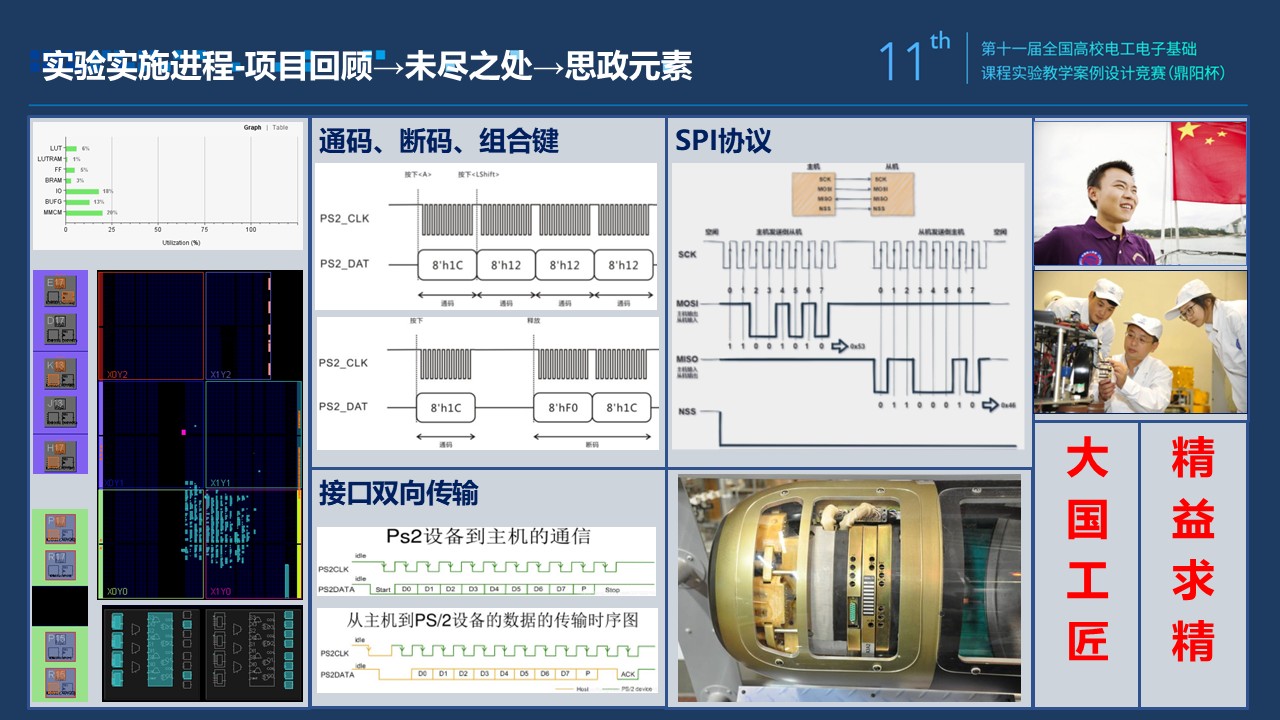

5)在实验完成后,回顾项目设计过程,展望项目改进思路,联系项目工程应用。

实验原理及方案

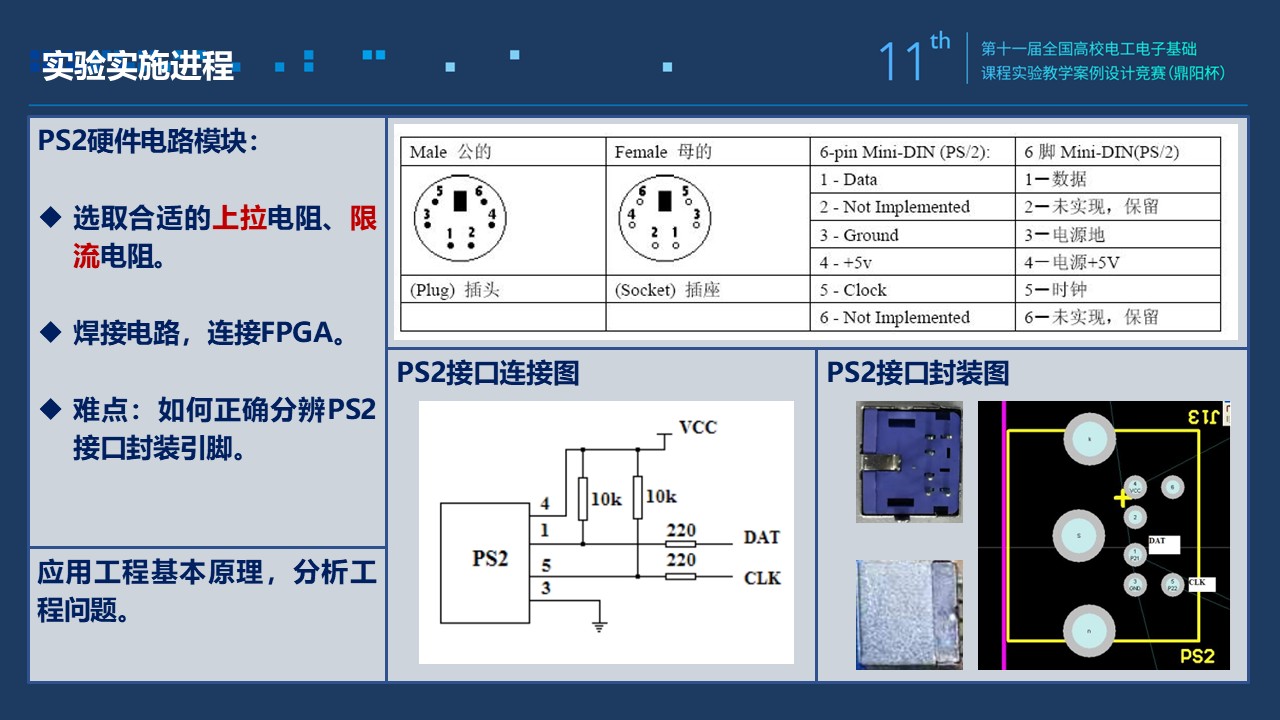

1)PS2硬件电路模块

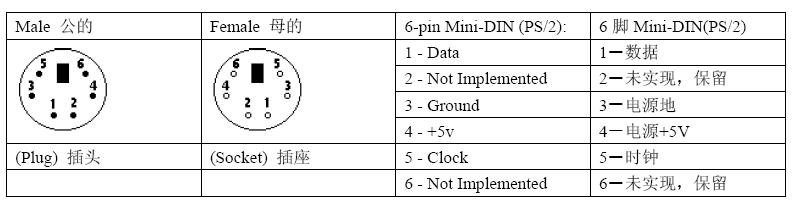

现在主流的PS2接口,具有六脚mini-DIN连接器。PS2 最初由IBM开发,它的连接端口只有四个脚有意义。分别是第1脚DATA(数据脚)、第3脚Ground(电源地)、第4脚+5V(电源脚)和第5脚Clock(时钟脚)。

图2 PS2接口引脚图

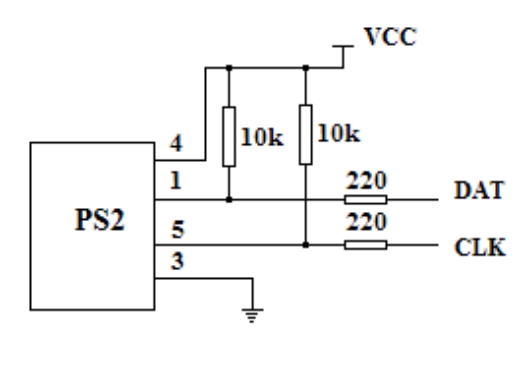

PS2键盘靠PC的PS2端口提供+5V电源,由于Clock和DATA两个脚都是集电极开路的,则必须接上拉电阻。 主从设备之间的数据通信采用双向同步方式传输,时钟信号由PC产生。它们平时一般保持高电平,有输出时才会被拉到低电平,之后会自动上浮到高电平。(即置“0”就把线拉低,置“1”就把线上浮成高电平)。

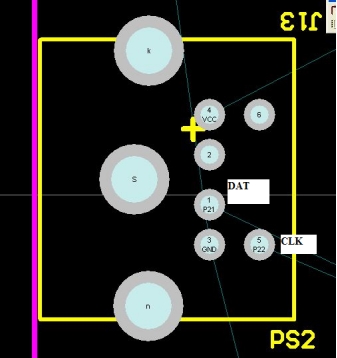

图3 PS2接口原理、封装图

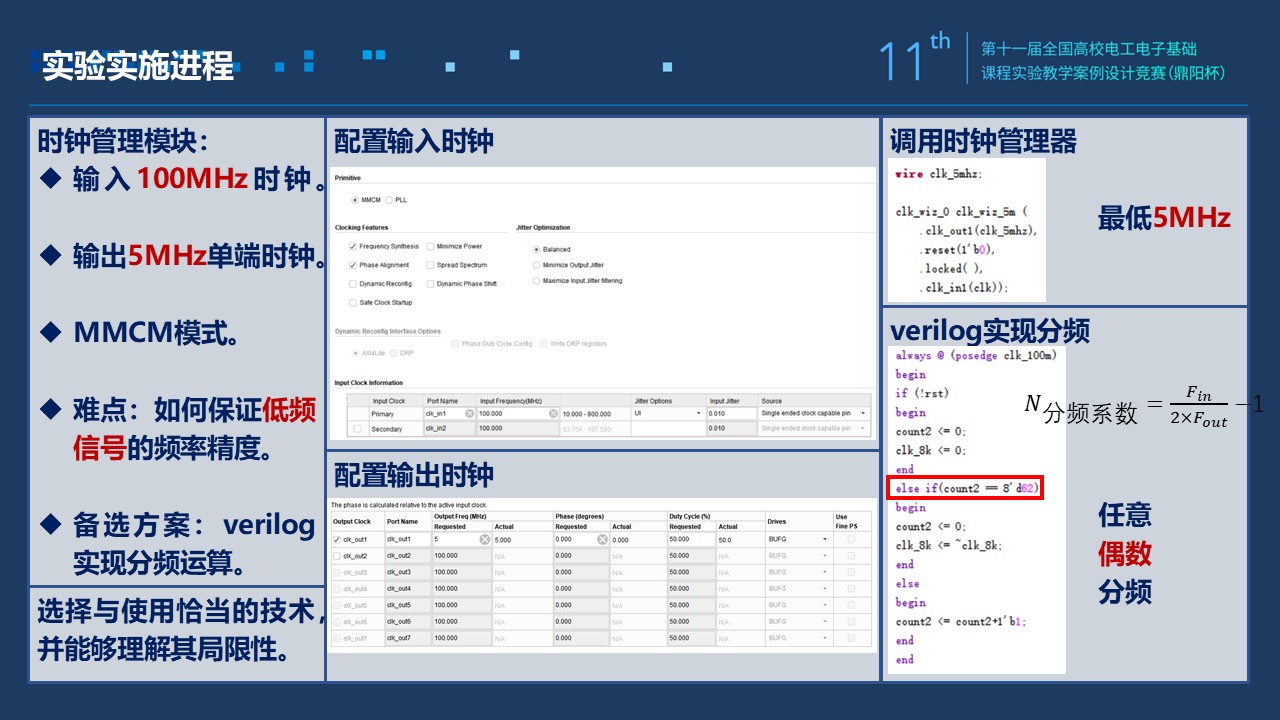

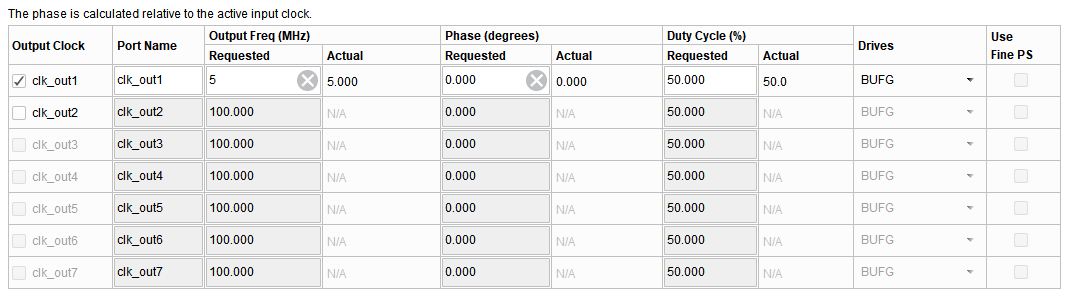

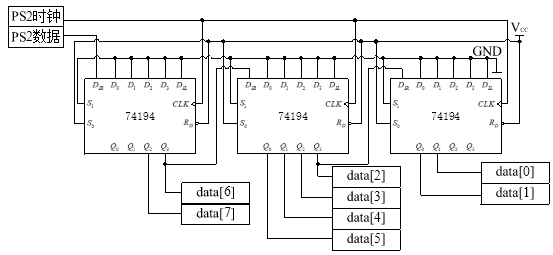

2)时钟管理模块

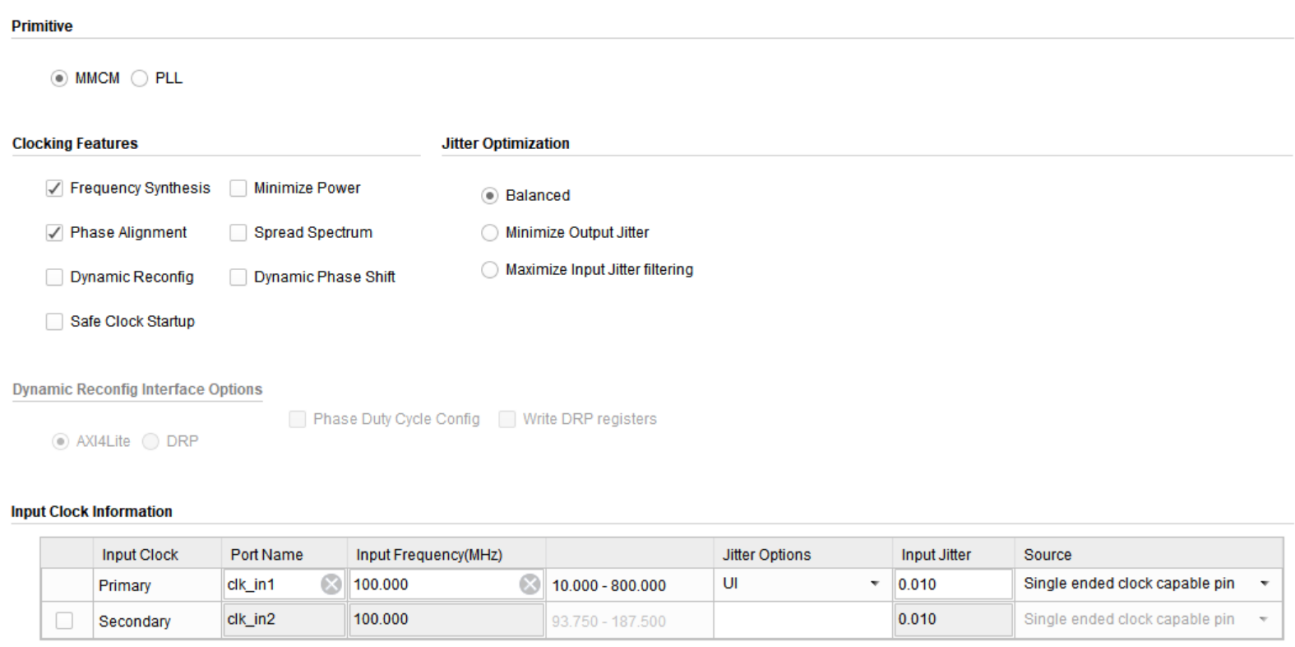

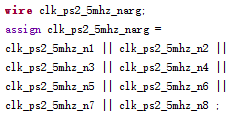

将FPGA板上100MHz输入时钟,转化为5MHz单端时钟,作为软件程序的系统时钟。时钟管理器配置方式、调用代码如下图所示。

图4 时钟管理器配置方案、调用代码

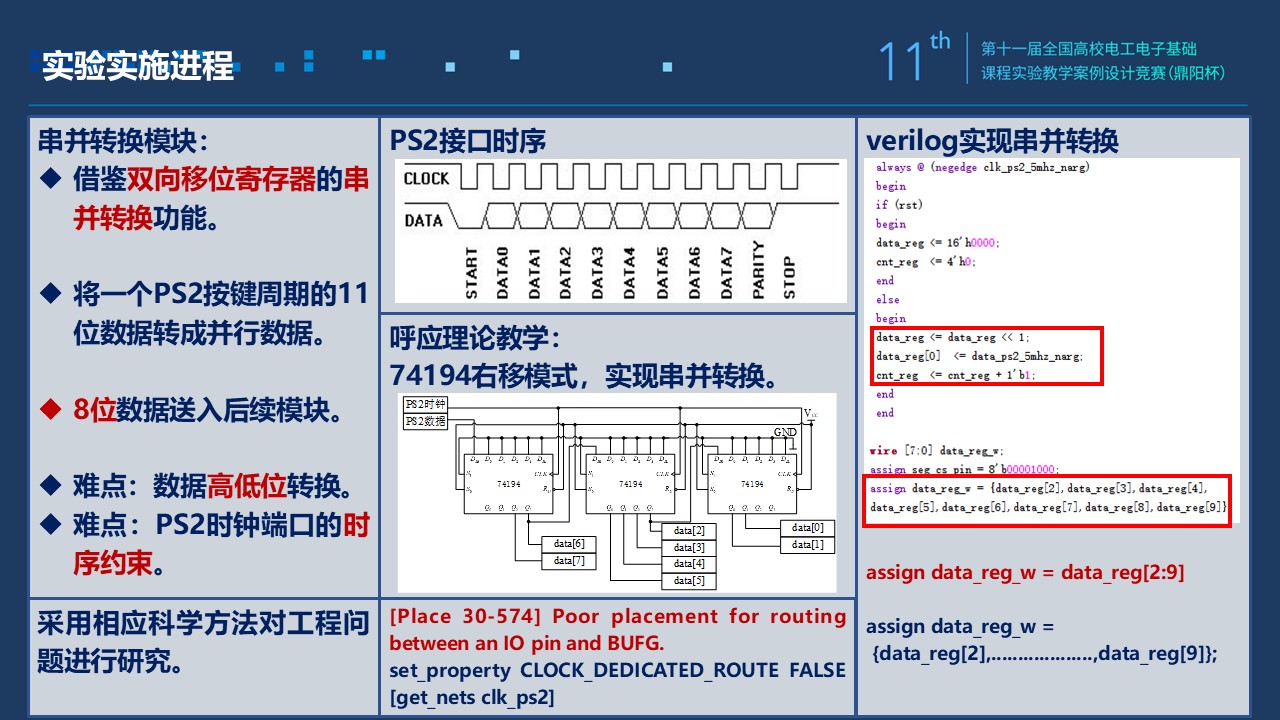

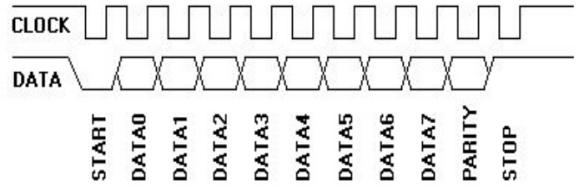

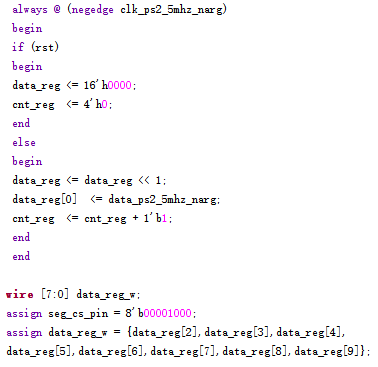

3)串并转换模块

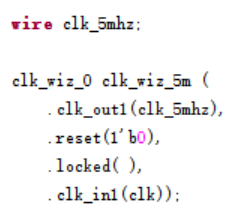

PS2键盘通信协议是一种双向同步串行协议。时钟线上每发生一个脉冲,数据线上发送一位数据,PS2键盘可以发送数据到主机,而主机也可以发送数据到设备,但主机有优先权,因此它只需把时钟拉低就可抑制在任何时候来自于键盘的通讯。

从键盘发送到主机的数据在时钟信号的下降沿被读取;不论通信的方向,键盘总是产生时钟信号,最大的时钟频率是33kHz, 而且大多数设备工作在10 ~20kHz。

PS2接口共有6个端口,需要FPGA控制的有一个时钟端口clock和一个数据端口data。根据PS2协议,其传输的数据格式有1个起始位,8个数据位,1个奇偶校验位,1个停止位,1个应答位。PS2从机发送一个完整数据包的时序图如下所示:

图5 PS2键盘发送数据时序

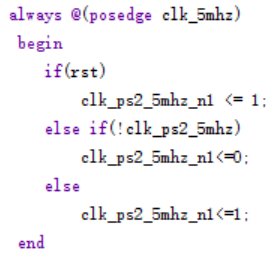

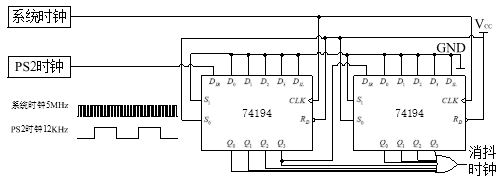

PS2协议和UART通信协议非常相似,键盘按照这个协议发送数据,FPGA作为主机,只需要正确的实现该协议的解码,将其中的8位数据位读取出来即可。由上图可知,数据在时钟的下降沿处是稳定的,因此只需要捕获时钟信号的下降沿,并在检测到这个下降沿时去读取数据线上的电平,就能够正确的读到数据。在PS2协议中,包含了从机到主机和主机到从机的通信时序,只是在进行PS2键盘的解码时,可以不需要进行主机到从机的通信。引导同学利用理论课上学习的双向移位寄存器74194完成以上逻辑模型设计,再用硬件描述语言完成程序编写。

图6 串并转换模块实现方案、程序代码

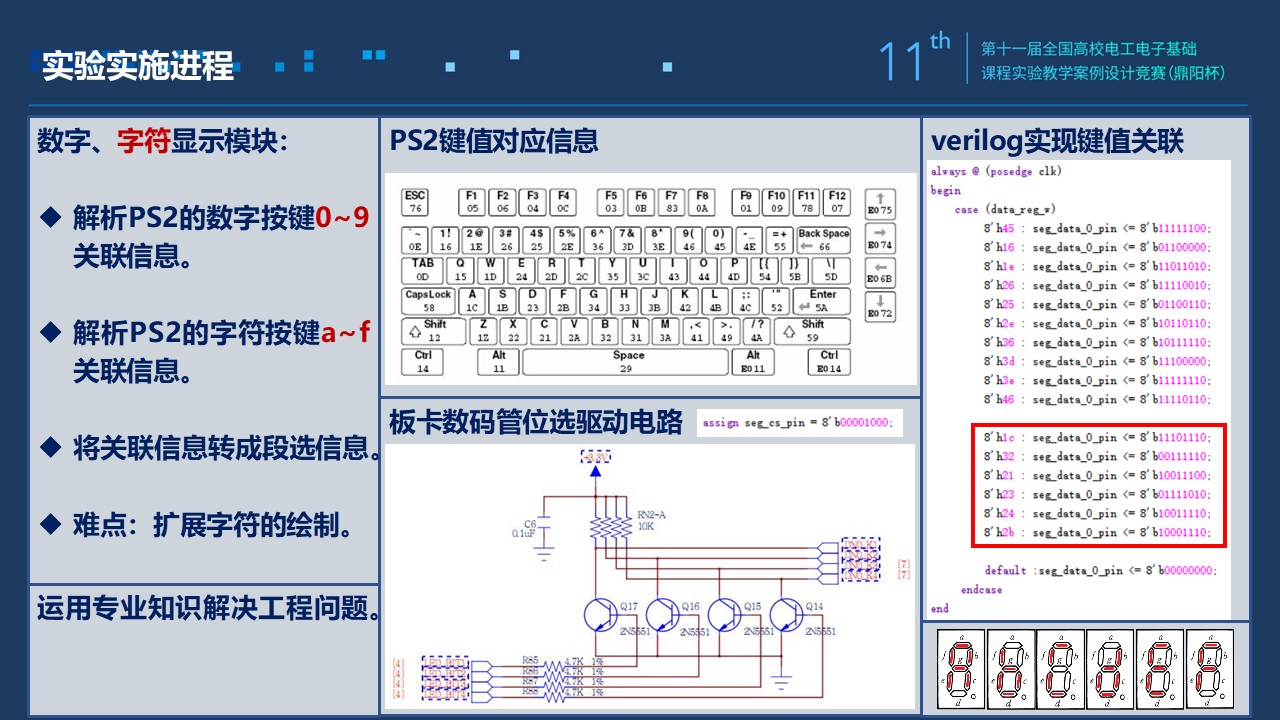

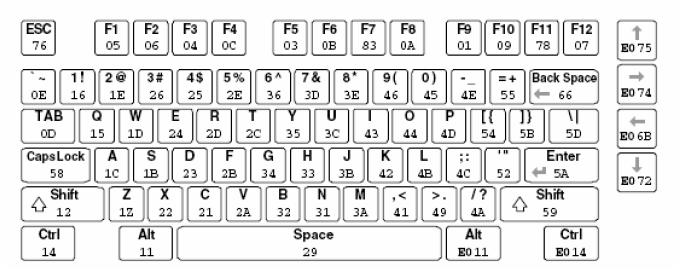

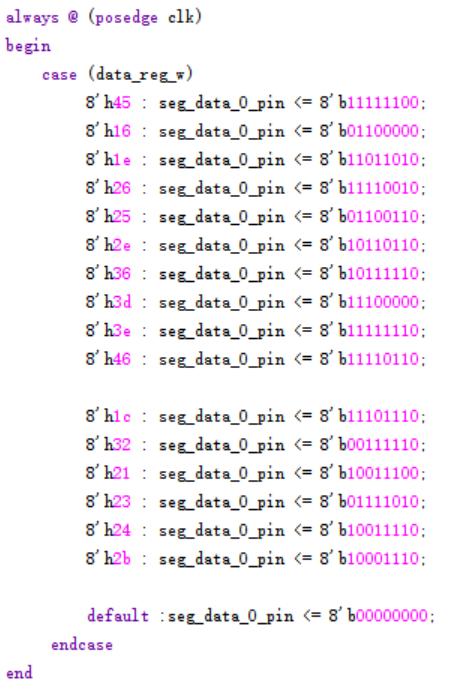

4)数字、字符显示模块:

解析PS2的数字按键0~9、a~f关联信息,将关联信息转成段选信息。

图7 PS2的数字按键关联信息、程序代码

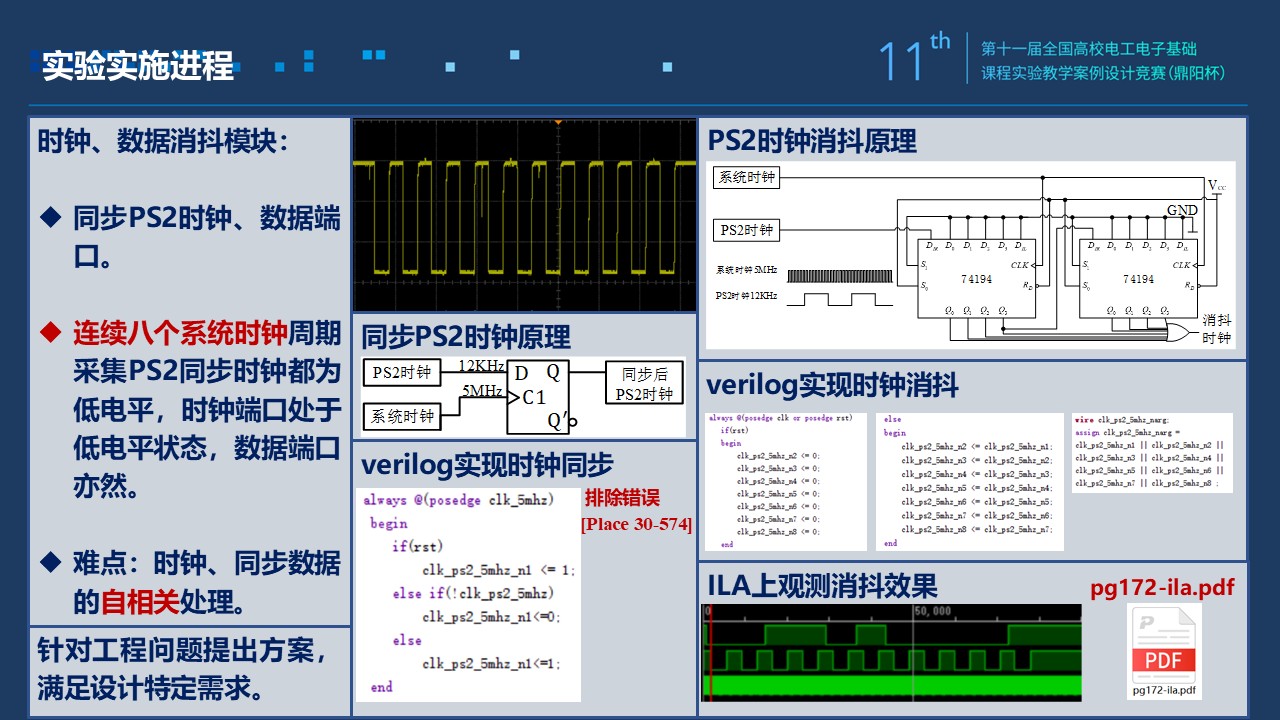

5)时钟、数据消抖模块

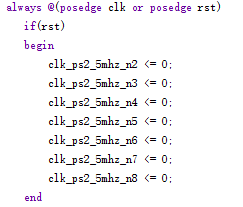

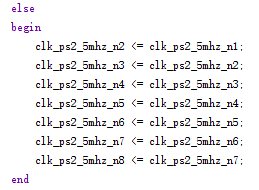

同步时钟消抖模块,利用频率较高的系统时钟扫描频率较低的PS2同步时钟。连续八个系统时钟周期采集PS2同步时钟都为低电平,才认为PS2时钟端口处于低电平状态,同理可判断PS2数据端口的低电平状态。

图8 PS2时钟同步转换、程序代码

图9 PS2时钟消抖、程序代码

教学实施进程

每次实验有三个环节,核算为8学时。首先是前导课,重点介绍每次实验(还有其他多个选题)的内容、要求等。其次是实验设计、预习课,学生可以进入实验室,调试验证自己的设计。因为本实验需要实验箱等硬件支持,学生需要在实验室完成。最后一个环节是验收,学生现场下载自己的设计工程,并进行功能演示,回答指导老师提出的各种问题,完成验收。

考核要求与方法

1)实物验收:功能与性能指标的完成程度,完成速度等;

2)实验质量:设计方案的合理性,代码的优化等;

3)自主创新:功能构思、电路设计的创新性,回答指导教师提出的相关设计问题,以此考查自主思考与独立实践能力;

4)实验数据:显示结果和现场演示效果;

表1 实验评分选项

| 序号 | 评 分 项 目 | 分值 |

| 1 | 研讨方案 | 10 |

| 2 | 软、硬件平台使用、调试及故障排查能力 | 30 |

| 3 | 任务功能完成情况及创新拓展 | 40 |

| 4 | 回答指导教师提出的问题 | 20 |

| 操 作 成 绩 | 100 | |

注:实验操作成绩根据学生现场操作情况给出

项目特色或创新

项目的特色在于:

1)呼应理论教学:理论知识活学活用,使学生在学习过程中主动发现问题,应用所学知识解决问题,使课堂学习的过程不再局限于获取知识,而是变为全面发展综合素质与能力的过程。

2)难度分级:内容可以分模块、分不同难度级别完成。允许学生完成部分功能,适应分级教学,不强求一致,也不至于让学生因难以完成整个任务而感觉挫败,或拿不到分数,使各个能力水平的学生都有收获。

3)经验可复制:中规模集成器件、图形法、语言法均可实现,适用于各类型院校的数字实验开展。

4)贴近工程实践:针对协议、接口展开项目,尝试新技术、新方法,信号看得见、设备摸得着,学生认同感强。

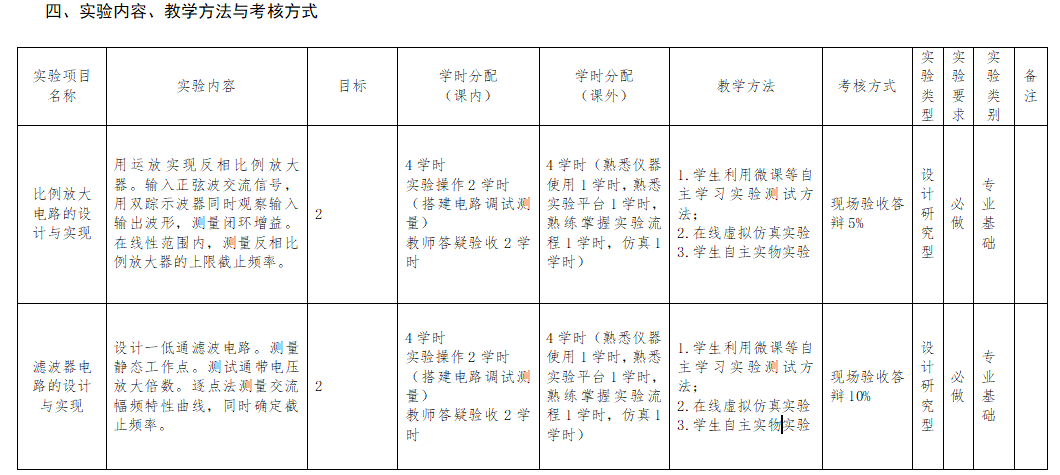

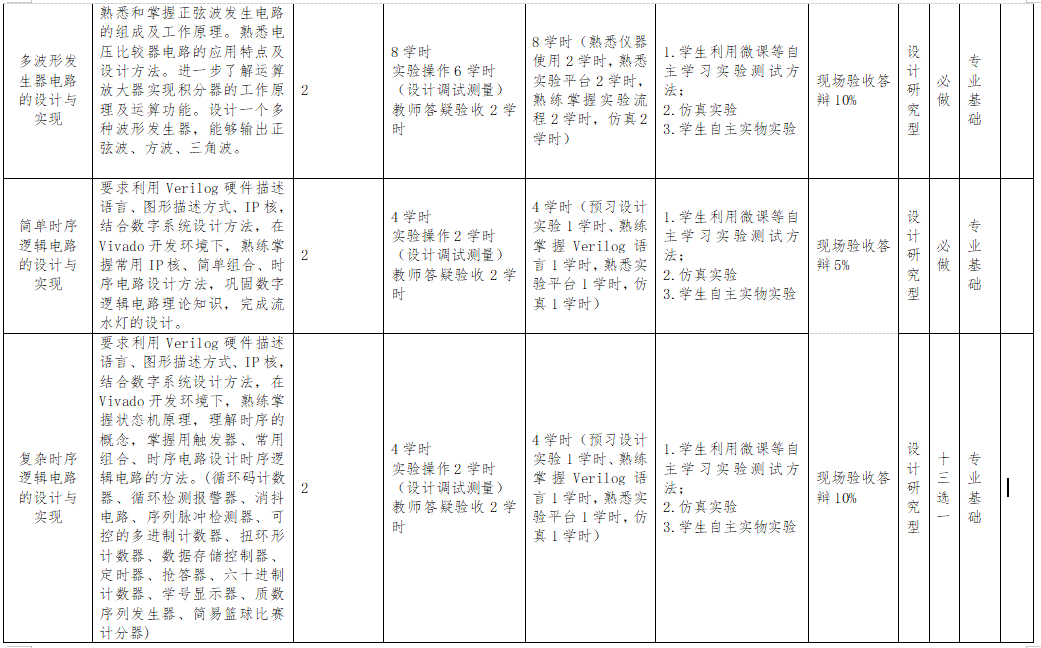

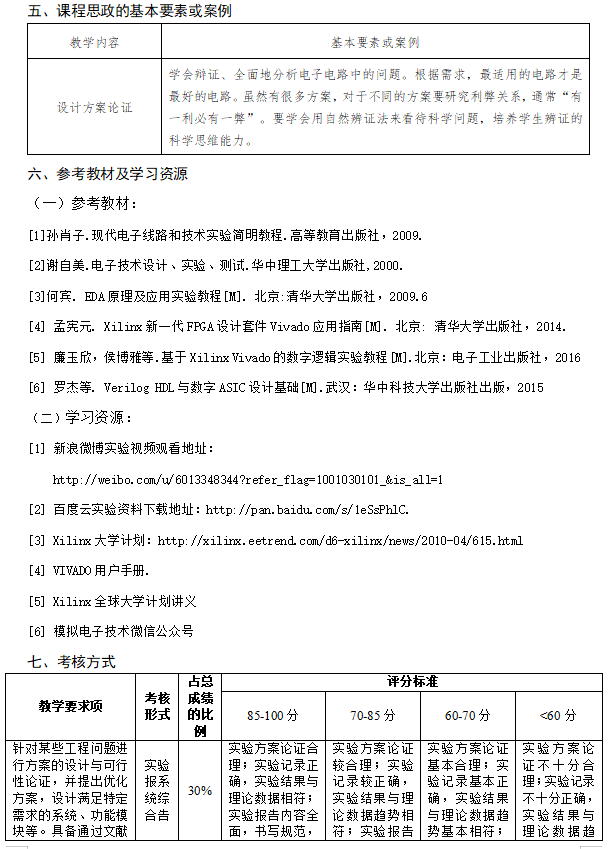

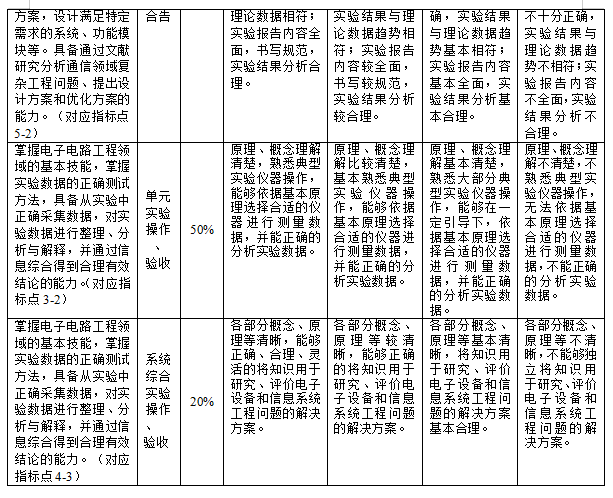

附录A:电子技术创新实践教学大纲

附录B:电路实物、学生评价