加法器的HDL设计和性能比较

实验题目:加法器的 HDL 设计和性能比较

1. 课程简要信息

课程名称:《数字逻辑电路》;课程学时:64学时;适用专业:电气信息类;学生年级:本科二年级。

2. 实验内容与任务(限 500 字)

1) 用HDL设计一位及多位加法器的不同电路结构;

2) 用门级建模、数据流建模和行为建模三种方式来描述组合逻辑电路模块;

3) 将多个模块组合起来对一个设计进行分级描述;

4) 在 $2 8 \mathrm { n m } \mathrm { C M O S }$ 工艺下,分析上述不同加法器的面积、速度、功耗参数;

5) 分析上述性能参数,并了解近似加法器的思想;

6) 选择一种近似加法器,用HDL进行描述并仿真上述的参数;

7) 分析 ITRS 提出的各设计参数对数字设计的影响;

8) 如有余力,把近似加法器应用到 DCT/IDCT中,并分析重建图像的质量和所消耗的资源。

3. 实验过程及要求(限 300 字)

1) 熟悉RCA、CLA 加法电路结构;

2) 熟悉仿真软件;

3) 用 HDL 语言描述 RCA 和 CLA;

4) 用自底向上和自顶向下两种方法进行分级描述;

5) 写testbench并测试电路的功能;

6) 比较综合后的面积、速度、功耗参数;

7) 用HDL语言描述 LOA电路;并重复第六步的过程。

8) 结合仿真结果,分析RCA和CLA 各自的面积速度优势;并分析 LOA 如何在性能上取得各

个参数之间的权衡。

9)提高部分:读入标准测试图像,用 HDL 语言进行 DCT/IDCT,其中加法器部分采用 LOA。

分析重建图像的质量,并列表比较 FPGA 资源使用情况。

4. 相关知识及背景(限 150 字)

熟练掌握和灵活运用硬件描述语言是数字电路课程的重点内容之一。HDL描述的数字电路可使用例如CMOS 工艺来实现硬件应用(ASIC 和 FPGA)。国际半导体技术路线图(ITRS)提出衡量数字设计的参数包括面积、速度、功耗和可靠性。本案例在组合电路的 HDL教学中,讲解数字设计中除了功能之外,其它参数的比较。

5. 教学目标与目的(限 100 字)

掌握组合电路模块的门级建模、数据流建模和行为建模三种方式。了解数字设计除了功能之外的其它参数之间的权衡。遵守基于工业惯例的用法去写电路模型,确保行为描述能有效被综合成物理硬件。

6. 教学设计与引导

本实验的过程是一个比较完整的探索研究过程,需要经历学习研究、资料查找、方案论证、仿真设计、参数比较、数据分析、设计总结等过程。在实验教学中,应在以下几个方面加强对学生的引导:

1)学生自主查找资料,学习近似加法器的知识;提示并引导学生,循序渐进理解各种精确加法器和近似加法器的异同。

2) 强调数字设计除了功能性之外,还需要兼顾其他设计参数,好的数字设计都必须在各个参数之间找到好的权衡。

3) 建议仿真时有效利用仿真软件功能,在分析仿真结果时,要学会理论联系实践,从宏观上大致判断仿真结果的合理性。

4) 不拘泥于教材和课堂,可以自己尝试设计可能综合性能更佳的加法器。

5) 注重讨论交流,但又必须独立思考。实验完成后,组织学生答辩,展示优秀作品。

7. 实验原理及方案

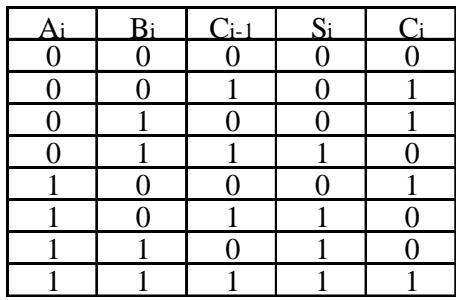

对于精确加法器而言,一般教材分为半加器和全加器考虑。半加器是指只考虑两个加数相加,不考虑低位向本位的进位,所以仅用半加器不能解决加法问题。全加器不仅考虑两个加数本位的相加,而且考虑低位到本位的进位。用 $A _ { i }$ 和 $B _ { i }$ 分别代表被加数和加数的第 $i$ 位, $C _ { i - 1 }$ 代表低位向本位的进位。本位的被加数 $A _ { i }$ 、加数 $B _ { i }$ 和低位向本位的进位 $C _ { i - 1 }$ 这三个变量的和用 $S _ { i }$ 表示,本位向高位的进位用 $C _ { i }$ 表示。全加器的真值表及其逻辑电路如图 7.1 所示。

图 7. 1 全加器真值表及其逻辑图

由真值表可以写出 $S _ { i }$ 和 $C _ { i }$ 的逻辑表达式:

$$ S _ { i } = \Bigr ( \overline { { A _ { i } } } \overline { { B _ { i } } } + A _ { i } B _ { i } \Bigr ) C _ { i - 1 } + \Bigr ( A _ { i } \overline { { B _ { i } } } + \overline { { A _ { i } } } B _ { i } \Bigr ) \overline { { C _ { i - 1 } } } $$

代 入式( 7 - 1 )可 得 $S _ { i } = S \oplus C _ { i - 1 } = A _ { i } \oplus B _ { i } \oplus C _ { i - 1 }$

$$ C _ { i } = \Big ( \overline { { A _ { i } } } B _ { i } + A _ { i } \overline { { B _ { i } } } \Big ) C _ { i - 1 } + A _ { i } B _ { i } $$

实际全加器的电路结构可以有多种不同的形式,它们都是通过变换 $S _ { i }$ 和 $C _ { i }$ 的逻辑表达式所得到。

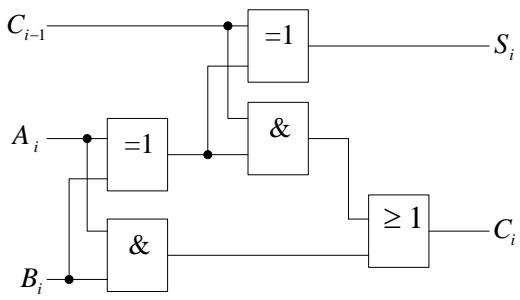

在一些要求高速运算的场合,常常采用超前进位加法器。所谓超前进位,是指通过逻辑电路提前得出加到每一位全加器上的进位输入信号,而无需从最低位开始逐位传递进位信号。根据全加器的进位逻辑表达式(式(7-3)),

$$ \begin{array} { r l } & { C _ { i } = \bigg ( \overline { { A } } _ { i } B _ { i } + A _ { i } \overline { { B _ { i } } } \bigg ) C _ { i - 1 } + A _ { i } B _ { i } = \overline { { A } } _ { i } B _ { i } C _ { i - 1 } + A _ { i } \overline { { B _ { i } } } C _ { i - 1 } + A _ { i } B _ { i } \overline { { C _ { i - 1 } } } + A _ { i } B _ { i } C _ { i - 1 } } \ & { \quad = A _ { i } B _ { i } + \big ( A _ { i } \oplus B _ { i } \big ) C _ { i - 1 } } \end{array} $$

令: $G _ { \scriptscriptstyle i } = A _ { \scriptscriptstyle i } B _ { \scriptscriptstyle i }$ 为进位产生项, $P _ { i } = A _ { i } \oplus B _ { i }$ 为进位传递项

则 $C _ { i }$ 的表达式可以写成

C G PC i i i i 1 , 其 中 1 i 4

$S _ { i }$ 的表达式可以写成

$$ S _ { i } = \Big ( \overline { { A _ { i } B _ { i } } } + A _ { i } B _ { i } \Big ) C _ { i - 1 } + \Big ( A _ { i } \overline { { B _ { i } } } + \overline { { A _ { i } } } B _ { i } \Big ) \overline { { C _ { i - 1 } } } = P _ { i } \oplus C _ { i - 1 } $$

如果实现 4 位超前进位加法器,则各位(第 1 到第 4 位)的进位表达式为

$$ \begin{array} { l } { C _ { 1 } = G _ { 1 } + P _ { 1 } C _ { 0 } = G _ { 1 } + P _ { 1 } C _ { i n } } \ { C _ { 2 } = G _ { 2 } + P _ { 2 } C _ { 1 } = G _ { 2 } + P _ { 2 } G _ { 1 } + P _ { 2 } P _ { 1 } C _ { i n } } \ { C _ { 3 } = G _ { 3 } + P _ { 3 } C _ { 2 } = G _ { 3 } + P _ { 3 } G _ { 2 } + P _ { 3 } P _ { 2 } G _ { 1 } + P _ { 3 } P _ { 2 } P _ { 1 } C _ { i n } } \ { C _ { 4 } = G _ { 4 } + P _ { 4 } C _ { 3 } = G _ { 4 } + P _ { 4 } G _ { 3 } + P _ { 4 } P _ { 3 } G _ { 2 } + P _ { 4 } P _ { 3 } P _ { 2 } G _ { 1 } + P _ { 4 } P _ { 3 } P _ { 2 } P _ { 1 } C _ { i n } } \end{array} $$

各位的输出表达式为

$$ \begin{array} { r l } & { S _ { 1 } = P _ { 1 } \oplus C _ { i n } } \ & { S _ { 2 } = P _ { 2 } \oplus C _ { 1 } } \ & { S _ { 3 } = P _ { 3 } \oplus C _ { 2 } } \ & { S _ { 4 } = P _ { 4 } \oplus C _ { 3 } } \ & { S _ { 5 } = C _ { 4 } } \end{array} $$

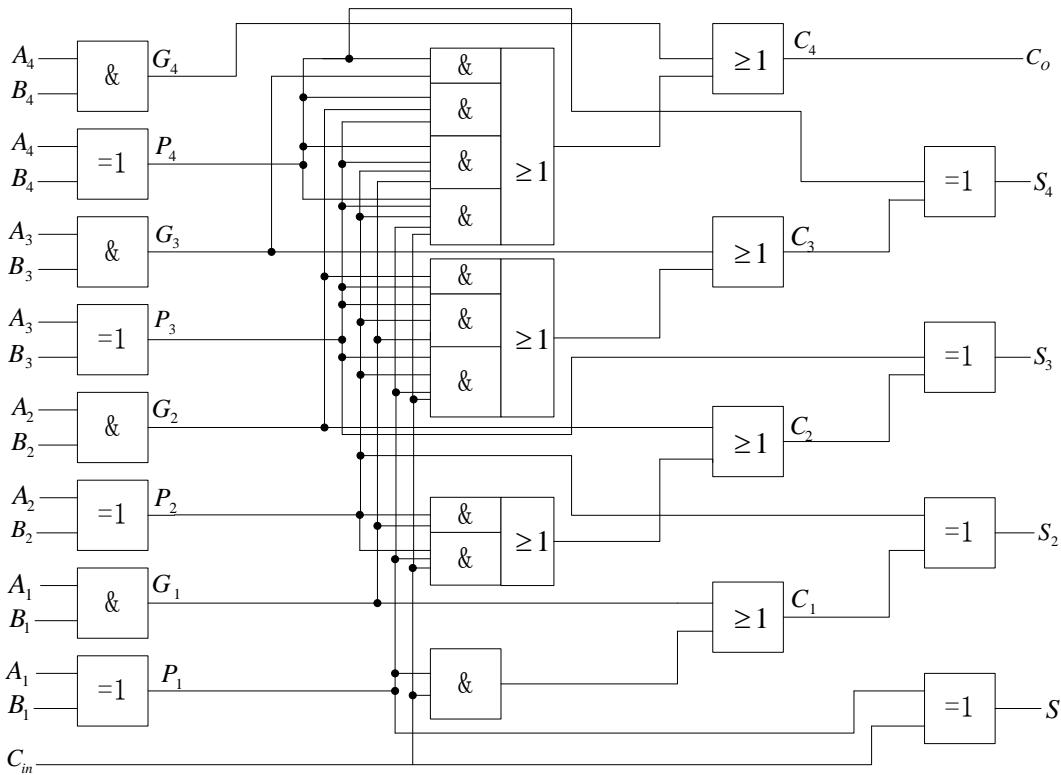

由此可见,进位信号均可以表示成 $P _ { i }$ 和 $G _ { i }$ 的函数。这样进位信号就能提前得到,所以多位数相加时,多个全加器可以同时工作,缩短了电路的传输延迟时间。四位超前进位加法器的逻辑电路图如图 7.2 所示。

图 7. 2 四位超前进位加法器的逻辑电路图

实验首先实现 RCA 和 CLA 这两种加法器,并了解 CLA 如何用面积换速度以及 ITRS 所提出的各个参数权衡的思想。

然而常规精确加法器为了得到精确的结果需要较长的时间延迟,而且功率消耗较大。随着移动计算机处理技术的普及,信号处理、多媒体、机器学习和模式识别等应用的需求不断增加。这些应用程序有一个共同特点,它们可以容忍计算结果出现一部分错误。例如,由于人眼无法识别嵌入在图像中的少量错误,因此可以允许在图像处理应用中偶尔产生一个不正确的像素。降低这些应用程序的精度要求可能会扩大设计空间。例如,可以采用相比精确计算具有较小时间延迟和功耗的设计方案,即近似计算,它是指以牺牲少量精度为代价,来换取性能和功耗的改善。实验进而通过一种代表的近似加法器 LOA来了解近似加法器的原理和应用。学有余力的学生可通过一个DCT/IDCT 的实例进一步深入了解近似加法器的应用场合和优势。

8. 教学实施进程

本实验的过程是一个兼顾拓展性、综合验证型与设计型的实验,需要经历文献检索与学习、电路设计、仿真调试、数据分析、设计总结等过程。在实验教学中,应在以下几个方面加强对学生的引导:

1)注重理论联系实践。对于工程学科,除了学会解题之外,更要注重学习书本知识在实践中的应用。2)重点介绍仿真软件的使用方法。3)鼓励学生大胆表达思想。这个实验的提高部分是完全开放性的,所给出的近似加法器结构和应用均可不拘泥于所给例子。4)在实验完成后,撰写实验报告及项目总结PPT。组织学生以答辩、评讲的形式进行交流,了解不同解决方案及其具体电路不同的实际应用,拓宽知识面。

9. 实验报告要求

实验报告需要反映以下工作:

1) 实验目的

2) 理论分析

3) 设计过程

4) 综合电路

5) 仿真结果

6) 数据分析

7) 实验应用

8) 结果总结

10.考核要求与方法(限 300 字)

基本部分:

1) 能用三种方式来描述组合逻辑电路模块;

2) 能对一个不同加法器电路进行分级描述;

3) 能正确编写 testbench;

4) 能运用软件仿真加法器的功能;

5) 能运用软件分析加法器的面积、速度、功耗参数;

6) 能对上述性能参数进行分析,描述各参数对数字设计的影响;

7) 实验报告内容完整,数据翔实;

提高部分:

8)能写出一种或以上近似加法器结构并分析各性能参数;

9)能将近似加法器应用于一种或以上数字设计中并分析性能;

11.项目特色或创新(可空缺,限 150 字)

项目的特色在于:科研反哺教学。

在科研成为教师的重点工作方向的当下,从事专业基础课教学的老师,如何将科研和本科生教学结合,是一个值得探讨的话题。本实验案例源于指导教师的基础科研项目,旨在让强化班的学生了解科学研究的入门方法,让他们觉得科学研究是源于基础理论的,并不遥不可及。

实验案例信息表

| 案例提供单位 | 南京理工大学 | 相关专业 | 电气信息类 | |||

| 设计者姓名 | 班恬 | 电子邮箱 | tian.ban @ njust.edu.cn | |||

| 移动电话 | 13585174441 | 通讯地址(含邮编) | 南京理工大学电光学院 210094 | |||

| 设计者姓名 | 陆凯 | 电子邮箱 | 18936030337@189.cn | |||

| 移动电话 | 18936030337 | 通讯地址(含邮编) | 南京理工大学电光学院210094 | |||

| 设计者姓名 | 电子邮箱 | |||||

| 移动电话 | 通讯地址(含邮编) | |||||

| 相关课程名称 | 数字逻辑电路 | 学生年级 | 二年级 | 学时(课内+课外) | 4+4 | |

| 支撑条件 | 仪器设备 | XilinxVirtex5系列开发板 | ||||

| 软件工具 | Modelsim, Cadence RTL Compiler, ISE | |||||

| 主要器件 | Virtex-5 FPGA | |||||