基于FPGA的ADC动态性能测评系统设计与实现

实验题目:基于 FPGA 的 ADC 动态性能测评系统设计与实现

1. 课程简要信息

课程名称:电子器件基础

课程学时:40 学时

项目学时:8学时(课内),12学时(课外)

适用专业:电子科学与技术、微电子科学与工程

学生年级:大三-春季学期

2. 实验内容、任务及要求

综合运用课程所讲授的模数转换器(Analog-to-Digital Converter, ADC)的基本原理、性能参数等相关理论知识,设计一款基于FPGA的ADC性能测量与分析系统,能够有效标定ADC的性能指标。具体包括,基于指定的器件型号(AD9226)设计ADC单元电路,通过高速并口与FPGA(XC6SLX16)核心板互连,基于FPGA编写ADC的驱动和数据缓存代码,通过数据在线分析套件 Chipscope 实时抓取 ADC 输出数据,并导入ADC性能分析软件WaveVision完成性能测量。通过本课程实验学习完成从前修课程《模拟电子技术》和《数字电子技术》的理论知识到工程实践的能力进阶。

1. 基本任务要求(4 课内学时 $\pm 4$ 课外学时):

基本要求针对所有学生,

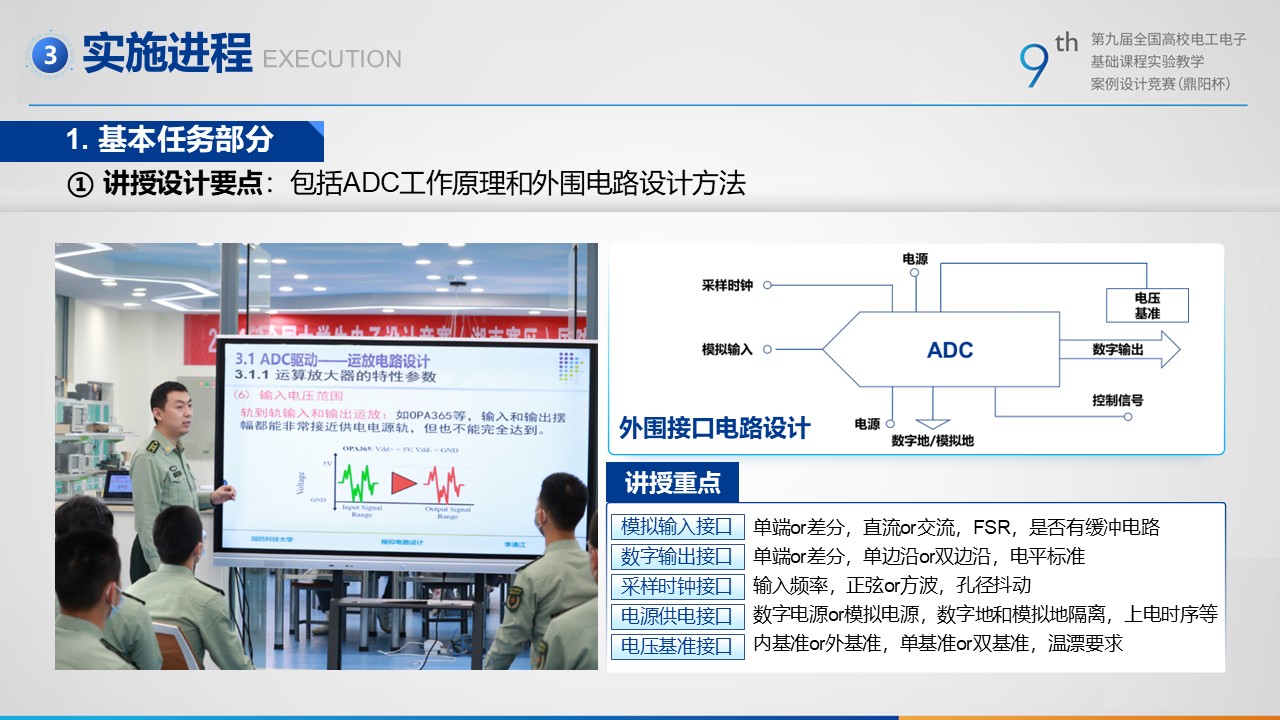

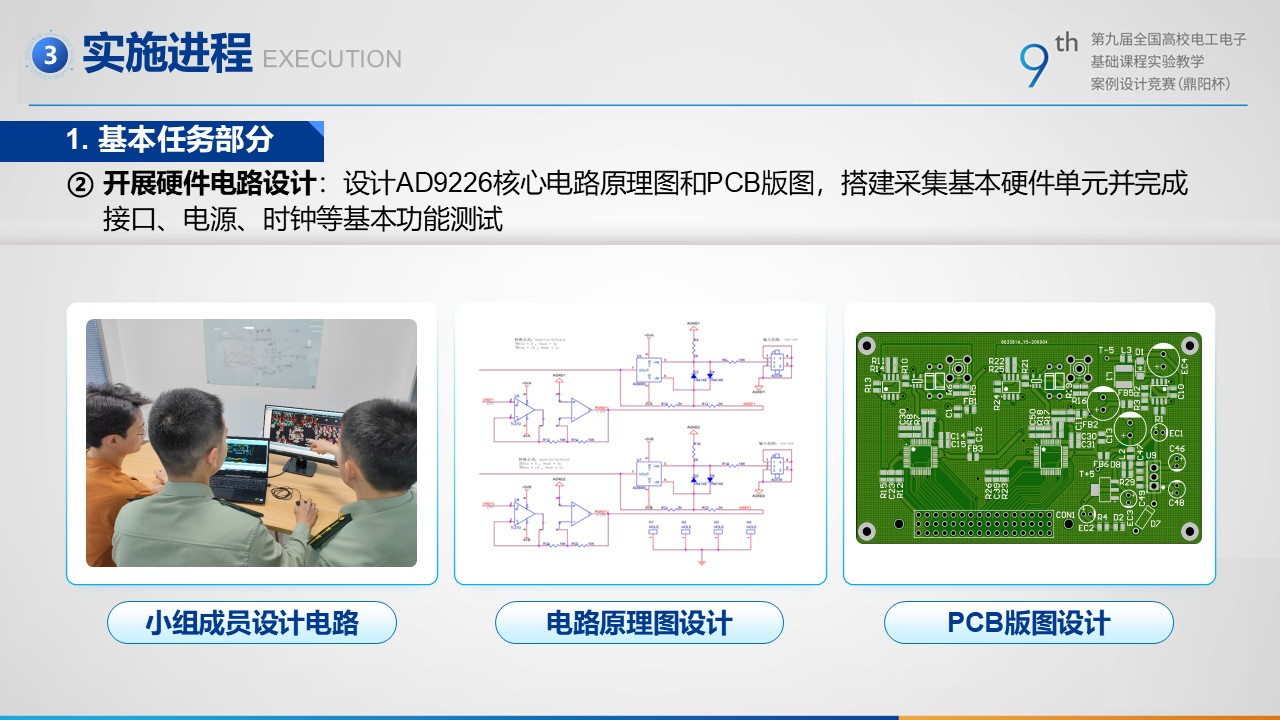

1)掌握ADC工作原理和外围电路设计方法。设计AD9226核心电路原理图和PCB版图,搭建采集基本硬件单元并完成接口、电源、时钟等基本功能测试。

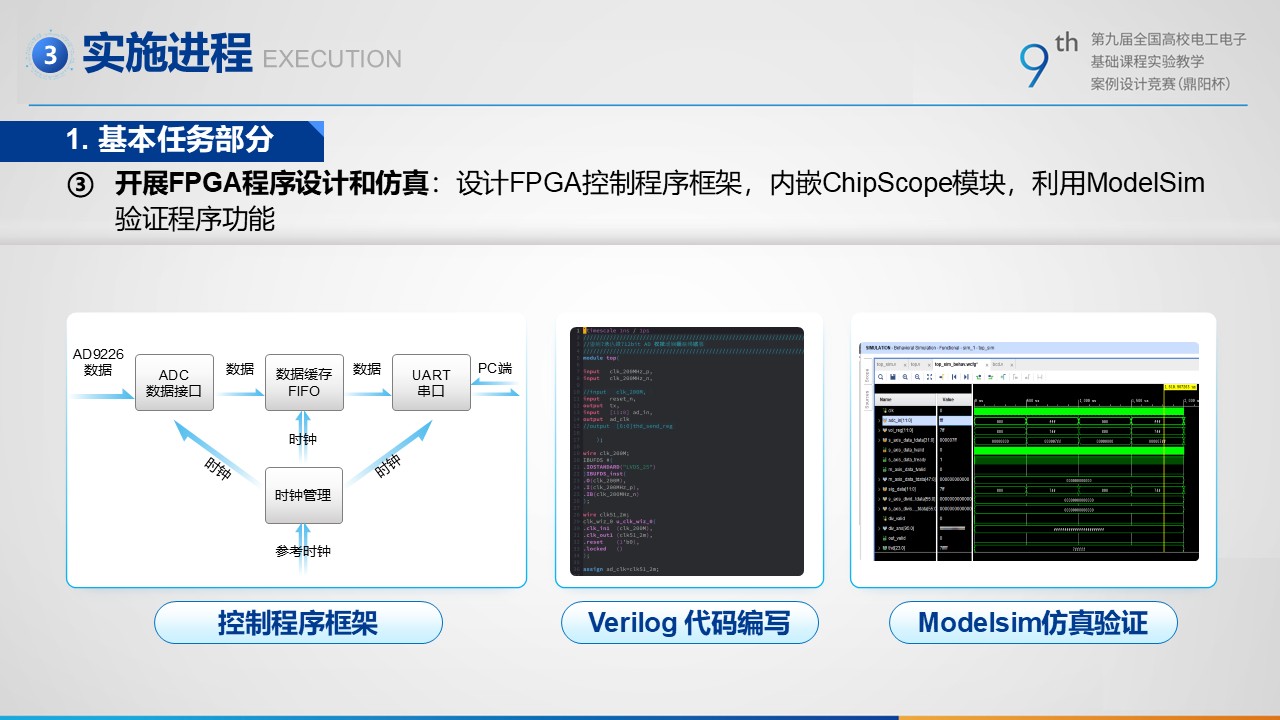

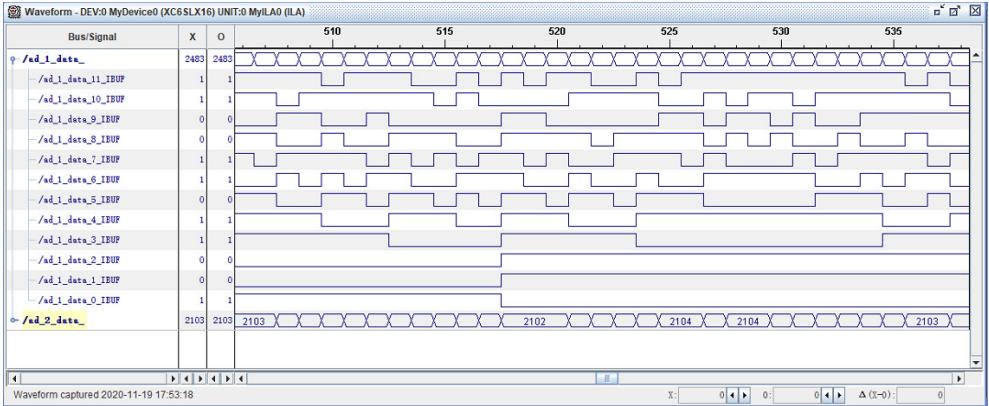

2)掌握 VHDL/Verilog 硬件描述语言设计方法。基于所提供的 FPGA 核心板,编写AD9226的驱动代码,并内嵌在线分析IP,为导出采样数据提供基础。

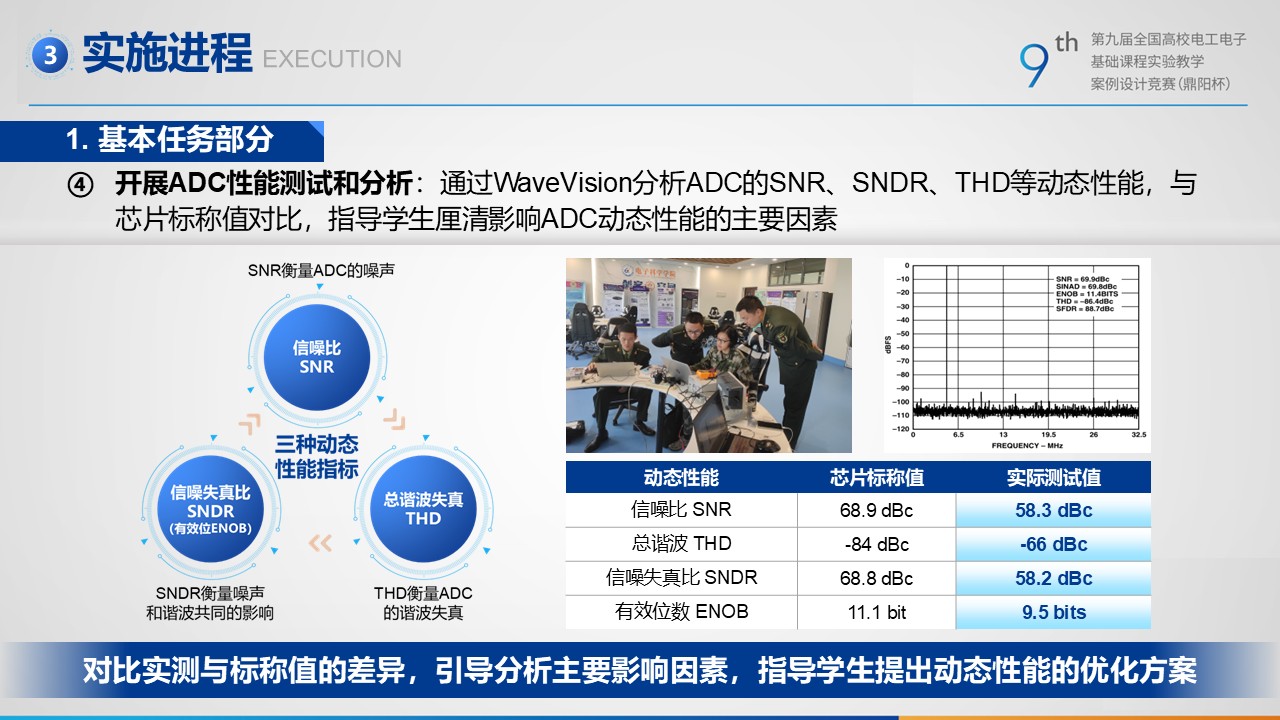

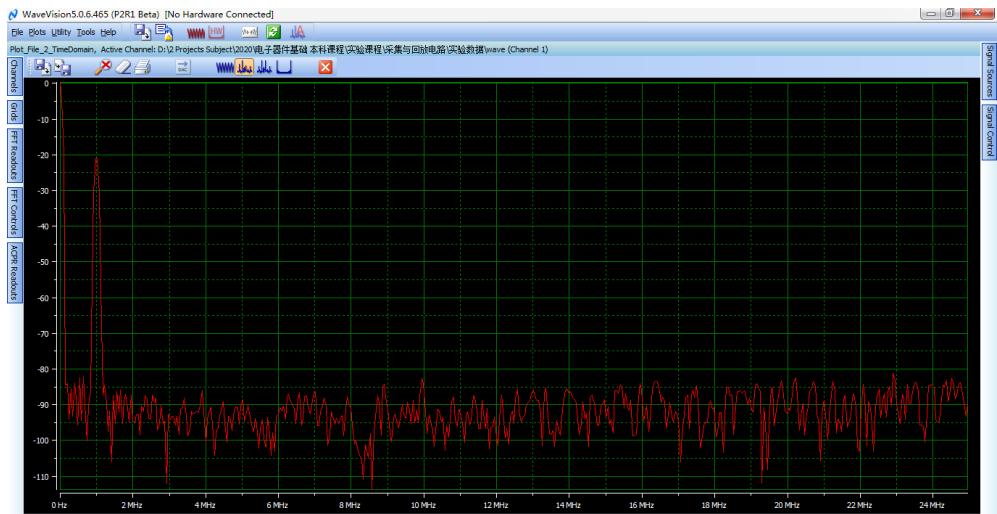

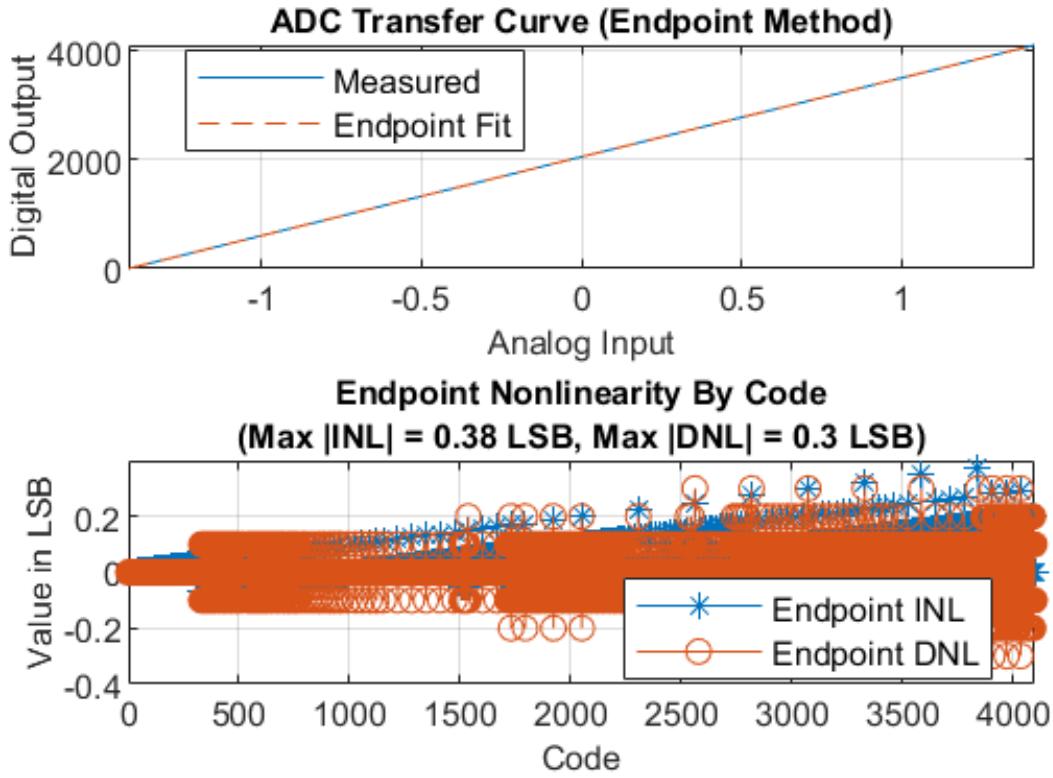

3)掌握 ADC 性能指标及其分析方法。绘制 ADC 的幅频响应曲线,并通过WaveVision软件分析ADC的满量程(FSR)、信噪比(SNR),无杂散动态范围(SFDR)以及有效位数(ENOB)等性能指标。

2. 能力提升要求(2 课内学时 $\mathbf { + 4 }$ 课外学时):

在完成基本任务要求的基础上,设置以下扩展要求,加深学生对相关知识的理解和掌握。

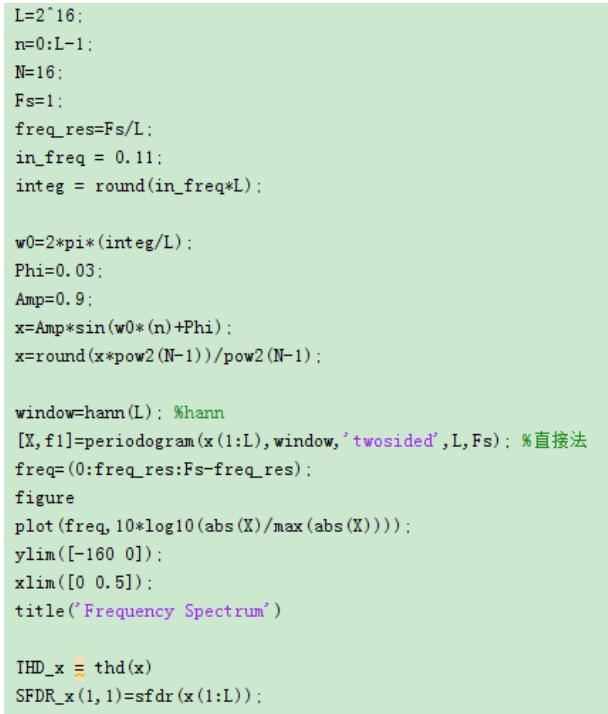

1)深入理解ADC动态性能分析方法。基于ADC动态性能的测试原理,自行编写Matlab 代码,分析 ADC 的 SNR,SFDR 以及 ENOB 等性能指标,并与商业软件 WaveVision的结果比对,分析差异来源。

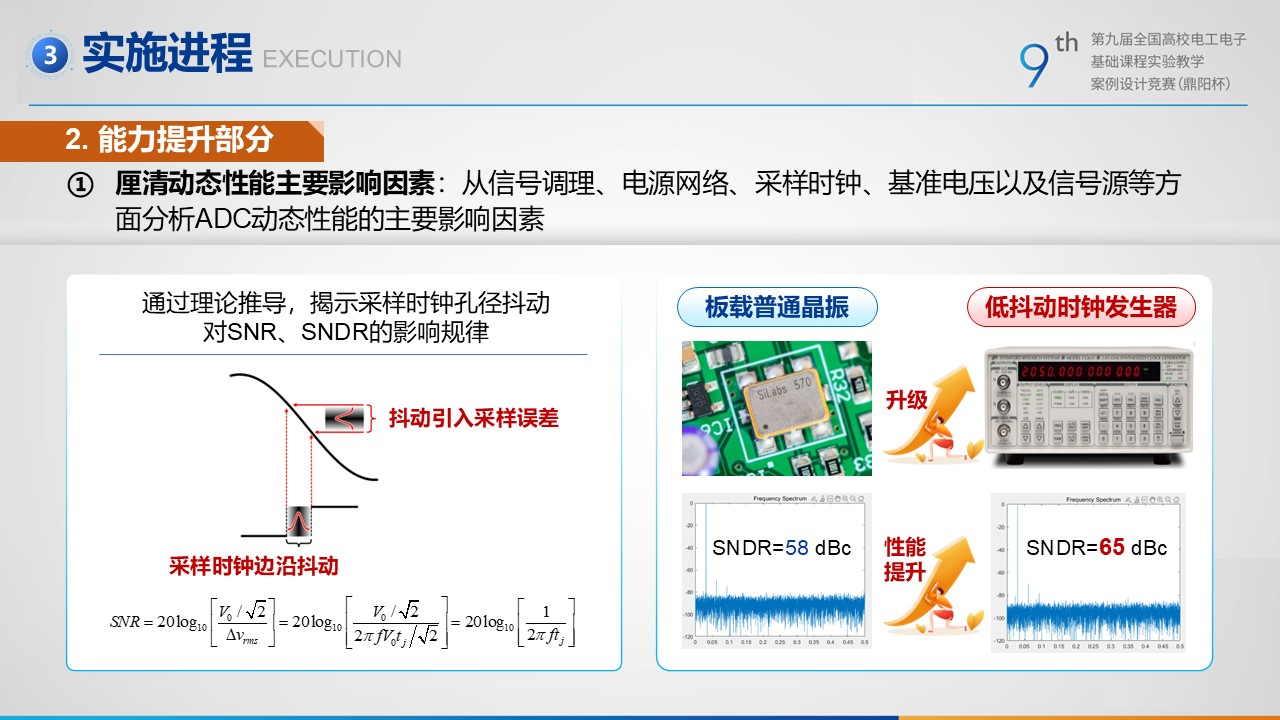

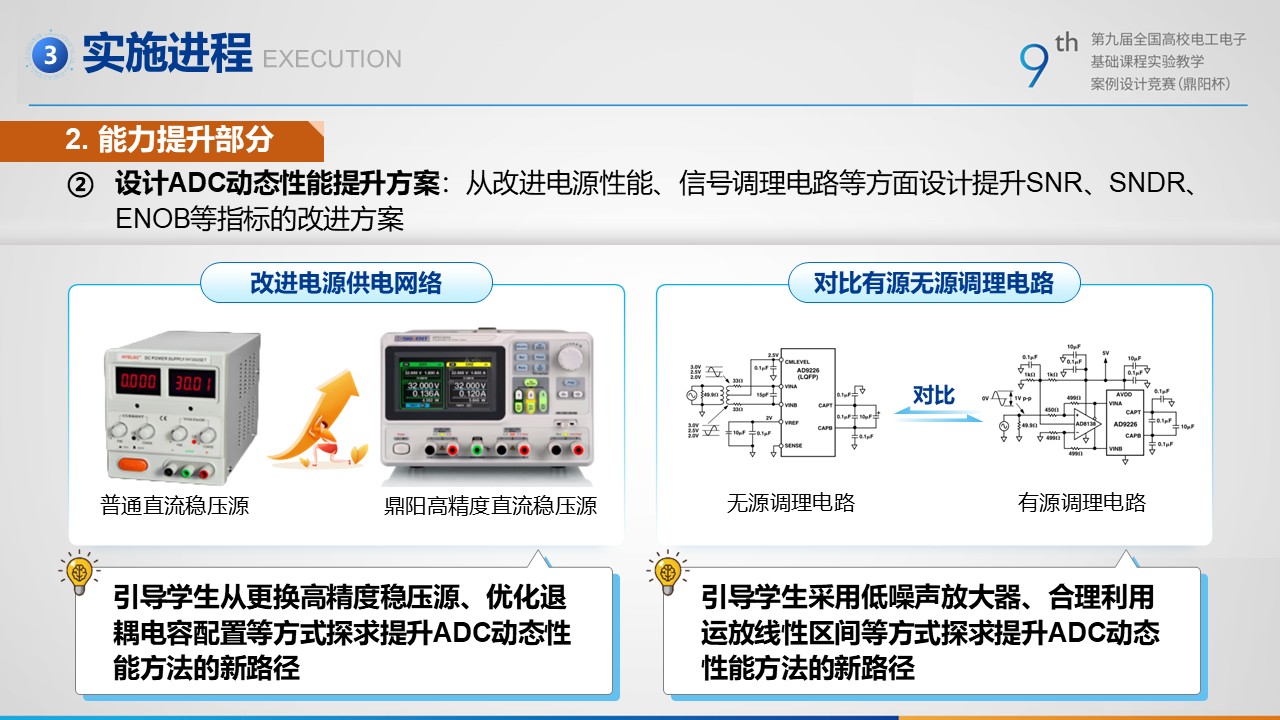

2)深入理解影响ADC性能的因素。从直流电源、采样时钟以及信号源等各个方面查找分析影响 ADC 性能的主要因素,及其在 SNR、SFDR、ENOB 等核心动态性能指标上的作用规律。

3. 工程实践应用(2 课内学时 $\pm 4$ 课外学时):

在上述工作的基础上,以教学团队所承担的某航天测控子系统研发项目为牵引,进一步突出实践应用导向,提升学员解决实际问题能力,培养系统设计思维。

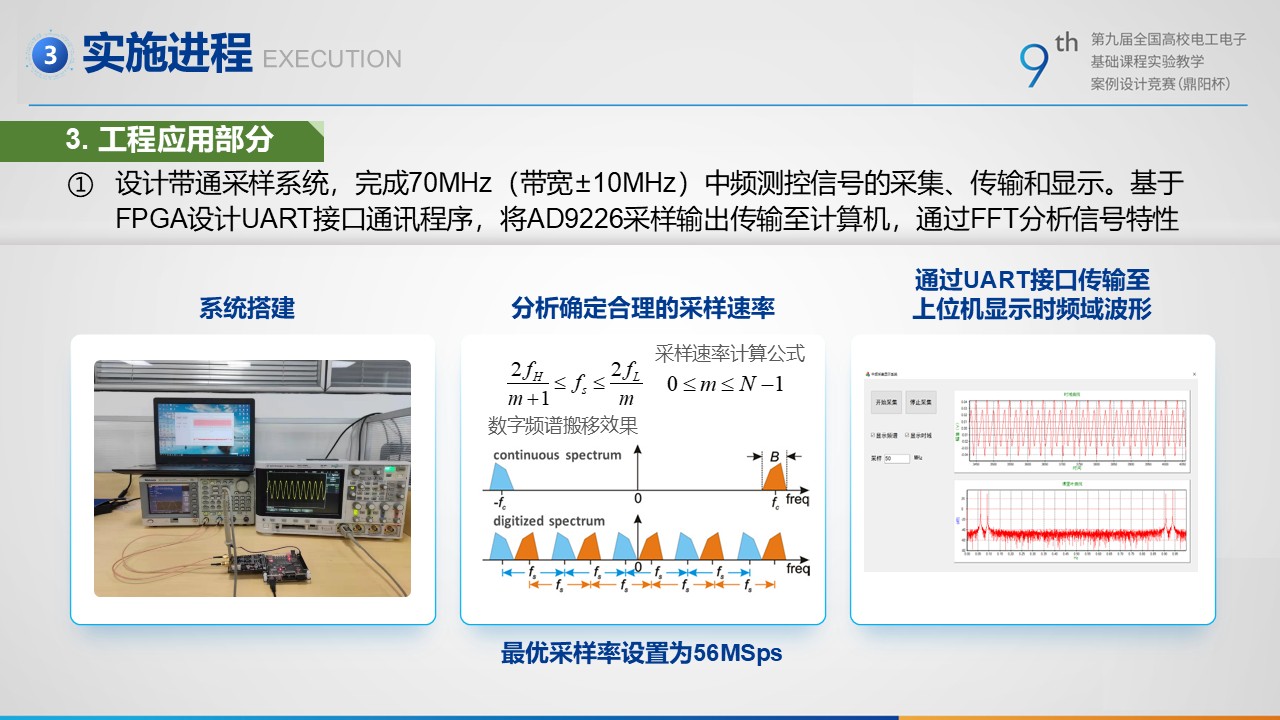

1)航天测控系统是导弹飞行试验和卫星发射运行中的重要设施,地面测控站需要接收飞行器反馈的工作状态数据,以便进行飞行器的健康分析,实现对飞行器的测距、测速、测角以及遥控等功能。而要完成这些复杂功能需要采集记录设备对中频载波信号进行模数转换,本实验第三部分以此工程应用为背景,基于所设计实现的ADC 性能测量分析系统,采用带通采样模式完成 70MHz(带宽±10MHz)中频测控信号的采集、传输和显示,基于 FPGA 设计 UART 接口通讯程序,将 ADC 采样输出传输至计算机,通过 FFT 分析信号特性。

4. 其它要求:

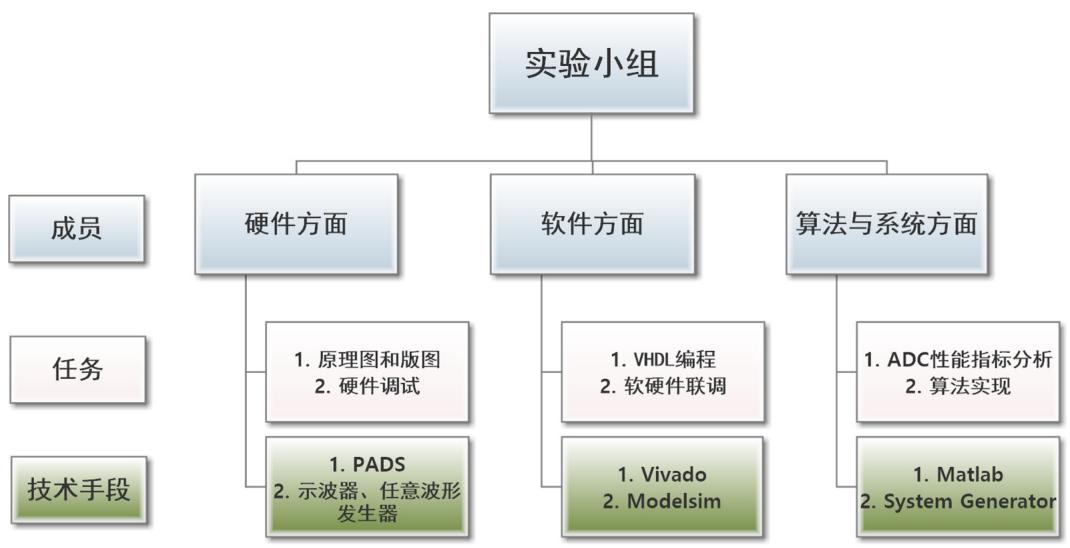

1)团队协作能力培养:要求 3 名学生一组,1 名担任组长。按照上述 3 点实验步骤和要求开展,不仅要求有详实的设计文档和总结报告,而且需要详细记录实验中遇到的各种问题,鼓励团队协作分析和解决问题。

2)系统设计思维塑造:通过实践理解电子系统集成化、芯片化趋势,掌握自顶向下法、自底向上法等设计方法,完整体验从调查研究、方案论证、单元电路设计、器件选择、组装调试到编写总结报告整个设计流程。

3. 相关知识及背景

模数转换器(ADC)是连接模拟世界和数字世界之间的唯一桥梁,是支撑现代信号处理的基础。ADC 是模电、数电、电子系统设计以及专用集成电路设计等课程中的重要组成章节,本实验要求基于 FPGA 设计 ADC 性能测量分析系统,涉及 ADC、放大器、时钟、电源等硬件单元电路设计与实现等相关知识与技术方法,基于 FPGA 的数据缓存、接口传输程序的仿真与调试,示波器、任意波形发生器、频谱仪等测量仪器的操作方法,动态指标 SNR,SFDR 以及 ENOB 的计算及多种测量途径实现等工程概念与方法。

4. 实验环境条件

1)实验场地:本实验依托国防科技大学电子科学与技术实验中心(国家级教学示范中心)以及电子科学学院创客空间开展。

图 1 课程所依托的实验场地

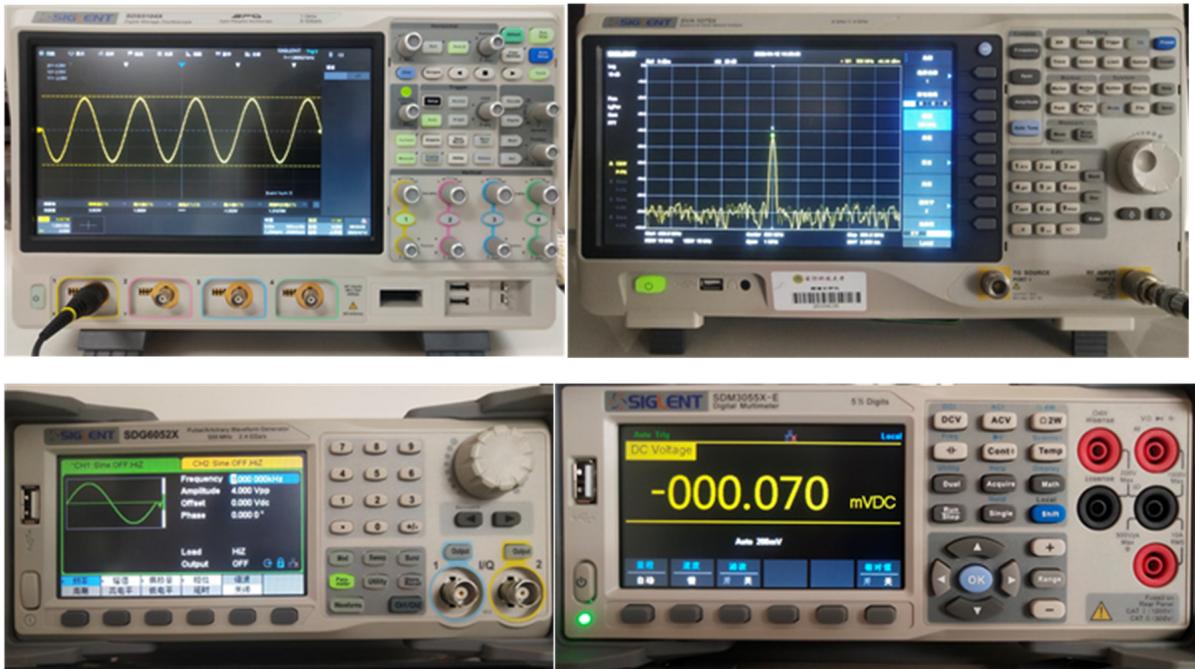

2)实验仪器:所需的实验仪器包括高速示波器(SDS5104X)、频谱分析仪(SVA1075X)、任意波形发生器(SDG6052X)、数字万用表(SDM3055X-E)等。

图 2 课程所采用的实验仪器

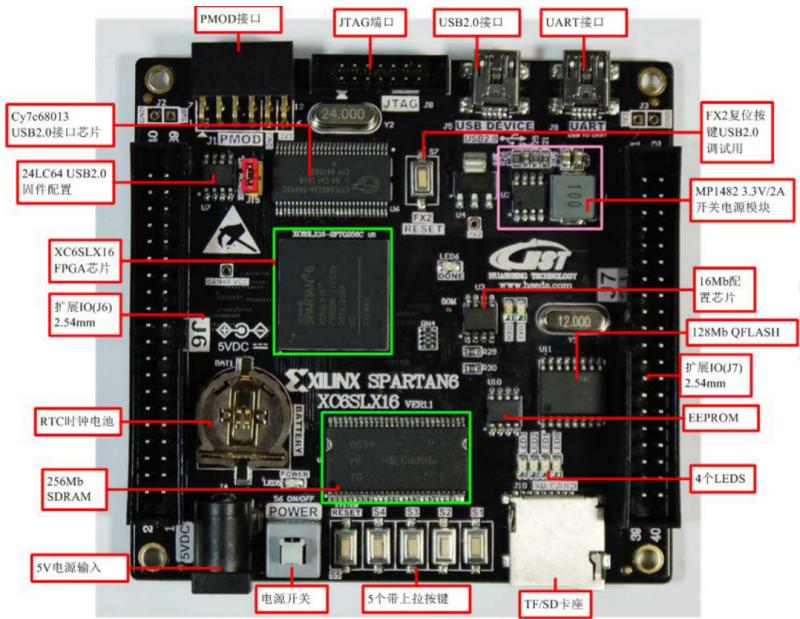

3)硬件电路:主要包括 FPGA 主控板和 AD 核心板其中 FPGA 主控板基于 Xilinx 公司 Spartan6 实现,具有丰富的外设资源包括:

16 位 256Mb SDRAM16Mb FLASH128Mb QFLASH4Kb EEPROM1 个实时时钟芯片1 个 USB 转 UART 接口1 个 USB 2.0 接口$\bullet$ 按键、LED 若干

具有良好的扩展性能、开发板引出了 84 个扩展 IO,并做等长处理,可连接音频输入输出卡、视频输入输出卡、AD、DA、千兆网模块。

图 3 FPGA 主控板主要接口及元器件

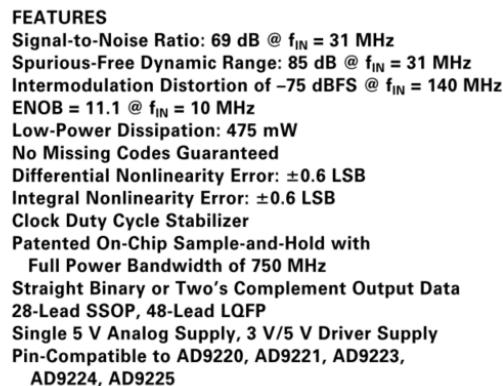

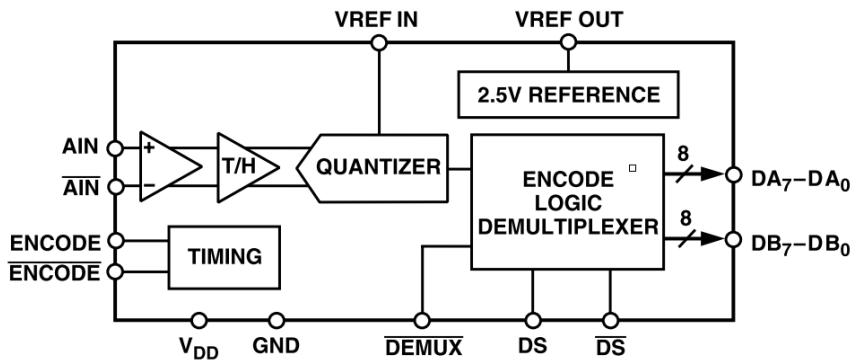

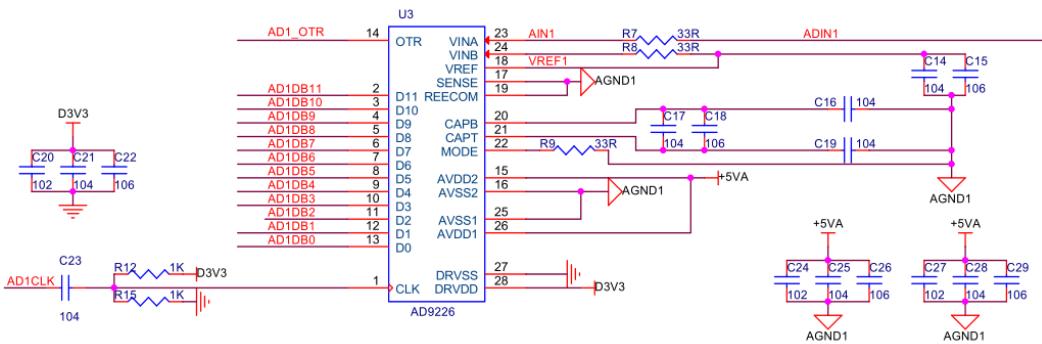

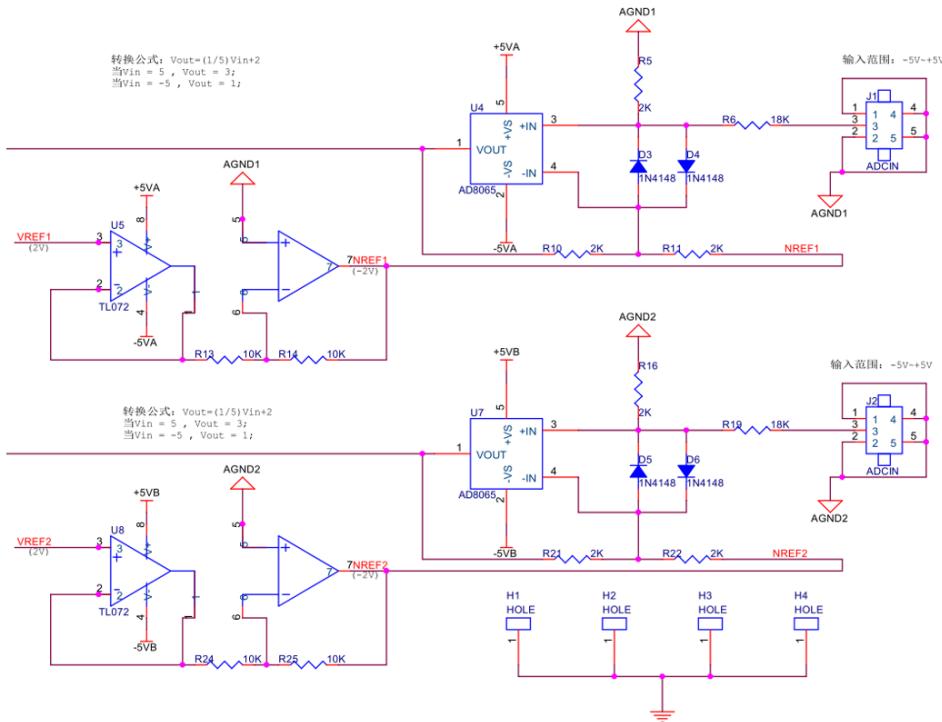

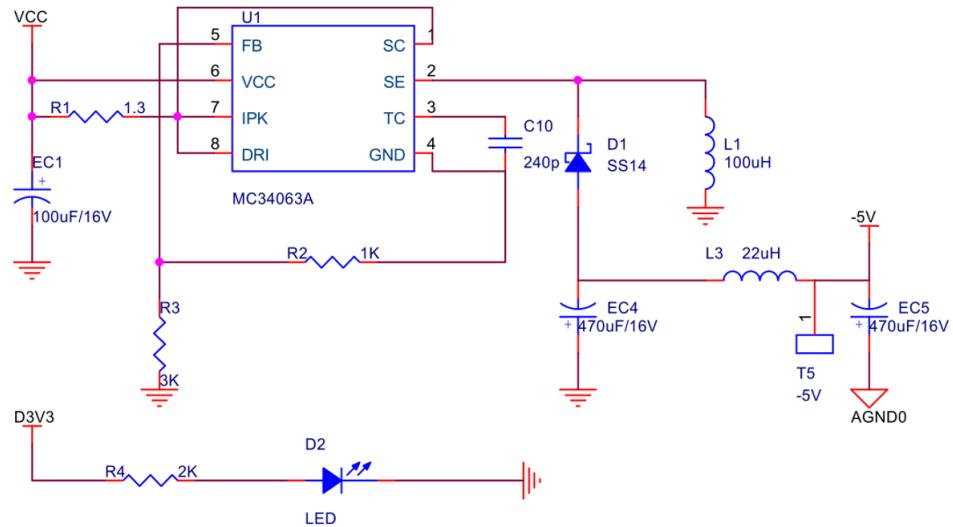

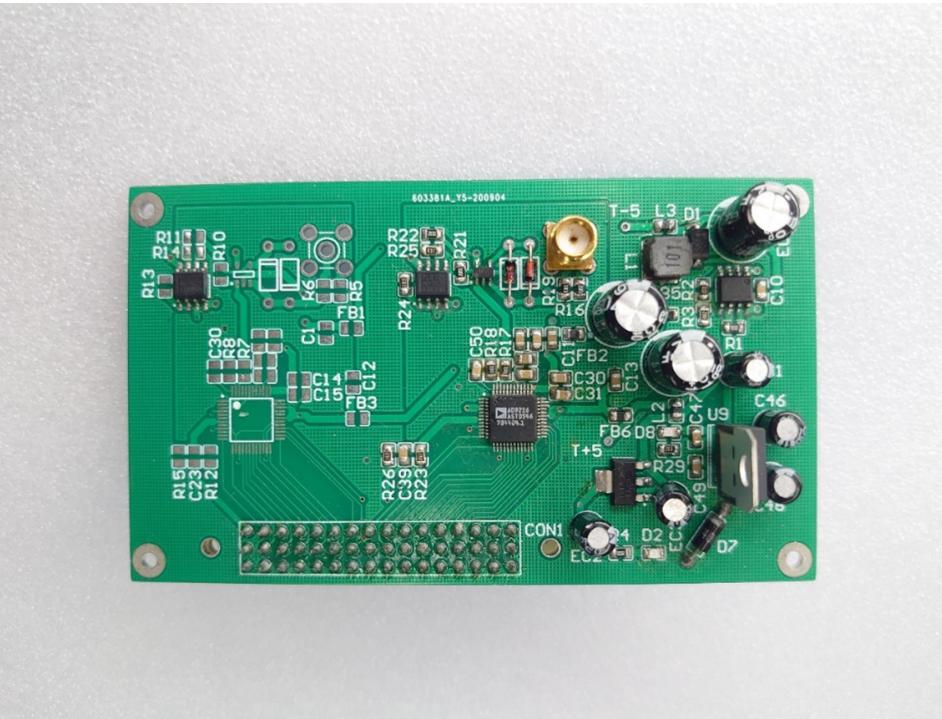

其中 ADC 核心板基于 ADI 公司 65MSps 12bit ADC(AD9226)设计实现,其主要主要性能指标及内部结构如下图所示。

Complete 12-Bit, 65 MSPS ADC Converter

AD9226

FUNCTIONALBLOCKDIAGRAM

图4 AD9226主要性能指标及内部结构

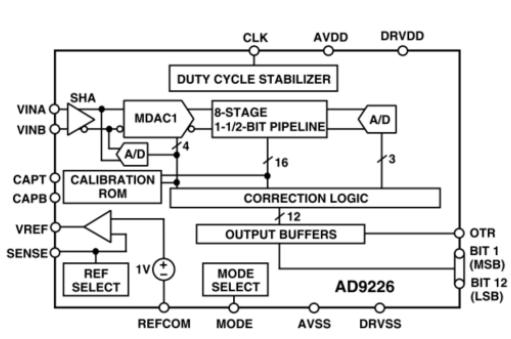

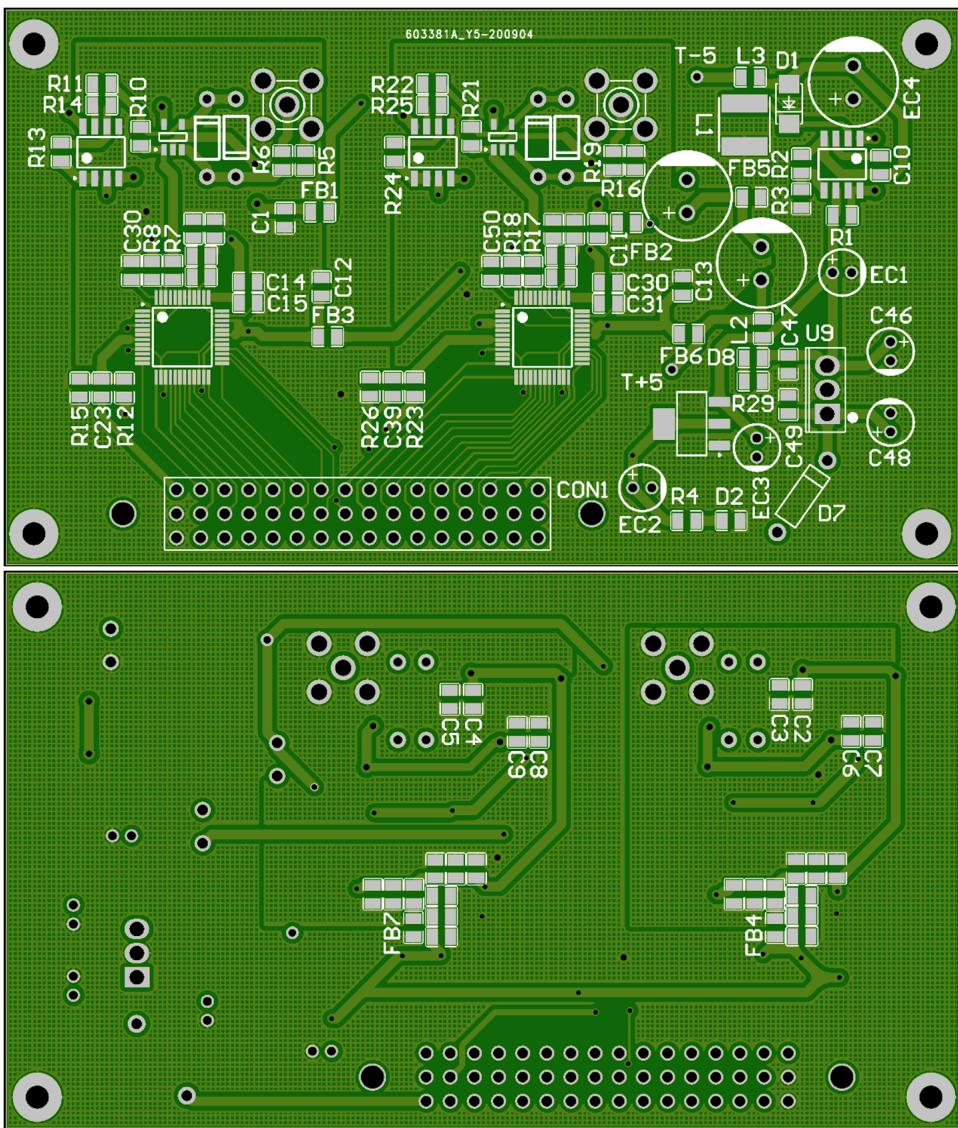

图 5 2019 级学生所设计的 AD9226 板卡

4)软件工具:

ADC单元电路设计相关软件

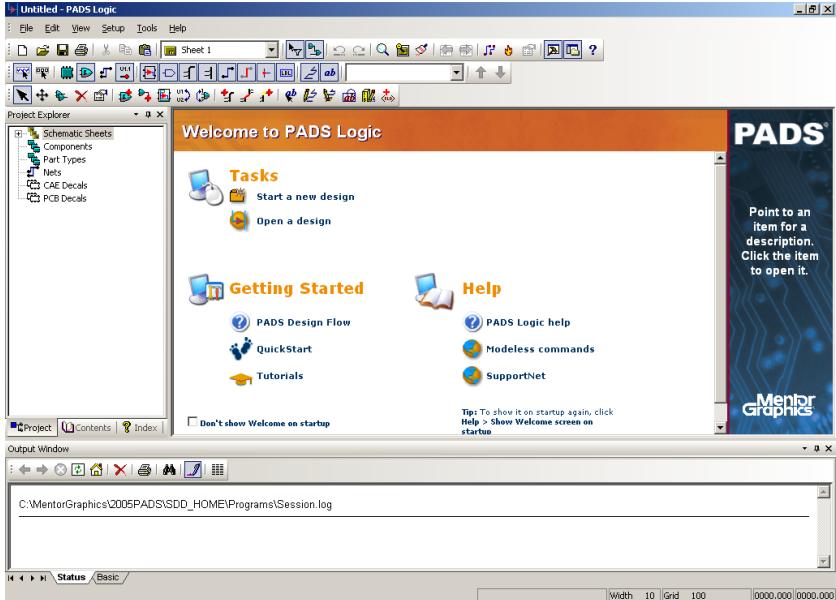

图 6 原理图设计软件:PADS Logic

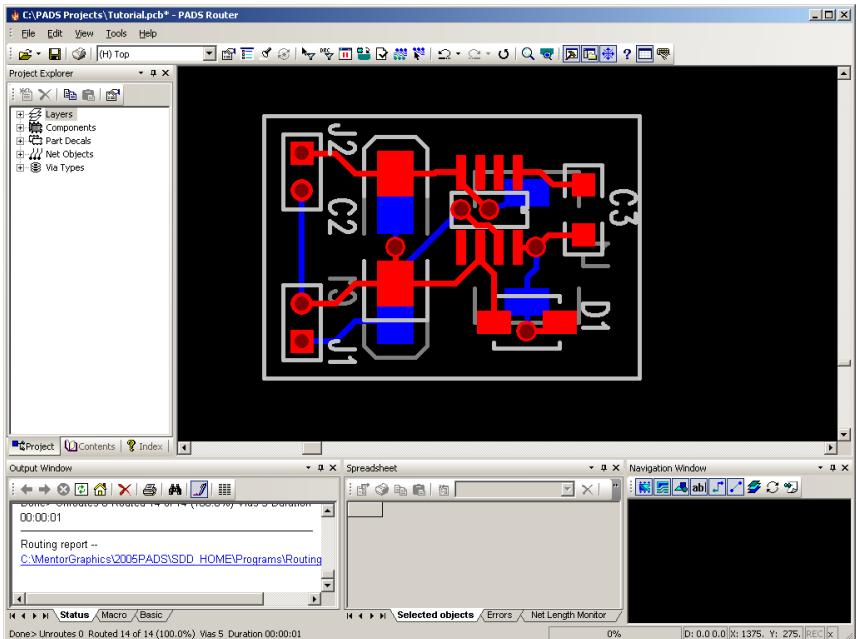

图 7 版图设计软件:PADS Layout & Router

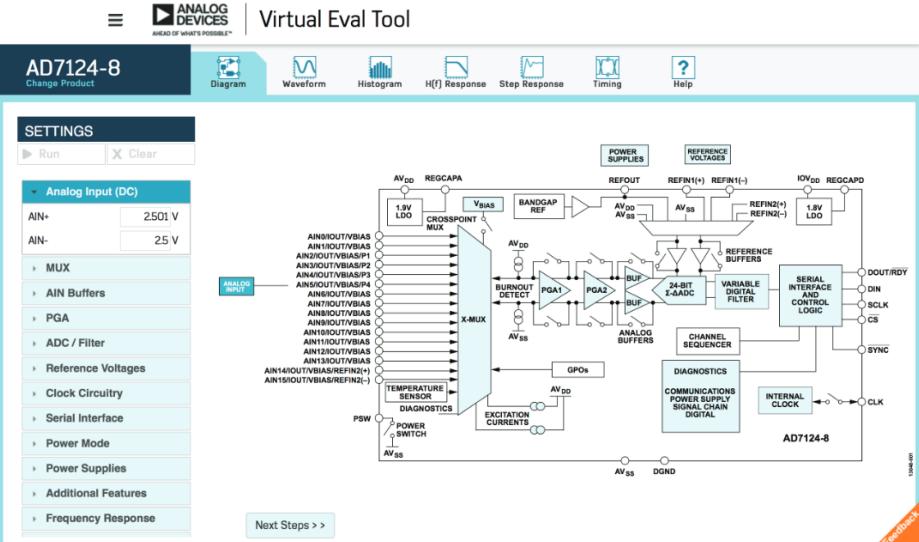

图 8 ADC 虚拟仿真软件: Virtual Eval

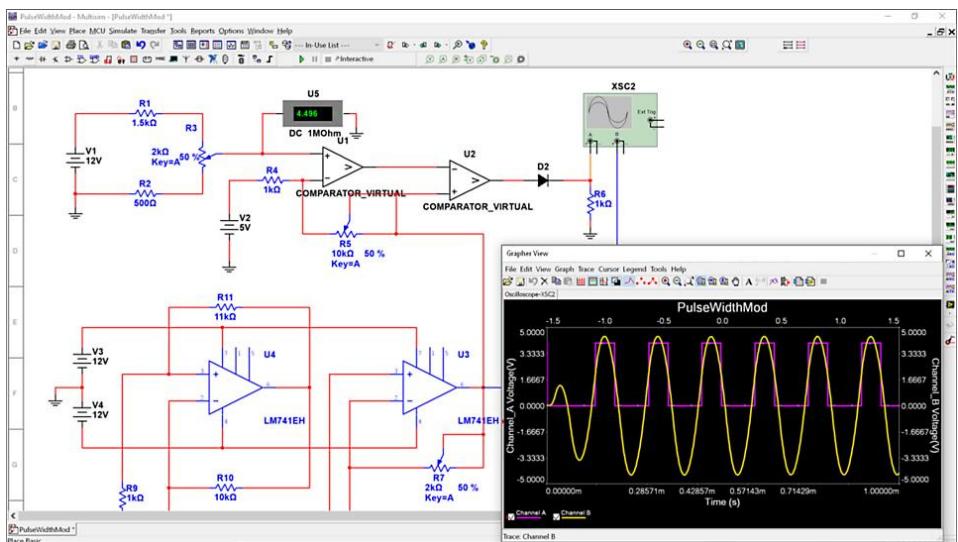

图 9 模拟电路仿真软件: Mutisim

FPGA 开发和分析软件

Xilinx, Inc.

2100 Logic Drive·San Jose, CA 95124 www.xilinx.com

Xilinx ISE Design Suite 12

ISE® Design Suite 12 software unlocks greater design productivity with breakthrough technologies for power optimization and cost.The Design Suite enables the fastest timeto design completion with Xilinx Targeted DesignPlatforms-availablein four configurations aligned to user-prefered methodologylogic,embedded,P,orsstemesign.

£ XILINX.

Xilinx Targeted Design Platforms provide embedded,DSP,and hardware designers with access to an array of devices supported by open standards,common design flows, IP,and runtime platforms.The ISE Design Suite offers domain-specific design environments and enables designers to meet power and performance goals with Xilinx CPLDs and FPGAs,including the new Virtex-6and Spartan@-6 families.

FEATURES

ISE Design Suite provides atight connection between embedded and DSPflows to enable integration of designs with embedded, DSP, IP, and user blocks in one system.Forusers familiarwith difering design environments,ISEDesignSuite 12providesaccommodationsranging from the push button user to the advanced designer.

Design preservation flow to improve timing predictably >Partial reconfiguration supporting Virtex-6 FPGAs 〉Intelligent clock gating supporting Virtex-6 FPGAs >Plug-and-play FPGA design through AMBA4 AXl"-4 interconnect protocol IP

图 10 FPGA 开发套件: Xilinx ISE

图 11 数据在线分析套件:Chipscope

ADC 性能分析软件

图 12 商业级分析软件:WaveVision

图13 动态性能分析算法实现:Matlab

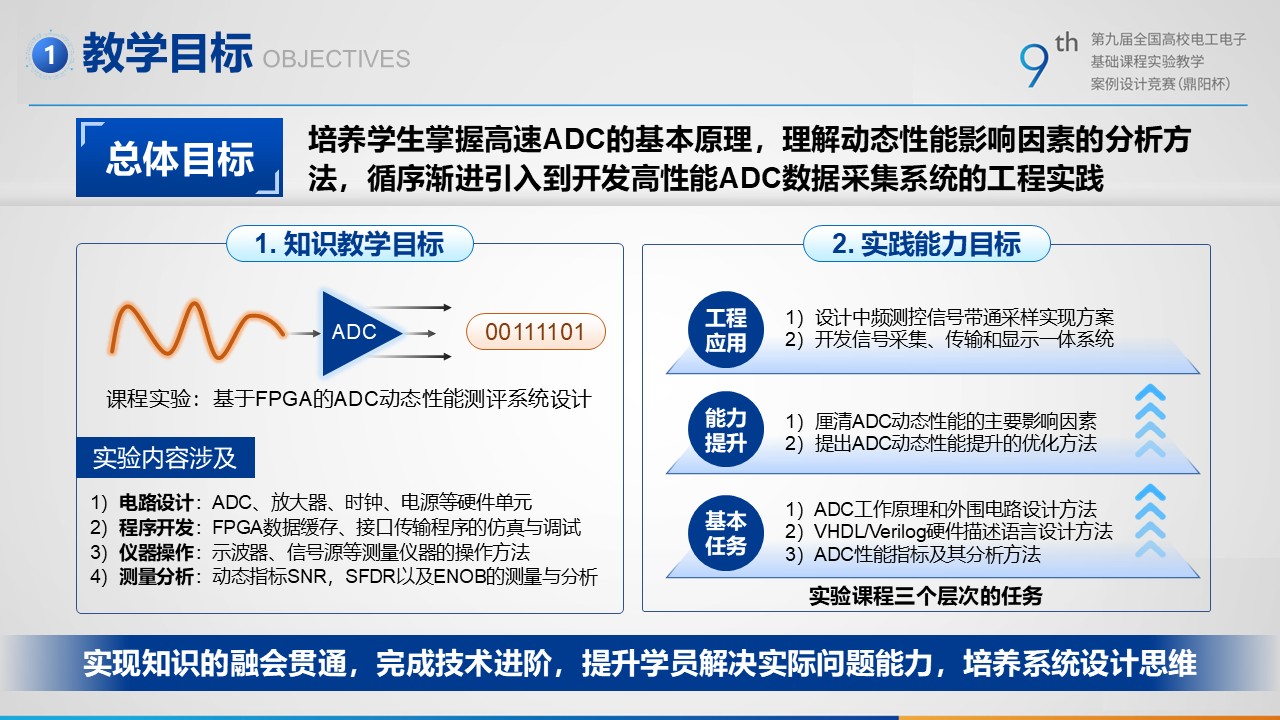

5. 教学目标与目的

通过综合性实验案例设计,我们希望实现下述教学目标:

1)贯通专业知识体系。 通过设计中综合运用电路分析、模/数电等课程理论知识,实现知识的融会贯通和技术进阶。

2)锻炼工程实践能力。通过经历设计全流程,锻炼发现和解决实际问题的能力,实现“以用促学,学以致用”。

3)激发创新意识和团队精神。通过挑战发挥部分,激发创新和进取意识。通过分工协作培养团队合作意识。

6. 教学设计与实施进程

6.1 教学目的

1)了解ADC的工作原理与分类,熟悉ADC的主要技术指标,掌握基本指标和动态指标的测量方法。

2)掌握ADC的选型,信号调理、采样时钟以及输出接口等外围电路设计实现方法。掌握 ADC 单元电路设计和调试方法。

3)掌握基于 FPGA 的 ADC 驱动程序的编程和在线调试方法。掌握影响 ADC 性能主要因素的分析方法。

6.2 设计思路

ADC是混合信号处理系统中的重要组成单元,是连接真实的模拟世界和虚拟的数字世界之间的桥梁,是支撑现代信号处理的基石。随着技术的发展,ADC 成为工业现场、地质勘测、医药器械、电子通信、航空航天等领域中用途最广、最重要的器件。ADC 的设计也是电子器件、集成电路设计等课程中的重点内容,是学生毕业后从事电子系统、集成电路设计方向工作的重要技术储备。

作为电子科学与技术、微电子科学与工程专业学生的一个综合性设计实验,本实验以应用场景需求为牵引,将ADC的外围电路设计、FPGA程序控制、信号分析和处理、系统实现工程实践等完整的技术链和开发流程融合到一个实验中,具体设计思路包括:

1)强化工程应用的需求牵引。

结合明确的工程应用需求背景,从系统-单元电路-芯片分 3 个层次分解设计指标,最后形成对所设计的电子系统具体功能性能指标要求,与实际应用结合,例如片上雷达、软件无线电等,让学生熟悉所设计的指标参数“从何而来”,所设计的电路要“用在哪里”,塑造工程思维方式,提升实践创新能力。

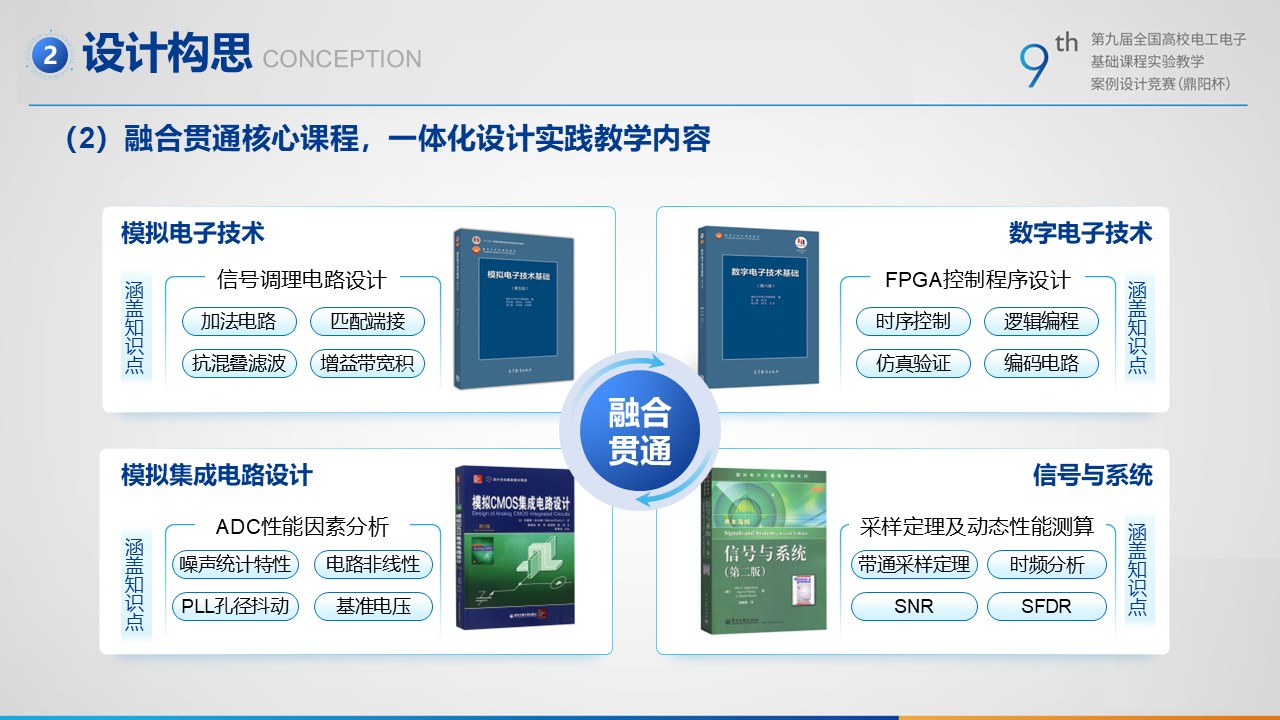

2)优化相关知识点融汇贯通。

通过一个综合性实验案例的设计,将电子信息专业的主干课程中的相关知识点形成无缝衔接,让学生深入理解电路分析、模拟电子技术、数字电子技术、电子器件基础、专用集成电路设计等课程中的相关知识点的内在联系,实现知识的融会贯通。

3)集成化、芯片化设计思维培育。

在电子系统领域,电子系统集成化、芯片化成为当前最主要的发展趋势,本课程正是适应这一发展趋势,帮助学生认识芯片,掌握芯片内部架构、原理和设计使用方法,培养学员基于芯片设计专用电子系统的能力,为后续专业课程和创新实践活动打下坚实基础。

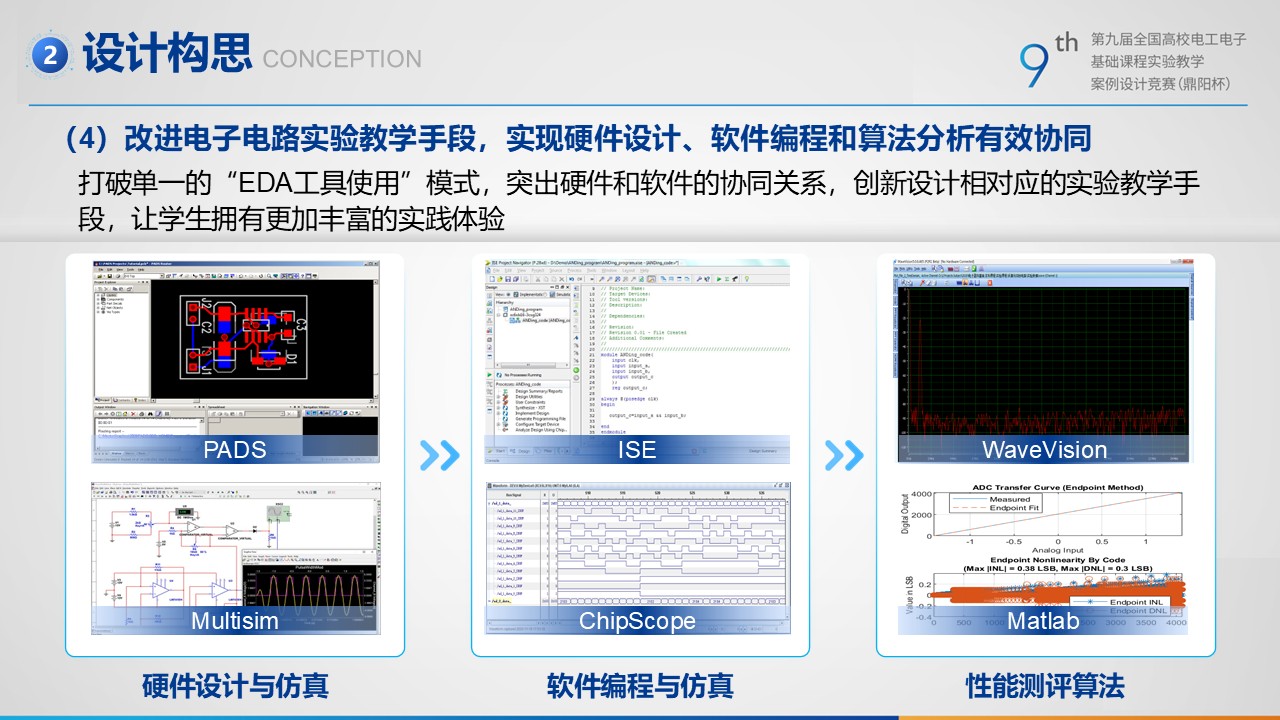

4) 改进电子电路综合性实验教学手段。

针对上述“贯通型、全流程”实验特点,打破单一的“EDA工具使用”模式,突出硬件和软件的协同关系,创新设计相对应的实验教学手段,“软硬”结合,让学生拥有更加丰富的实践体验。

6.3 教学实施步骤

本课程实验为综合性、设计型实验,根据教学设计思路,和三个层次的任务要求,我们将全部试验内容按照电子系统设计流程划分为若干步骤和板块,学生了解实验顶层设计框架后,依次完成推进各个单元设计。计划通过8个课内学时和12个课外学时,共20学时的教学环节完成整个课程实验,具体步骤如下表所示:

| 课次 | 实验内容 | 课时 | 主要实验步骤 | 教学方法 |

| 基本任务部分(8学时) | ADC 工作原理、性能指标以及外围电路设计方法 | 2 | 1)应用场景介绍2)工作原理介绍3)SAR、FLASH、M-△ADC等特点和工作原理4)基本指标和动态性能指标分析5)信号调理、时钟、电压基准、电源、去耦设计 | 老师讲授分组研讨 |

| AD9226采集单元硬件设计 | 2 | 1)学生选定外围电路元器件,完成ADC单元电路原理图设计2)完成单元电路仿真评估3)完成PCB版图设计 | 学生设计老师答疑安排投板 | |

| 基于 FPGA 的 ADC 驱动程序编写 | 2 | 1)学生熟悉FPGA核心板2)学生按照提供参考的 AD9226寄存器指令和控制时序完成驱动程序编写 | 学生设计老师答疑 | |

| 电路测试与性能分析 | 2 | 1)完成ADC电路的焊接和调试2)利用AWG产生测试信号完成测试3)利用软件分析待测 ADC 的动态性能 | 学生测试老师答疑 | |

| 能力提升部分(6学时) | 完成动态性能分析算法编程、掌握电路影响因素的分析方法 | 4 | 1)老师逐一讲授时钟、电源、非线性等影响动态性能的因素2)学生分析测试结果,查找与手册性能的差异及可能的原因3)编写Matlab程序,能够实现对信噪比,无杂散动态范围、有效位数等指标的 | 学生设计老师答疑分组研讨 |

| 分析 1)逐一测试时 | ||||

| 测试验证 | 2 | 钟、电源、非线 性对ADC 测量结 果的影响 2)总结现有设计 方案,提出改进 方法或策略 1)老师介绍项目 | 学生测试 老师答疑 | |

| 工程应用部分 (6学时) | 工程案例需求讲解分析 以及电路设计测试 | 4 | 应用背景和指标 要求 2)将系统指标分 解为对ADC系统 的测量指标 3)学生按照要求 设计带通采样传 输系统 4)完成中频数传 基带信号的测 试,分析测试结 | 学生设计 老师答疑 分组研讨 |

| 实验总结分组汇报 | 2 | 果和性能 1)学生完成实验 总结报告 2)按照分组汇报 实验结果,并展 示作品 | 分组报告 与作品展 示 老师点评 与提问 |

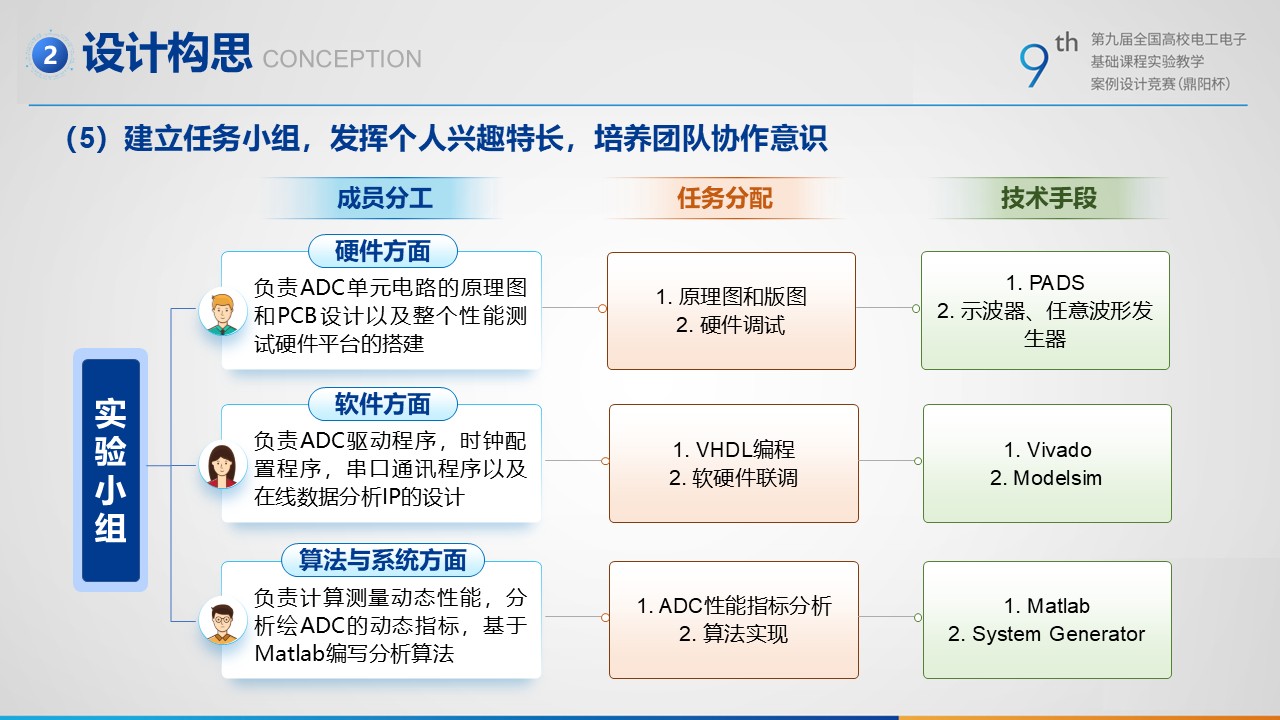

为了能够更好的达到实验效果,发挥个人兴趣特长,培养团队协作意识,对学生的分组方式补充说明如下:学生按照 3 人成组,推选 1 名同学作为组长负责整个实验推进以及总结报告的撰写和合稿。3 名同学推荐按照以下方法划分任务,其中第一名同学负责 ADC单元电路的原理图和 PCB设计以及整个性能测试硬件平台的搭建;第二名名同学负责 ADC 驱动程序,时钟配置程序,串口通讯程序以及在线数据分析IP 的设计;第三名同学负责掌握动态性能测量软件使用,分析绘制 ADC 的基本指标和动态指标,并能够基于Matlab编写性能分析算法代码。

图 14 实验小组成员分工示意图

由于本实验综合性较高,涉及到的知识面较宽,在实验过程中,我们鼓励学生通过互联网、书籍、论文查阅相关资料。对于疑难问题,尽量自己寻找解决方案,授课老师给予思路上和方法上的引导。 在课后时间,教师通过 QQ 群,微信群进行在线答疑,创客空间和电路实验室等延长开放时间,方便学生完成课外实验的环节。

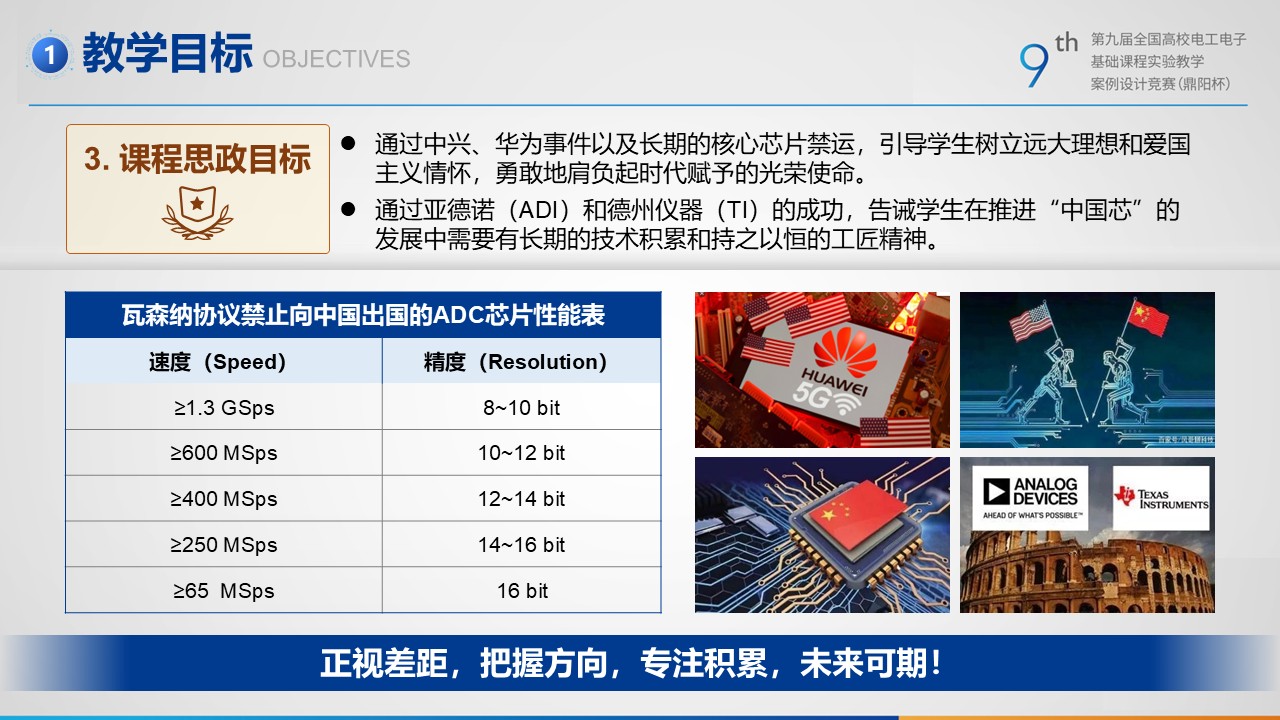

6.4 课程思政设计

1)在课程讲授过程中,通过国外对我国实施的 ADC/DAC 产品禁运(美国商务部对 ADC 芯片的禁运指标如下表所示),结合中兴、华为事件凸显出的对芯片设计与制造人才的急迫需求,引导学生树立远大理想和爱国主义情怀,勇敢地肩负起时代赋予的光荣使命。

表 1 美国商务部 ADC 芯片禁运表

| 瓦森纳协议禁止向中国出国的ADC芯片性能表 | |

| 速度 (Speed) | 精度(Resolution) |

| ≥1.3GSps | 8~10 bit |

| ≥600 MSps | 10~12 bit |

| W400MSps | 12~14bit |

| ≥250MSps | 14~16 bit |

| W65 MSps | 16 bit |

2)结合教学内容相关知识点,通过华为海思设计的基带芯片、5G 芯片的自主研发等典型事例,引导学生向业界前辈学习,培养学生的敬业精神;

图 15 课程思政素材

3)罗马城不是一天建成的,通过介绍亚德诺(ADI)和德州仪器(TI)的成功案例,这两家模拟芯片的巨头公司能实现现在的成就和规模,靠的是几十年的时间积累,告诉学生成功需要有持之以恒的工匠精神。

图 16 课程思政素材

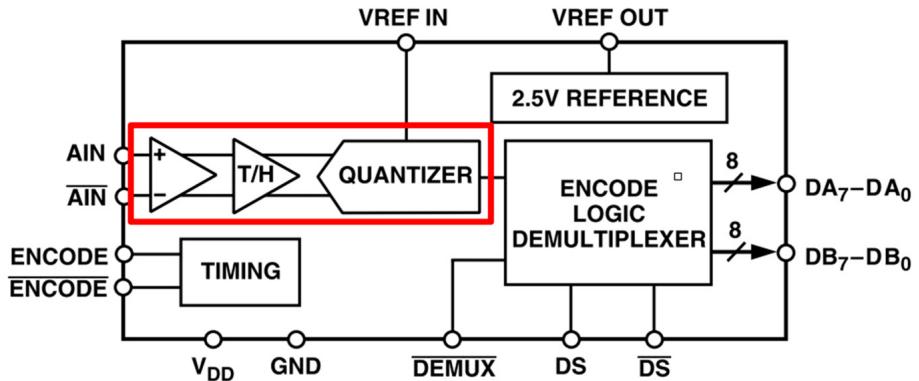

4)通过采样保持电路和量化比较电路分析过程的讲解,帮助学生建立用数学思维模式来描述和解决工程问题的工程意识,将学习的知识体系做到前后贯通,提升学生的科学素养。

7. 实验原理及方案

7.1 ADC 基本知识

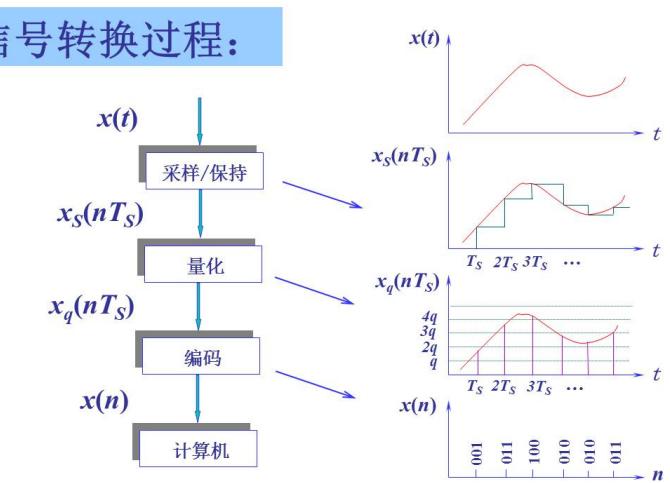

1)模数转换基本原理

模数转换器就是将模拟输入信号转换为数字输出量的器件,它是混合信号处理系统中的重要组成单元,连接真实的模拟世界和虚拟的数字世界之间的桥梁,是支撑现代信号处理的基石。其内部组成单元如下图所示,通常包括了采样保持电路(T/H),比较量化电路(Quantizer),编码逻辑电路(Encode Logic)以及电压参考、定时电路和缓冲放大电路等。

图17 典型ADC内部框图

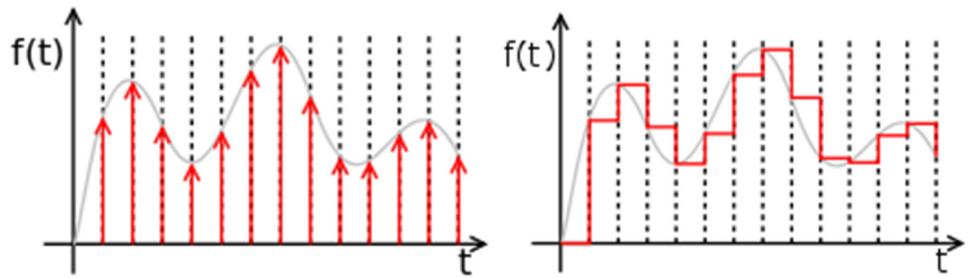

要实现将连续变化的模拟信号变为离散的数字量,需经过四个步骤:采样、保持、量化、编码,其中前两个步骤由采样-保持电路(S-H)完成,后两个由比较器和数字逻辑电路完成。

图 18 信号转换的 4 个步骤

采样保持:采样保持(T/H)是模数转换过程的第一步,考虑到其后的量化和编码操作需要一定的时间,为了使 ADC 转换后的数字信号能够正确的反映原始的的模拟信号,需要在一次转换周期内加在 ADC 上的模拟信号电压保持在某一个固定的采样值上。但是由于模拟信号本身是实时变化的,故需要采样保持电路固定样本值。

图 19 采样保持对模拟信号的影响

量化:量化就是采用有限字长的一组二进制码去逼近离散的模拟信号幅值,其本质是将采样信号的幅值与某个最小数量单位的一系列整数倍比较,以接近于采样信号幅值最小数量单位倍数来代替该幅值,他是 ADC 的主要功能。其中最小数量单位又称为量化精度。

编码:把量化的数值用代码表示,就称为编码。编码是模数转换的最后阶段,它有多种形式,最常用的是二进制编码,例如把量化的数值用二进制代码表示,这个二进制代码就是 ADC 输出的最终信号,通常模数转换器会根据被测信号的极性特征选择编码方式,通常有单极性编码形式和双极性编码形式。

基本定理:采样定理又称为 Nyquist-Shannon 定理。

设有连续信号 $\mathsf { x } \left( \sf t \right)$ ,其频谱 X(f),以采样周期 TS 采得的信号为 xs(nTs)。如果频谱和采样周期满足下列条件:

(1)频谱 X(f)为有限频谱,即当 $| { \mathsf { f } } | \geqslant { \mathsf { f } } { \mathsf { c } }$ ,X(f) =0(2)fs ≥ 2*fc则由采样信号 xs(nTs)能无失真地恢复为原来信号 x(t)。

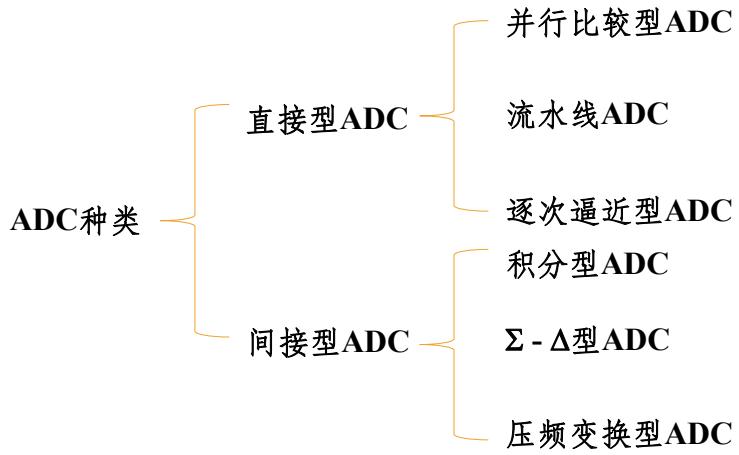

2)ADC 分类及几种典型结构

ADC 根据量化结果和输入信号的关系可以分为直接型和间接型两类,其中直接型ADC 可直接将模拟信号转换成数字信号,这类转换器工作速度快。直接型 ADC 主要有并行比较型/串行比较型 ADC、反馈比较型 ADC 和逐次逼近型 ADC。而间接型 ADC先将模拟信号转换成中间量(如时间、频率等),然后再将中间量转换成数字信号,转换速度比较慢。间接型 ADC 主要有积分型 ADC、Σ-Δ型 ADC 和压频变换型 ADC。

图 20 ADC 的分类

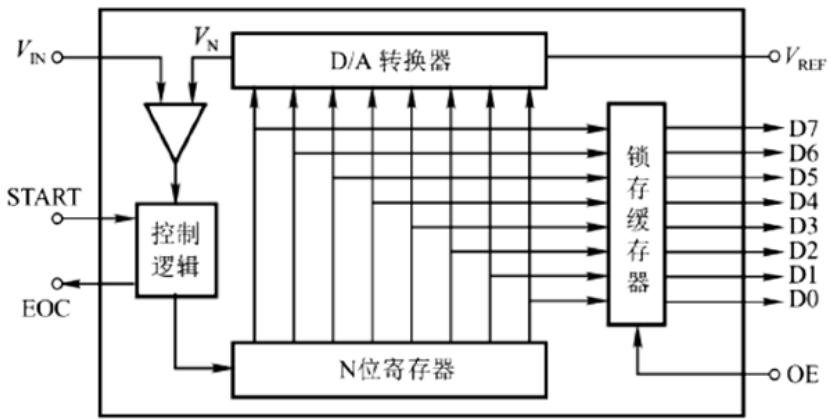

分别以逐次逼近型 ADC 和 $\Sigma - \Delta$ 型 ADC 为例,介绍两类 ADC 的工作方式。

逐次比较型 ADC 由一个比较器和 DAC 通过逐次比较逻辑构成,从 MSB 开始,顺序地对每一位将输入电压与内置 DA 转换器输出进行比较,经 n 次比较而输出数字值。控制逻辑电路首先把逐次逼近寄存器的最高位置1,其它位置0,这个数经数模转换后得到的电压值与输入信号进行比较。比较器的输出反馈到逐次逼近寄存器,并在下一次比较前对数模转换的输入值进行修正。在逻辑控制电路的时钟驱动下,不断进行比较和移位操作,直到完成最低有效位(LSB)的转换。其核心思想是用时间换取面积,其电路规模属于中等。

图 21 逐次比较型 ADC 内部结构

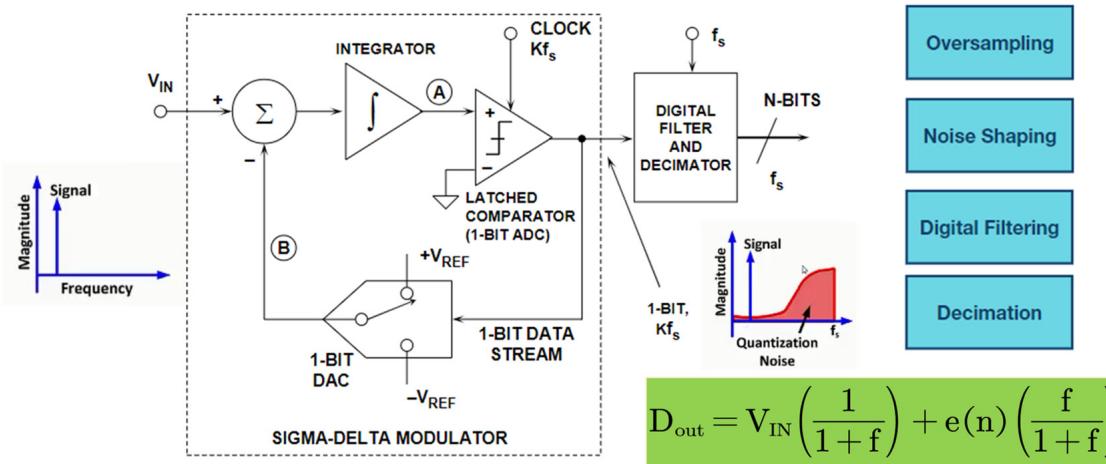

Sigma-Delta ADC 由 $\Sigma ^ { - } \Delta$ 调制器和数字信号处理模块组成,其中调制器包括了积分器,比较器,1bit DAC 组成,数字处理部分由低通滤波器和抽取器组成。原理上近似于积分型,将输入电压转换成时间(脉冲宽度)信号,用数字滤波器处理后得到数字值。电路的数字部分结构简单,更加适合实现高分辨率转换。

图 $2 2 \Sigma { - } \Delta$ 型 ADC 内部结构

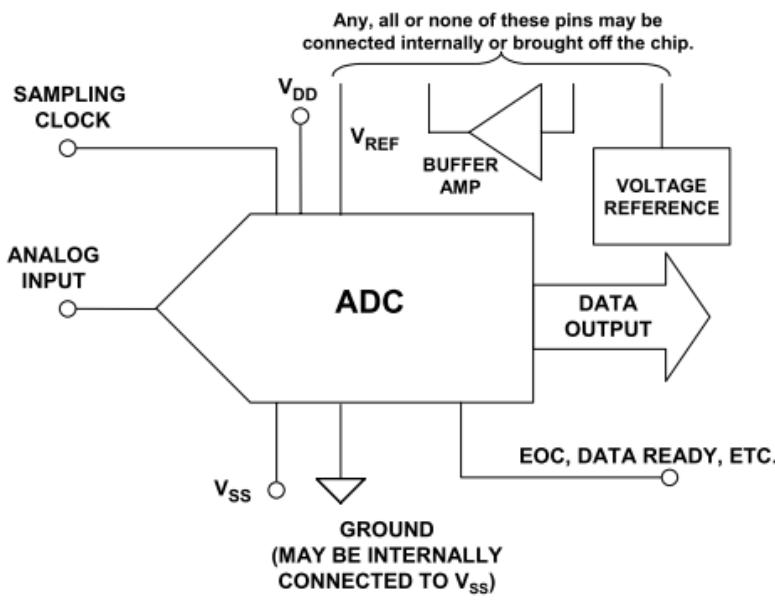

3)外围接口及设计注意事项

如下图所示,ADC 的接口包括了模拟输入(Analog Input)、数字输出(DigitalOutput)、采样时钟输入(Sampling Clock)、电源(Vdd,Vss),电压基准输入(Vref)等。

图 23 模数转换器外围接口

对于模拟输入接口,它是模拟信号接入 ADC 的管脚。我们需要重点关注连接的形式,例如是单端输入还是差分输入,需要直流耦合还是交流耦合,能够承受的最大信号范围,以及在 ADC 的内部是否具有缓冲电路等。

对于数字输出接口,它是量化后数据传输的接口,通常和后端的嵌入式处理器连接,例如本实验中所采用的 FPGA,在设计时我们需要考虑,数字信号的输出形式(单端 or 差分)、速度(单边沿 or 双边沿)、电平标准(LVTTL、LVDS、LVPECL)等指标。

对于采样时钟,它是驱动整个 ADC 的工作的信号,无论是模拟电路部分还是数字电路部分都需要。高速 ADC 对于采样时钟的性能要求十分严格,时钟的抖动增加将会制约 ADC 信噪比的提高。在器件的选择上尤其要关注芯片引入的抖动(jitter,tj)。

对于电源输入,因为 ADC 是一个模数混合的器件,故其内部既包括了模拟电路又含有数字电路,首先需要考虑模拟电源和数字电源的切分问题,避免高频的数字噪声对模拟信号的干扰。其次是上电时序,有些高性能的 ADC 会对上电时序有严苛的要求。此外 ADC 电源电压也有单电源,双电源和不同电压范围之分。这需要根据系统的所能提供的电源来考虑。

对于电压基准,ADC 的基准电压有内基准、外基准和单基准、双基准之分。如系统对温漂无严格要求,优先选用内置基准电压;若系统对温漂有严格要求,可选用精密温漂的基准电压芯片,例如 MC1403、LM336 等。

7.2 ADC 性能指标与测试方法

1)基本性能指标

○1 满量程(FSR)

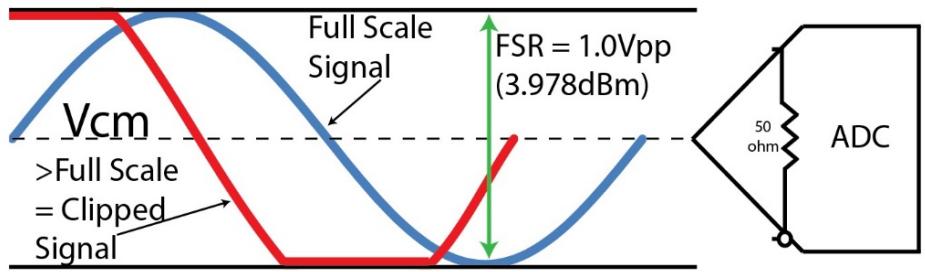

满量程是指 ADC 输入接口所能接受的最大电压范围。一般与基准电压相同。当输入信号超过量程后会出现削波的现象,影响测量的准确性。

图 24 ADC 满量程示意图

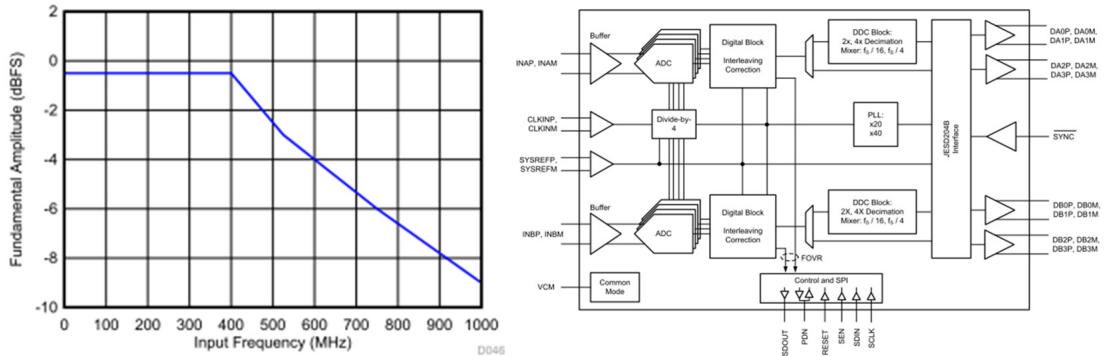

在工程设计中需要注意的是:ADC 的满量程未必是一个确定值,可能与输入频率相关。技术资料不可全信,要带有质疑的眼光。

图 25 ADS54J60 满量程随着输入频率的变化而变化

$\textcircled{2}$ 分辨率(Resolution)

指 ADC 的所能分辨模拟输入信号的最小变化值。设 ADC 的位数为 N,满量程电压为 VFSR,则 ADC 的分辨率定义为:

例如一个满量程电压为 10V 的 12 位 ADC,能够分辨模拟输入电压变化的最小值为 $2 . 4 4 \mathsf { m V }$ 。可见 ADC 分辨率的高低取决于位数的多少。因此通过我们也会用 ADC 的位数来衡量分辨能力。

$\textcircled{3}$ 采样速率(Sampling Rate)

采样速率是指每秒钟能够完成模拟量到数字量转换的次数。常用单位是 KS/s,MS/s,和 GS/s。转换周期则是转换速率的倒数。积分型 ADC 的转换时间是 ms 量级,属低速 ADC;逐次比较型 ADC 的转换时间是 s 量级,属中速 ADC;并行/流水型 ADC转换时间为 ns 量级,属高速 ADC。

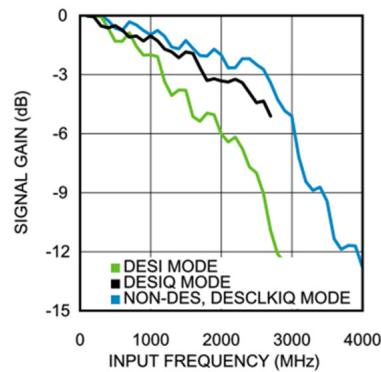

$\textcircled{4}$ 模拟带宽(Analog Bandwidth)

输入信号幅度衰减 3dB 对应的频率。ADC 的模拟带宽会受放大器、采保电路、量化电路以及寄生电容的影响。

图 26 影响 ADC 模拟带宽的内部组成模块

ADC 的幅频响应在通带内可能是不平坦的,以模数转换器 ADC12D1800RF 为例,其标称值为 2.7 GHz,但实际情况缺有所差异,思考如何处理?如何测量 ADC 的幅频响应?

3.0 Features

Excellent noiseand linearityuptoand above $\uparrow _ { 1 N } = 2 . 7$ GHz

Configurable toeither 3.6GSPS interleavedor1800 MSPS dual ADC

New DESCLKiQ Mode for high bandwidth,high sampling rateapps

■Pin-compatible with ADC1xD1x00,ADC12Dx00RF

■AutoSync feature for multi-chip synchronization

■Internally terminated,buffered,differential analog inputs Interleaved timing automatic and manual skew adjust

Test patterns at output for system debug

Time Stamp feature to capture external trigger

■Programmable gain,offset,and $t _ { A D }$ adjust feature

■1:1 non-demuxed or 1:2 demuxed LVDS outputs

图 27 ADC12D1800RF 幅频响应特性

2)动态性能指标

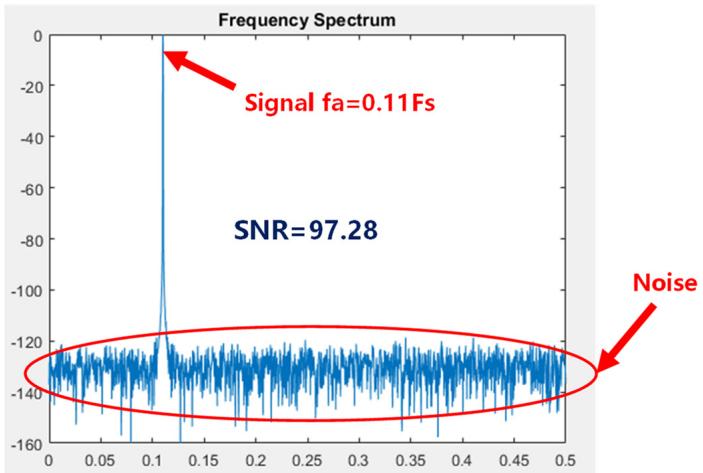

○1 信噪比(SNR)

指 ADC 输入单音正弦信号时,信号的功率与 Nyquist 带宽内的其它频率分量(不包括直流和谐波分量)的总功率之比。增加 FFT 的点数能够提升频率分辨率。能够降低噪底,提高微弱信号检测能力。

$$ S N R = 1 0 \cdot \log _ { 1 0 } \left( \frac { S i g n a l P o w e r } { N o i s e P o w e r } \right) $$

图 28 基于 ADC 输出频谱计算 SNR

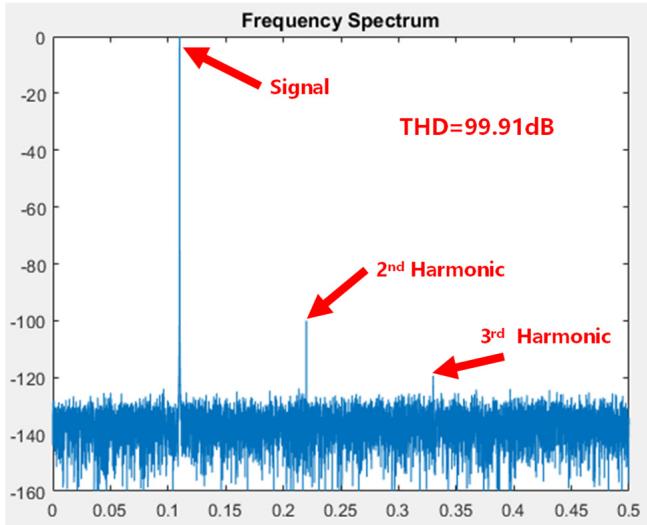

○2 总谐波失真比(THD)

总谐波失真是输入信号与系统所有谐波的总功率比,它可以表征系统非线性的强度。ADC 的谐波失真来源于:量化器的积分非线性( INL )和差分非线性(DNL);运算放大器;以及采保电路。

$$ T H D = 1 0 \cdot \log _ { 1 0 } { \left( \frac { S i g n a l P o w e r } { D i s t o r t i o n s P o w e r } \right) } $$

图 29 基于 ADC 输出频谱计算 THD

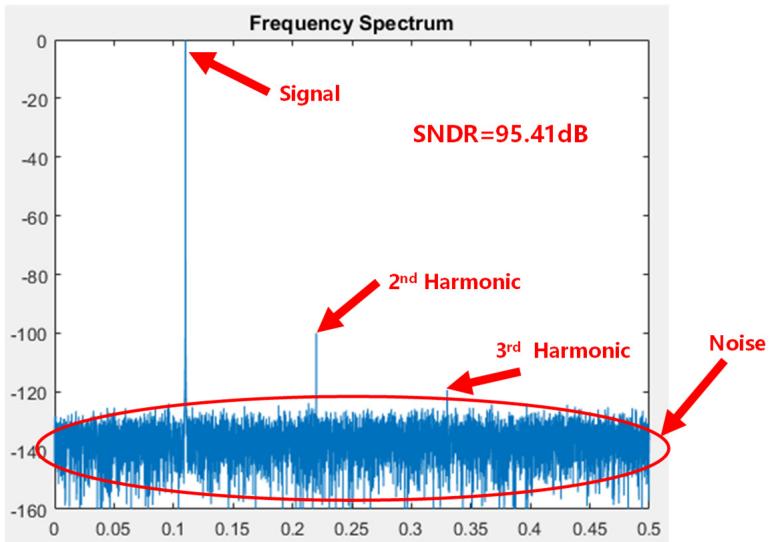

$\textcircled{3}$ 信噪失真比(SNDR)

又称 SINAD。指 ADC 输入单音正弦信号时,信号功率与 Nyquist 带宽内的全部其它频率分量(包括谐波分量,不包括直流分量)的总功率之比。

$$ S N D R = 1 0 \cdot \log _ { 1 0 } { \left( { \frac { S i g n a l P o w e r } { N o i s e P o w e r + D i s t o r t i o n s P o w e r } } \right) } $$

图 30 基于 ADC 输出频谱计算 SNDR

SNR 衡量 ADC 的噪,THD 衡量 ADC 的谐波失真,SNDR 衡量噪声和谐波共同的影响。已知任意两个,就可以确定第三个。

$$ S N R = 1 0 \log _ { 1 0 } { \left( { \frac { S } { N } } \right) } = - 1 0 \log _ { 1 0 } { \left( { 1 0 } ^ { - { \frac { S N D R } { 1 0 } } } - { 1 0 } ^ { - { \frac { T H D } { 1 0 } } } \right) } $$

$$ T H D = 1 0 \log _ { 1 0 } { \left( { \frac { S } { D } } \right) } = - 1 0 \log _ { 1 0 } { \left( { 1 0 } ^ { - { \frac { S N D R } { 1 0 } } } - { 1 0 } ^ { - { \frac { S N R } { 1 0 } } } \right) } $$

$$ S N D R = 1 0 \log _ { 1 0 } { \left( { \frac { S } { N + D } } \right) } = - 1 0 \log _ { 1 0 } { \left( { 1 0 } ^ { - { \frac { S N R } { 1 0 } } } + { 1 0 } ^ { - { \frac { T H D } { 1 0 } } } \right) } $$

$\textcircled{4}$ 有效位数(ENOB)

有效位数 ENOB 是在 ADC 器件 SNR 或 SNDR 的基础上计算出来的,它将传输信号质量转换为等效比特分辨率。实际上系统噪声使输出信号失真,失真大小就反映在信噪比上。ADC 的分辨率可以用来计算给定器件的理论信噪比,反过来也成立,所以器件的信噪比测量值也可用来计算有效器件比特分辨率。故 ENOB 是考虑了所有噪声源和 ADC 的各种误差合在一起综合作用的结果。

一个理想的 N 位 ADC 模块(仅考虑量化误差)的信噪比可以由 SNR 的电压形式推导得到,即:

$$ S N R = 6 . 0 2 \cdot N + 1 . 7 6 d B $$

实际测量到的 ADC 的信号和噪声谐波失真比 SNDR,并用其来计算有效位数(ENOB),这样可表征实际 ADC 性能,即:

$$ E N O B = \frac { S N D R - 1 . 7 6 } { 6 . 0 2 } b i t $$

由此可知,当 ADC 的总谐波失真功率(THD)一定时,有效位数 ENOB 取决于噪声功率;ADC 的 SNR 越高,其有效位数 ENOB 就越高。

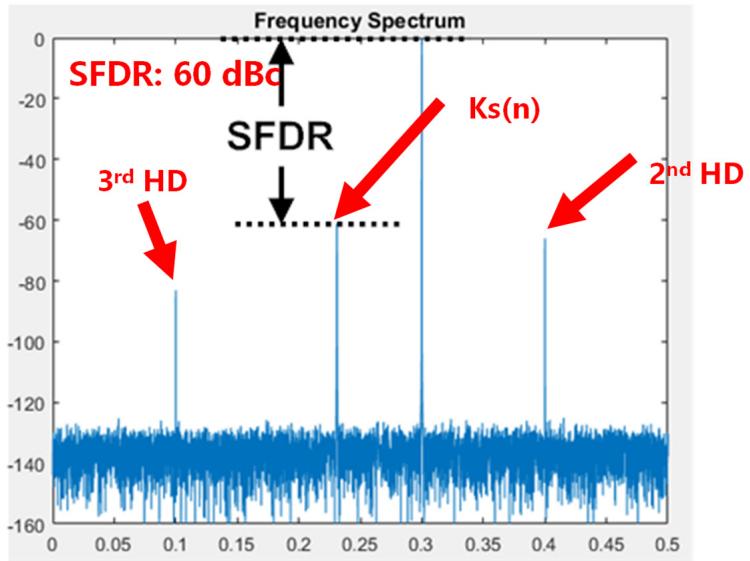

$\textcircled{5}$ 无杂散动态范围(SFDR)

无杂散动态范围能对系统线性度进行量化,它是信号功率与杂波功率最大值的数量差。杂波通常产生于各谐波中,它表示器件输入和输出之间的非线性。

图 31 基于 ADC 输出频谱计算 SFDR

3)综合评价指标

FOM(Figure of Merit),一般通过 FOM 对比不同类型 ADC 的能效,其定义为

$$ \mathrm { F O M } = \frac { \mathrm { P o w e r } } { \mathrm { m i n } \left{ \mathrm { f _ { s } } , 2 \times \mathrm { E R B W } \right} \times 2 ^ { \mathrm { E N O B } } } $$

其中,fs 表示采样速率,ENOB 表示有效带宽对应的有效位数,ERBW 是有效输入带宽。

4)动态性能测试方法

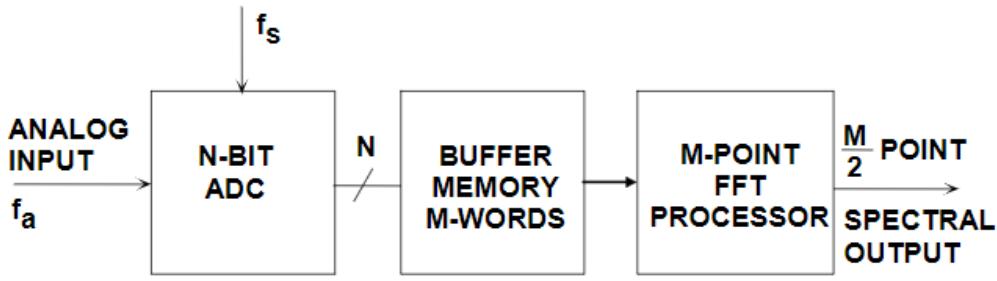

ADC 动态性能的测试方法可以分为以下三个步骤, $\textcircled{1}$ 以 Fs 为采样率,缓存 M 点采样样本。 $\textcircled{2}$ 进行 FFT 运算,得到 M 点复数序列。 $\textcircled{3}$ 根据上述指标定义计算 SNR、SNDR、THD、SFDR 等动态性能

图 32 动态性能测试方法流程

图 33 Matlab 计算程序参考

7.3 影响性能的因素分析

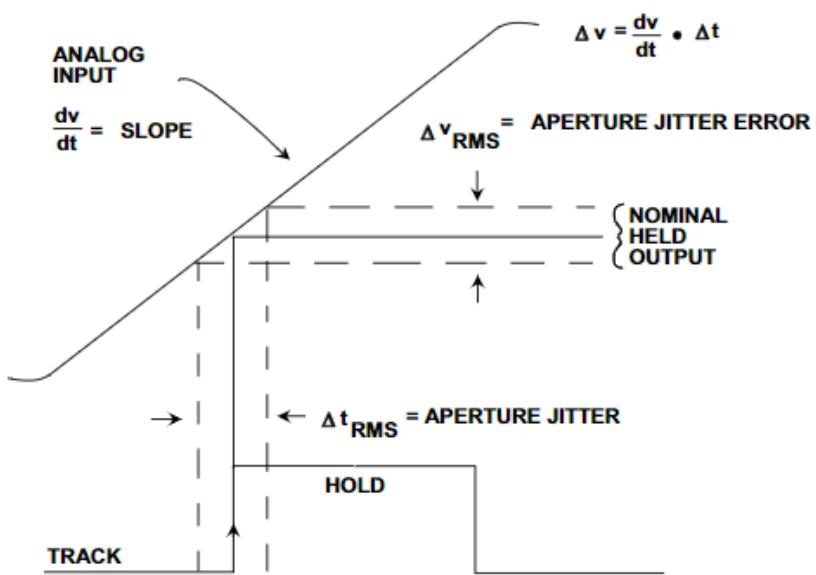

以采样时钟的孔径抖动为例,详细分析抖动tj对ADC输出信噪比的影响。孔径延迟不产生误差(假设它比保持时间要短),但会在采样时钟输入或模拟输入(取决于其符号)中起固定延迟作用。然而,在“交错”ADC、同步采样应用或直接I/Q解调中,两个或更多 ADC 必须精密匹配,不同转换器之间的孔径延迟差异可能会给高压摆率信号带来误差。在这些应用中,必须适当调整采样时钟相对于 ADC 的相位,从而消除孔径延迟不匹配问题。然而,如果孔径延迟中存在样本间变化(“孔径抖动”),则会产生相应的电压误差,如下图所示。在开关断开的时刻,这种样本间变化称为“孔径不确定性”或“孔径抖动”,通常用均方根皮秒(ps rms)来衡量。相应输出误差的幅度与模拟输入的变化速率有关。针对既定的孔径抖动值,孔径抖动误差随着输入 dv/dt 提高而提高。相位抖动对外部采样时钟(或模拟输入)的影响也是产生同样类型的误差。因此,总抖动量为外部采样时钟抖动与ADC孔径抖动的方和根。

图34 孔径抖动对采样保持电路的影响

孔径抖动和采样时钟抖动对ADC信噪比(SNR)的影响。通过下面的简单分析,可以预测孔径和采样时钟抖动对理想ADC SNR的影响。假设输入信号由下式给出:

$$ \nu \big ( t \big ) = V _ { 0 } \sin \big ( 2 \pi f t \big ) $$

该信号的变化速率由下式给出:

$$ \frac { d \nu } { d t } { = } 2 \pi f V _ { \mathrm { 0 } } \cos \left( 2 \pi f t \right) $$

将幅度 $2 \pi f V _ { 0 }$ 除以可以获得 $d \nu / d t$ 的均方根值:

$$ \frac { d \nu } { d t } { = } \frac { 2 \pi f V _ { 0 } } { \sqrt { 2 } } $$

现在令 $\Delta \nu _ { _ { r m s } } =$ 均方根电压误差, $\Delta t =$ 均方根孔径抖动 $t _ { j }$ ,并将这些值代入上式,可得

$$ \frac { \Delta \nu _ { r m s } } { t _ { j } } = \frac { 2 \pi f \mathcal { V } _ { 0 } } { \sqrt { 2 } } $$

进而可得

$$ \Delta \nu _ { r m s } = \frac { 2 \pi f V _ { 0 } t _ { j } } { \sqrt { 2 } } $$

满量程输入正弦波的均方根值为 $V _ { 0 } / \sqrt { 2 }$ ,因此均方根信号与均方根噪声的比值(用 dB 表示)为:

$$ S N R = 2 0 \log _ { 1 0 } \left[ \frac { V _ { 0 } / \sqrt { 2 } } { \Delta \nu _ { m s } } \right] = 2 0 \log _ { 1 0 } \left[ \frac { V _ { 0 } / \sqrt { 2 } } { 2 \pi f V _ { 0 } t _ { j } \sqrt { 2 } } \right] = 2 0 \log _ { 1 0 } \left[ \frac { 1 } { 2 \pi f t _ { j } } \right] $$

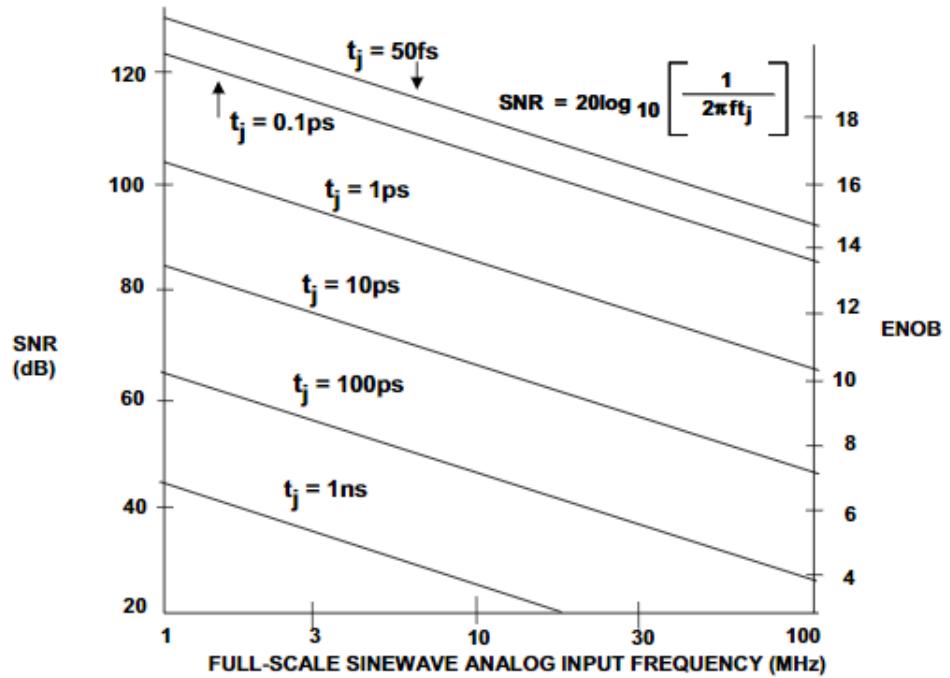

该公式假设 ADC 具有无限的分辨率,孔径抖动是决定 SNR 的唯一因素。下图给出了该公式的图形,它说明孔径和采样时钟抖动对SNR和ENOB有严重影响,特别是当输入/输出频率较高时。例如,当对一个 $1 0 0 M H z$ 的信号进行采样时,为了实现14

位 SNR 性能,孔径抖动必须小于 0.1ps。目前可提供典型孔径抖动规格为 60 fs rms的 ADC(AD9445 14 位 125 MSPS 和 AD9446 16 位 100 MSPS)。必须特别注意降低采样/重构时钟的相位噪声,以免 ADC 本身固有的性能下降。

图 35 抖动引起的 ADC 的 SNR 和 ENOB 与输入频率的关系

7.4 带通采样应用举例

1)带通采样定理

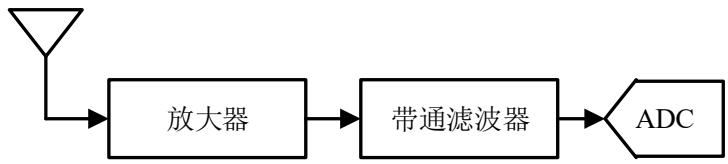

实际中遇到的许多信号是带通型信号,这种信号的带宽往往远小于信号中心频率。若带通信号的上截止频率为 $f _ { H }$ ,下截止频率为 $f _ { L }$ ,这时并不需要采样频率高于两倍上截止频率 $f _ { H }$ ,可按照带通采样定理确定采样频率。与低通采样不同,带通采样能够有效降低系统对采样速率的要求,从而能够降低后端数据处理的要求。带通采样系统的电路级结构如下所示,通常在 ADC。

图36 带通采样系统组成

带通采样速率要求的分析推导如下。首先带通采样定理定义为:一个频带限制在 $\left( f _ { L } , f _ { H } \right)$ 内的时间连续信号 $x { \big ( } t { \big ) }$ ,信号带宽 $B = f _ { H } - f _ { L }$ ,令 $M = f _ { \scriptscriptstyle H } / B - N$ 这里 $N$ 为不大于 $f _ { H } / B$ 的最大正整数。如果采样频率 $f _ { s }$ 满足条件

$$ { \frac { 2 f _ { H } } { m + 1 } } \le f _ { s } \le { \frac { 2 f _ { L } } { m } } 0 \le m \le N - 1 $$

则可以由抽样序列无失真的重建原始信号 $x { \big ( } t { \big ) }$ 。

这里 $m$ 是大于等于零的一个正数。如果 $m$ 取零,则上述条件化为

$$ f _ { s } \geq 2 f _ { { \scriptscriptstyle H } } $$

这时实际上是把带通信号看作低通信号进行采样。

而 $m$ 取得越大,则符合的采样频率会越低。但是 $m$ 有一个上限,因为 $f _ { s } \leq { \frac { 2 f _ { L } } { m } }$ 而为了避免混叠,延拓周期要大于两倍的信号带宽,即 $f _ { s } \geq 2 B$ 。

因此

$$ m \leq \frac { 2 f _ { L } } { f _ { s } } \leq \frac { 2 f _ { L } } { 2 B } = \frac { f _ { L } } { B } $$

由于 $N$ 为不大于 $f _ { H } / B$ 的最大正整数,因此不大于 $f _ { L } / B$ 的最大正整数为$N { - } 1$ ,故有 $0 \leq m \leq N - 1$ 。

作为一个特例,我们考虑 $f _ { H } = N B$ ( $N > 1$ )的情况,即上截止频率为带宽的整数倍。若按低通抽样定理,则要求抽样频率 $f _ { s } \geq 2 N B$ ,抽样后信号各段频谱间不重叠,采用低通滤波器或带通滤波器均能无失真的恢复原始信号。根据带通抽样,若将抽样频率取为 $f _ { s } \geq 2 B$ ( $m$ 取为 $N { - } 1$ ),抽样后信号各段频谱之间仍不会发生混叠。采用带通滤波器仍可无失真地恢复原始信号,但此时抽样频率远低于低通抽样定理 $f _ { s } = 2 N B$ 的要求。

2)航天测控中频信号采集系统应用举例

对于本实验课程所涉及的航天测控系统中数传基带信号的特征如下

$\bullet$ 中频 70MHz

$\bullet$ 信号带宽±10MHz

$\bullet$ 信号幅度:-60 dBm~0 dBm

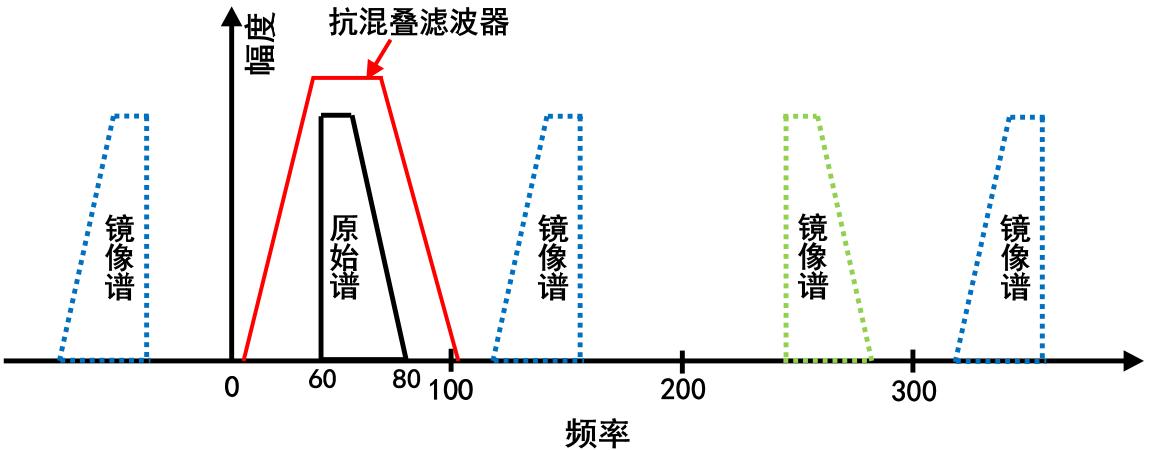

输入信号中频位于 70MHz,最大带宽不超过 $2 0 M H z$ ,则可知信号的分布范围60MHz~70MHz。如果我们按照低通采样模式,根据奈奎斯特采样定理可知,能够无混叠的还原出原始信号的最低采样率为输入信号带宽的两倍,即 $2 { \ast } 7 0 { = } 1 4 0 \mathsf { M s p s } .$ 。考虑信号调理电路中滤波器过渡带的设计需要,通常需要预留 $20 \sim 3 0 %$ 的余量,将采样率设置 200Msps,采样结果的频谱示意图如下所示

图 37 低通采样模式的输出频谱示意图

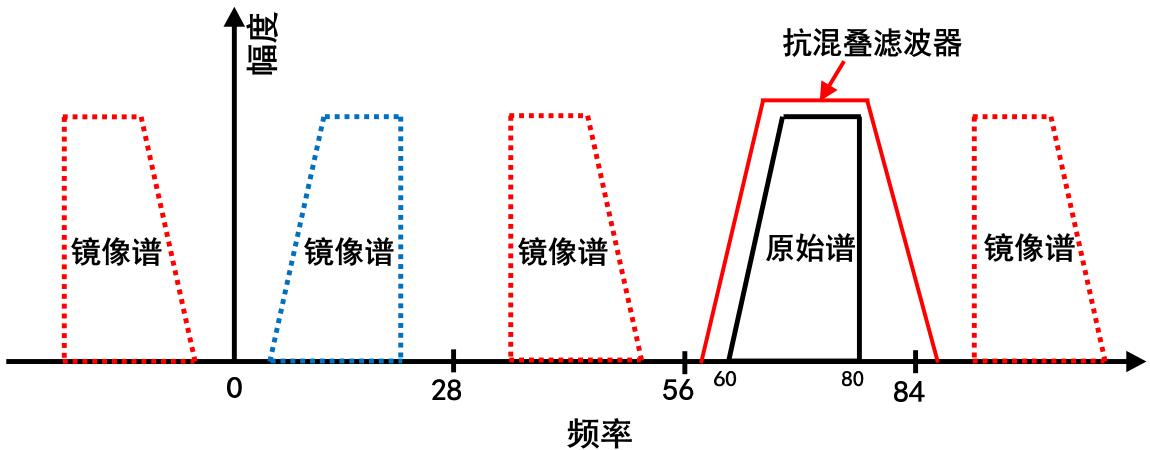

更为高效的方法是采用带通采样模式,根据前面推导的带通采样速率计算公式,同时考虑信号调理电路中滤波器过渡带的设计需要,将采样率设置56Msps,采样结

果的频谱示意图如下所示

图38 带通采样模式的输出频谱示意图

这时我们利用的是 ADC 的第 3 奈奎斯特带,经过时域离散化之后,在第 1 奈奎斯特带内的频谱与原始信号谱具有相同的分布特征,这与第 2 奈奎斯特带通采样不同。通过这种方式,可以将采样速率降低 4 倍,这意味着对传输接口和缓存空间的要求都可以大幅度降低,从而更加高效的满足系统应用的要求。故之前设计的AD9226 的单元电路能够满足该项目需求,沿用之前的硬件系统即可。

8. 实验报告要求

实验报告需要反映以下工作:

1) 实验目的

描述每次实验课程的具体实验目标。

2) 实验方案与步骤

描述实验方案的分析设计过程和实验具体步骤,包括设计思想、结构框图、工作原理、参数计算等。

3) 实验数据

包括实验过程中产生的设计原理图、PCB 版图、仿真结果、测试数据、实物测试照片、结果分析对比情况等。

4) 实验总结

阐述设计中遇到的问题、原因分析及解决方法,分享实验的收获、体会及展望。

5) 参考文献

9. 考核要求与方法

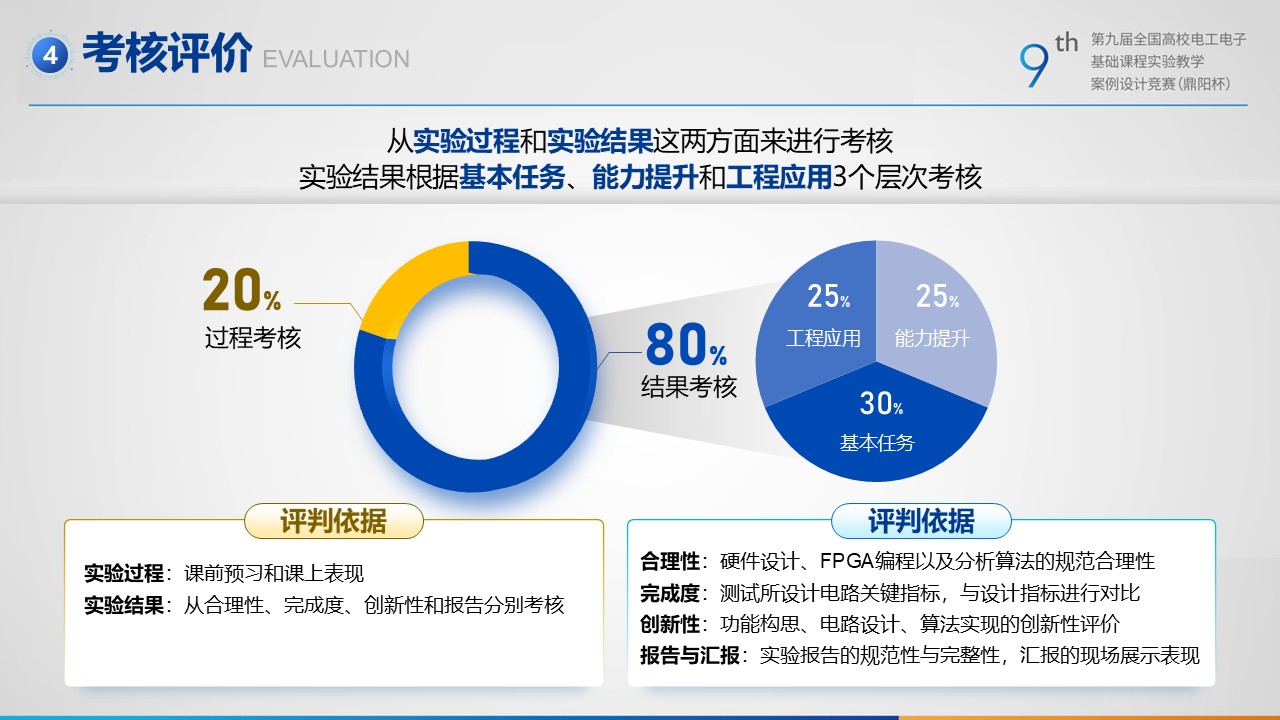

对学生的考核主要从实验过程和实验结果这两方面来进行考核。

| 考核内容 | 具体考核项 | 考核方式 | 分值占比 |

| 实验过程 | 课前预习情况 | 授课老师通过课上雨课堂测试,课前提问情况给出评分。 | 20% |

| 课上表现 | 授课教师根据到课率、回答问题、积极程度等给出综合评价。 | ||

| 实验结果(基本任务部分) | 合理性 | 授课老师从硬件设计、FPGA 编程以及分析算法的规范合理性等综合评分。 | 30% |

| 完成度 | 授课老师现场测试所设计电路关键指标,与设计指标进行对比给出评分。 | ||

| 创新性 | 授课老师从功能构思、电路设计的创新性,实现电路的经济性等方面给出综合评分。 | ||

| 实验报告与汇报 | 授课老师从实验报告的规范性与完整性,汇报的现场展示表现等方面给出综合评分。 | ||

| 实验结果(能力提升部分) | 从合理性、完成度、创新性和报告分别考核 | 方式同上。 | 25% |

| 实验结果(工程应用部分) | 从合理性、完成度、创新性和报告分别考核 | 方式同上。 | 25% |

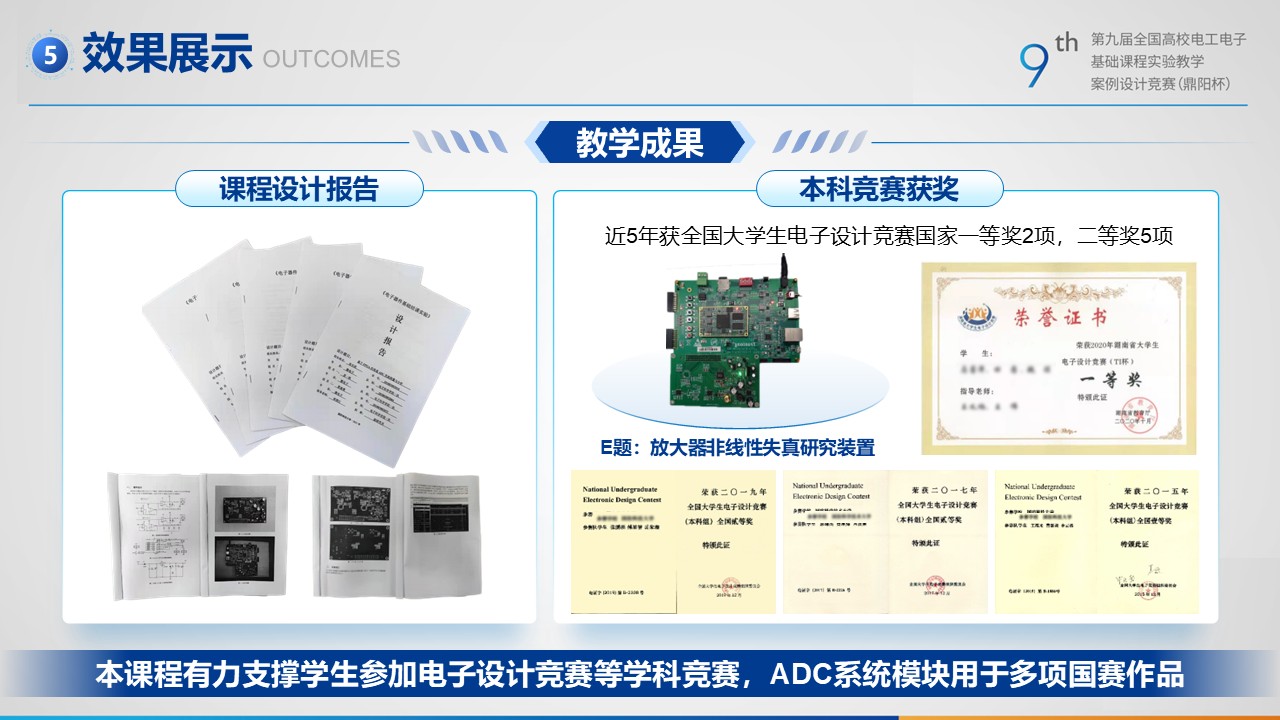

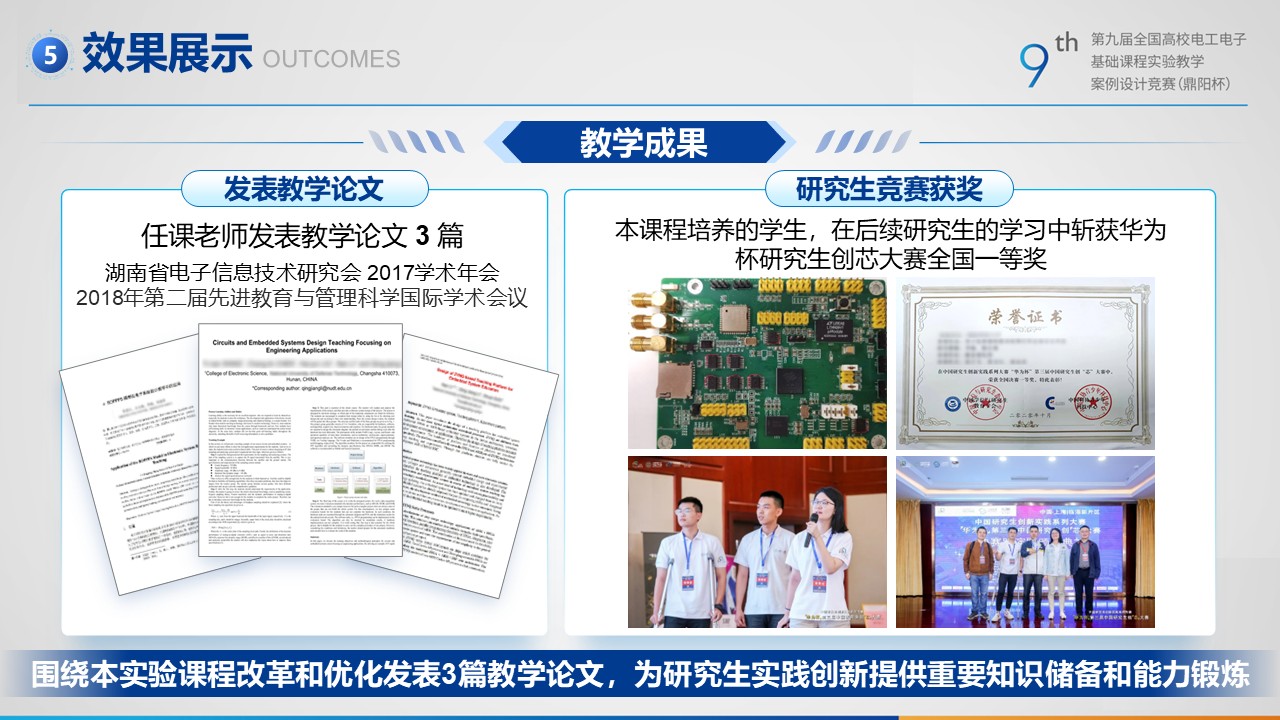

10.项目特色或创新

项目的特色在于:以工程实践项目为牵引,将电路分析、模电、数电、集成电路设计与工艺等专业骨干课程中所学的知识和理论融合到整个实验课程中,实现知识的融会贯通,完成技术进阶,提升学员解决实际问题能力,培养系统设计思维。通过挑战发挥部分,激发创新和进取意识。通过分工协作培养团队合作意识。

1. 教学大纲、简介及实验计划书

《电子器件基础》课程教学大纲

(执笔人:李清江 王义楠审阅学院:电子科学学院)

课程编号:170314011

英文名称:Fundamentals ofElectronic Components and Devices

预修课程:固体物理,半导体物理,模拟电子技术,数字电路与逻辑设计。

学时安排:40学时,其中讲授32学时,实践8学时。

学分:2.5

课程性质:专业选修课

开课学期:春3

一、课程性质地位

本课程是本科阶段电子技术知识与技能的学科基础课程。课程讲授电子器件的发展现状与趋势,现代电子系统各组成部分所涉及的主要电子器件的原理功能、性能指标和典型应用电路。使学生从应用需求出发,对电子器件有一个系统、全面的认识,能够综合运用所学电子器件知识进行应用电路的设计和分析,培养学生的创新思维、工程素养和解决实际问题的能力。课程学习为以后深入学习电子技术及其在专业中的应用打好基础。

二、课程目标

通过本课程的教学及实践,学生应具备的知识与能力目标如下。

(一)课程知识目标

本课程的知识目标主要包括以下知识单元,即电子器件绪论、传感器件、信号调理器件、数据转换器件、新原理信息存储与处理器件,学员应熟悉、了解或掌握不同知识单元的具体内容,达成课程标准的相应内容。

具体知识目标的分解如表1所示。

(二)课程能力目标

本课程要发展的能力目标对应在培养方案中对应的一级能力目标:4 围绕联合作战保障、装备技术保障、新型作战力量的构思-设计-实施-运行全系统的工程综合能力,二级能力目标为:4.5 实施系统建构,而三级能力目标则区分为设计实施过程、硬件制造过程、硬、软件集成等三个方面。

三、教学方法

通过课堂教学,组织讨论,案例讲解,课后作业,作业讲解与讨论,课内实践一系列的环节使学员达到预期学习目标,具体包括理论讲授,互动研讨,问题讲解,答疑解惑等环节。

本课程采用理论教学、网络教学、EDA教学相互交叉融合的结构。理论教学强调系统性和基础性,精讲多练,启发引导,留有余地,归纳总结;网络教学开展讨论,自主学习,交流互动,举一反三,活跃气

三级能力4.5.4:硬、软件集成

掌握程度:

初始程度:L1,要求程度:L4

学习目标:

能够基于电子器件原理、性能学习,进行典型应用电路设计与实现。

学习实现环节:

课程讲解+研讨实践+综合实验

五、课程学习内容与时间节点

按照章节和模块说明本课程的内容要点及课内学时数,其中章节为顺序编号,不一定与所用教材一致。如下表3所示。

| 章节 | 内容 | 课内学时数 |

| 绪论 | 课程定位、内容、授课方式简介 | 1 |

| 第一章 | 电子器件导论 | 1 |

| 第二章 | 传感器件 | 8 |

| 第三章 | 信号调理器件 | 10 |

| 第四章 | 数据转换器件 | 8 |

| 第五章 | 新原理信息存储与处理器件 | 4 |

| 实验 | 内容 | 课内学时数 |

| 综合设计实验 | 高速ADC 性能测量与分析 | 8(配套12课外学时) |

| 合计 | ||

| 40 | ||

六、课程综合计分方法

(一)考核结构设计与各教学环节比例分配

考核方式:考试与考查相结合

组织方式:笔试/现场测试,笔试部分采用闭卷形式

成绩评定:百分制

记分标准:课程考试占 $60 %$ ,综合设计实验(含实验成绩和平时作业)占 $40 %$

(二)评分标准

采用百分制进行评分,最后综合评分进行相应比例折算。评分标准如下表4所示。

表4平时作业评分标准

| 完成情况 | 得分 |

| 严格按照作业要求并及时完成,基本概念清晰,解决问题的方案正确、合理, 能提出不同的解决问题方案 | 80-100分 |

《电子器件基础》课程简介

课程编号:170314011

课程名称 (英文):Fundamentals of Electronic Components and Devices学时安排:40学时,其中讲授32学时,实践8学时。预修课程:固体物理,半导体物理,模拟电子技术,数字电路与逻辑设计。

内容简介:

本课程主要讲授电子器件的发展现状与趋势,现代电子系统各组成部分所涉及的主要电子器件的原理功能、性能指标和典型应用电路,学习掌握从应用需求出发,综合运用所学电子器件知识进行应用电路的设计和分析的方法。随着微电子技术的快速发展和广泛应用,电子器件在军用、民用电子信息系统中起着核心支撑作用。因而,本课程具有很强的实用性,学员通过本课程的学习,将对现代电子器件有一个系统、全面的认识,建立面向实际应用系统需求进行电子器件设计与应用的硬件思维方式,培养学生的创新思维、工程素养和解决实际问题的能力。

《电子器件基础》实验教学计划

(执笔人:李清江 王义楠审阅学院:电子科学学院)

课程编号:170314011

课程名称:电子器件基础

总学时:40学时

实验学时:8学时

实验地点:电子科学学院-工程实验中心

一、任务背景与目标

(一)任务背景描述

本课程实验室基于《电子器件基础》课程特点而设置,目的是为了锻炼学生的实践动手能力,加深对电子器件及其相关理论知识的感性认识,从而为今后从事电子器件的设计、应用研究打下工程实践能力基础。

实验教学以讲授式、启发式、讨论式与实际操作实验相结合,以增强学生的理论与实践相结合的能力,提高基本操作技能与电子器件分析、测试与应用开发等综合能力。在整个实验教学过程中,以学生为主,充分调动学生学习的积极性,3人一组,协作讨论研究,组队发现并解决问题,培养学生独立工作作风和团结互助的团队协作精神。

(二)技术目标

1)了解ADC的工作原理与分类,熟悉ADC的主要技术指标,掌握基本指标和动态指标的测量方法。2)掌握ADC的选型,信号调理、采样时钟以及输出接口等外围电路设计方法。掌握ADC单元电路设计和调试方法。3)掌握FPGA控制程序的编程和在线调试方法。掌握影响ADC性能因素的分析方法。

(三)能力目标

通过综合性实验案例设计,我们希望实现下述教学目标:

1)促进专业知识体系的构建和整合。通过实验设计分析过程,将电路分析、模电、数电、集成电路设计与工艺等专业骨干课程中所学的知识和理论运用到实际电路设计项目之中,实现知识的融会贯通和技术进阶。

2)锻炼学生的工程素养和实践能力。学生能够亲身体验电子系统设计全流程,在实际工程中锻炼发现问题、分析问题和解决问题的能力,从而真正达到“以用促学,学以致用”。

3)激发学生的创新意识和团队精神。通过设计能力提升和工程应用两个发挥部分,鼓励学有余力的学员挑战更高难度,激发学生创新和进取意识。通过分工协作模式培养团队意识和合作精神。

4)塑造学生的工匠精神和爱国情怀。在实验课程的教学全过程融入工匠精神和爱国情怀教育,将执着

2. 实施课表

2021年春季学期本科学员课程表

2018级(无军籍)微电子科学与工程

制表日期:2021-02

| 学期 | 周 | 星期 | 星期 | 备注 | |||||||||||||||||

| 日期/节次 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | |||

| 中 | 1 | 02.03-02.09 | 雷达原理 | 军事技能 | 嵌入式 | 电子器件 | 模式识别 | 军事技能 | 嵌入式 | 电子器件 | 雷达原理 | 模式识别 | 春季学期第3周星期日1-4节军事技能春季学期第10周星期日1-2节导航原理春季学期第10周星期日3-4节雷达原理春季学期第10周星期日5-6节5G春季学期第12周星期六 5-6节模式识别 | ||||||||

| 2 | 02. 22-02. 28 | 导航原理 | 雷达原理 | 军事技能 | 嵌入式 | 电子器件 | 模式识别 | 导航原理 | 集成电路 | 军事技能 | 嵌入式 | 电子器件 | 雷达原理 | 模式识别 | 集成电路 | ||||||

| 3 | 03.01-03.07 | 导航原理 | 雷达原理 | 军事技能 | 嵌入式 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 军事技能 | 嵌入式 | 电子器件 | 微纳器件 | 雷达原理 | 模式识别 | 集成电路 | ||||

| 4 | 03. 08-03. 14 | 导航原理 | 雷达原理 | 嵌入式 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 嵌入式 | 电子器件 | 微纳器件 | 雷达原理 | 模式识别 | 集成电路 | ||||||

| 5 | 03. 15-03. 21 | 导航原理 | 雷达原理 | 形势政策 | 嵌入式 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 形势政策 | 嵌入式 | 电子器件 | 微纳器件 | 雷达原理 | 模式识别 | 集成电路 | ||||

| 6 | 03. 22-03. 28 | 导航原理 | 雷达原理 | 形势政策 | 嵌入式 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 形势政策 | 嵌入式 | 电子器件 | 微纳器件 | 雷达原理 | 模式识别 | 集成电路 | ||||

| 7 | 03. 29-04. 04 | 导航原理 | 雷达原理 | 5G | 嵌入式 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 5G | 嵌入式 | 电子器件 | 微纳器件 | 雷达原理 | 嵌入式 | 模式识别 | 集成电路 | |||

| 8 | 04. 05-04. 11 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 5G | 嵌入式 | 电子器件 | 微纳器件 | 雷达原理 | 嵌入式 | 模式识别 | 集成电路 | |||||||

| 9 | 04. 12-04. 18 | 导航原理 | 雷达原理 | 5G | 嵌入式 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 5G | 嵌入式 | 电子器件 | 微纳器件 | 雷达原理 | 嵌入式 | 模式识别 | 集成电路 | |||

| 10 | 04. 19-04. 25 | 导航原理 | 雷达原理 | 5G | 嵌入式 | 电子器件 | 微纳器件 | 模式识别 | 导航原理 | 集成电路 | 5G | 电子器件 | 微纳器件 | 雷达原理 | 嵌入式 | 模式识别 | 集成电路 | ||||

| 日 | 04. 26-05. 02 | 导航原理 | 雷达原理 | 5G | 嵌入式 | 专业设计 | 专业设计 | 模式识别 | 导航原理 | 集成电路 | 5G | 嵌入式 | 专业设计 | 专业设计 | 雷达原理 | 模式识别 | 集成电路 | ||||

| 12 | 05.03-05.09 | 专业设计 | 专业设计 | 雷达原理 | 模式识别 | 集成电路 | |||||||||||||||

| 13 | 05.10-05.16 | 导航原理 | 雷达原理 | 5G | 专业设计 | 专业设计 | 模式识别 | 导航原理 | 集成电路 | 5G | 专业设计 | 专业设计 | 光电成像 | 模式识别 | 集成电路 | ||||||

| 14 | 05. 17-05. 23 | 导航原理 | 光电成像 | 5G | 专业设计 | 专业设计 | 模式识别 | 导航原理 | 集成电路 | 5G | 专业设计 | 专业设计 | 光电成像 | 模式识别 | 集成电路 | ||||||

| 15 | 05. 24-05.30 | 光电成像 | 5G | 专业设计 | 专业设计 | 集成电路 | 5G | 专业设计 | 专业设计 | 光电成像 | 集成电路 | ||||||||||

| 16 | 05. 31-06. 06 | 光电成像 | 专业设计 | 专业设计 | 光电成像 | 专业设计 | 专业设计 | 光电成像 | 集成电路 | ||||||||||||

| 17 | 06. 07-06. 13 | 光电成像 | 专业设计 | 专业设计 | 光电成像 | 专业设计 | 专业设计 | 光电成像 | |||||||||||||

| 18 | 06. 14-06. 20 | 节假日 | 专业设计 | 专业设计 | 光电成像 | 光电成像 | |||||||||||||||

| 19 | 06. 21-06. 27 | 光电成像 | 光电成像 | 光电成像 | |||||||||||||||||

| 20 | 06. 28-07. 04 | ||||||||||||||||||||

| 课程名称 | 简称 | 学时 | 授课教员 | 授课地点 | 课程名称 | 简称 | 学时 | 授课教员 | 授课地点 | ||||||||||||

| 形势与政策 | 形势政策 | 64 | 鞠晓生副教授 | 305-509 | 光电成像与探测 | 光电成像 | 32 | 杨俊刚副教授 | 305-509 | ||||||||||||

| 微纳电子器件 | 微纳器件 | 32 | 刘森副教授 | 301-304 | 军事技能(二) | 军事技能 | 16 | 曾皓 | 田径场 | ||||||||||||

| 大学生职业发展与就业创业指导2 | 职业发展 | 16 | 李楠副教授 | 302-306 | 集成电路设计与工艺 | 集成电路 | 56 | 陈长林副研究员 | 305-406 | ||||||||||||

| 5G与未来通信 | 5G | 32 | 刘伟副教授 | 305-509 | 导航原理与系统 | 导航原理 | 48 | 刘小汇研究员 | 305-402 | ||||||||||||

| 嵌入式系统原理与设计 | 嵌入式 | 48 | 于红旗副教授 | 305-509,电子技术实验室 | 人工智能与模式识别 | 模式识别 | 56 | 陈浩副教授 | 305-509 | ||||||||||||

| 微电子科学与工程专业设计 | 专业设计 | 56 | 李楠副教授 | 微电子与专用集成电路实验室 | 雷达原理 | 雷达原理 | 48 | 赵锋副教授 | 305-509 | ||||||||||||

| 电子器件基础 | 电子器件 | 40 | 李清江副研究员 | 305-205 | |||||||||||||||||

批准人:王雪松 联系人:邵恒电话:503027

2022年春季学期本科学员课程表

2019级电子科学与技术(无军籍)

制表日期:2022-01

| 学 | 周 | 星期 | 星期 | 四 | 星 | 备注 | ||||||||||||||||

| 次 | 日期/节次 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | 5/6 | 7/8 | 1/2 | 3/4 | |||

| 中 | 1 | 02. 21-02. 27 | 军事技能 | 集成电路 | 电子器件 | 微波技术 | 通信原理 | 军事技能 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | ||||||||||

| 2 | 02.28-03.06 | 军事技能 | 集成电路 | 电子器件 | 微波技术 | 通信原理 | 军事技能 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | |||||||||||

| 第11周星期六7-8节雷达原理第11周星期六5-6节通信原理第13-14,17-18周星期日5-8节通信原理第11周星期六3-4节微波技术第13-14,16-19周星期六 5-8节信号设计第6周星期六5-6节集成电路第9周星期日5-6节集成电路第6周星期六1-2节嵌入系统第4-5,7-9,12-14周星期六1-2节职业发展 | ||||||||||||||||||||||

| 3 | 03. 07-03.13 | 军事技能 | 集成电路 | 电子器伴 | 微波技术 | 通信原理 | 军事技能 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | |||||||||||

| 4 | 03. 14–03. 20 | 军事技能 | 集成电路 | 电子器件 | 微波技术 | 通信原理 | 雷达原理 | 军事技能 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | 雷达原理 | |||||||||

| 5 | 03. 21-03. 27 | 嵌入系统 | 集成电路 | 电子器件 | 微波技术 | 通信原理 | 雷达原理 | 嵌入系统 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | 雷达原理 | |||||||||

| 6 | 03. 28-04. 03 | 嵌入系统 | 集成电路 | 通信原理 | 电子器件 | 微波技术 | 通信原理 | 雷达原理 | 嵌入系统 | 集成电路 | 通信原理 | 通信原理 | 微波技术 | 通信原理 | 通信原理 | 电子器件 | 雷达原理 | |||||

| 7 | 04. 04-04. 10 | 嵌入系统 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | 雷达原理 | |||||||||||||||

| 8 | 04. 11–04. 17 | 嵌入系统 | 集成电路 | 电子器伴 | 微波技术 | 通信原理 | 雷达原理 | 嵌入系统 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | 雷达原理 | |||||||||

| 9 | 04. 18-04. 24 | 嵌入系统 | 形势政策 | 集成电路 | 电子器件 | 微波技术 | 通信原理 | 雷达原理 | 嵌入系统 | 形势政策 | 集成电路 | 微波技术 | 通信原理 | 电子器件 | 雷达原理 | |||||||

| 10 | 04.25-05.01 | 嵌入系统 | 形势政策 | 集成电路 | 通信原理 | 电子器件 | 微波技术 | 通信原理 | 雷达原理 | 嵌入系统 | 形势政策 | 集成电路 | 通信原理 | 通信原理 | 微波技术 | 通信原理 | 通信原理 | 电子器件 | 雷达原理 | |||

| 1 | 05.02-05. 08 | 微波技术 | 通信原理 | 电子器件 | 雷达原理 | |||||||||||||||||

| 12 | 05.09-05.15 | 嵌入系统 | 嵌入系统 | 专业设计 | 专业设计 | 集成电路 | 微波技术 | 通信原理 | 雷达原理 | 微纳器件 | 集成电路 | 微波技术 | 通信原理 | 微纳器件 | 雷达原理 | |||||||

| 13 | 05. 16-05. 22 | 嵌入系统 | 嵌入系统 | 集成电路 | 微波技术 | 通信原理 | 雷达原理 | 微纳器件 | 集成电路 | 微波技术 | 通信原理 | 微纳器件 | 雷达原理 | |||||||||

| 14 | 05. 23–05. 29 | 嵌入系统 | 嵌入系统 | 专业设计 | 专业设计 | 集成电路 | 微波技术 | 通信原理 | 雷达原理 | 微纳器件 | 集成电路 | 微波技术 | 通信原理 | 微纳器件 | 雷达原理 | |||||||

| 15 | 05. 30-06. 05 | 嵌入系统 | 嵌入系统 | 集成电路 | 微波技术 | 通信原理 | 雷达原理 | 微纳器件 | 节 | 日 | ||||||||||||

| 16 | 06. 06-06. 12 | 嵌入系统 | 嵌入系统 | 专业设计 | 专业设计 | 雷达原理 | 微纳器件 | 微纳器件 | 雷达原理 | |||||||||||||

| 17 | 06.13-06.19 | 嵌入系统 | 嵌入系统 | 微纳器件 | 微纳器件 | |||||||||||||||||

| 18 | 06. 20-06. 26 | 工训3 | 工训3 | 专业设计 | 专业设计 | 工训3 | 工训3 | 微纳器件 | 微纳器件 | |||||||||||||

| 19 | 06.27-07.03 | 工训3 | 工训3 | 工训3 | 工训3 | 微纳器件 | 微纳器件 | |||||||||||||||

| 20 | 07.04-07.10 | 工训3 | 工训3 | 专业设计 | 专业设计 | 工训3 | 工训3 | 微纳器件 | 工训3 | 工训3 | ||||||||||||

| 21 | 07. 11-07. 17 | |||||||||||||||||||||

| 一 | 课程名称 | 篇 | 学时 | 授课教员 | 授课地点 | 课和 | 名称 | 称 | 学时 | 授课教员 | 授课地点 | |||||||||||

| 微纳电子器件 | 微纳器件 | 32 | 刘森副教授 | 306-203 | 军事技能(二) | 军事技能 | 16 | 侯春牧副教授 | 第一田径场 | |||||||||||||

| 信号处理课程设计 | 信号设计 | 24 | 韩韬副教授 | 一 | 信号实验室 | 形势与政策 | 形势政策 | 64 | 鞠晓生副教授 | 305-406 | ||||||||||||

| 工程技术训练3 | 工训3 | 1 | 卢耀晖副教授 张萌副教授 | 305-402,金工实习中心 | 电子器件基础 | 电子器件 | 40 | 李清江翻研充员任文楼福研究员 | 302-302.电子技术实验室 | |||||||||||||

| 大学生职业发展与就业创业指导2 | 职业发展 | 16 | 刘继斌教授 | 301-103 | 嵌入式系统原理与设计 | 嵌入系统 | 48 | 于红旗副教授 | 302-108,电子技术实验室 | |||||||||||||

| 通信原理 | 通信原理 | 64 | 黄圣春雷菁黄英 | 302-204,通信工程实验室 | 集成电路设计与工艺 | 集成电路 | 56 | 陈长林副研究员 | 301-204 | |||||||||||||

| 微波技术基础 | 微波技术 | 56 | 柴舜连教授 | 306-204 | 电子科学与技术专业设计 | 专业设计 | 40 | 肖科副教授 | 电波技术实验室 | |||||||||||||

| 雷达原理 | 雷达原理 | 48 | 赵锋副教授 | 301-203 | ||||||||||||||||||

批准人:王雪松 联系人:邵恒

电话:503027

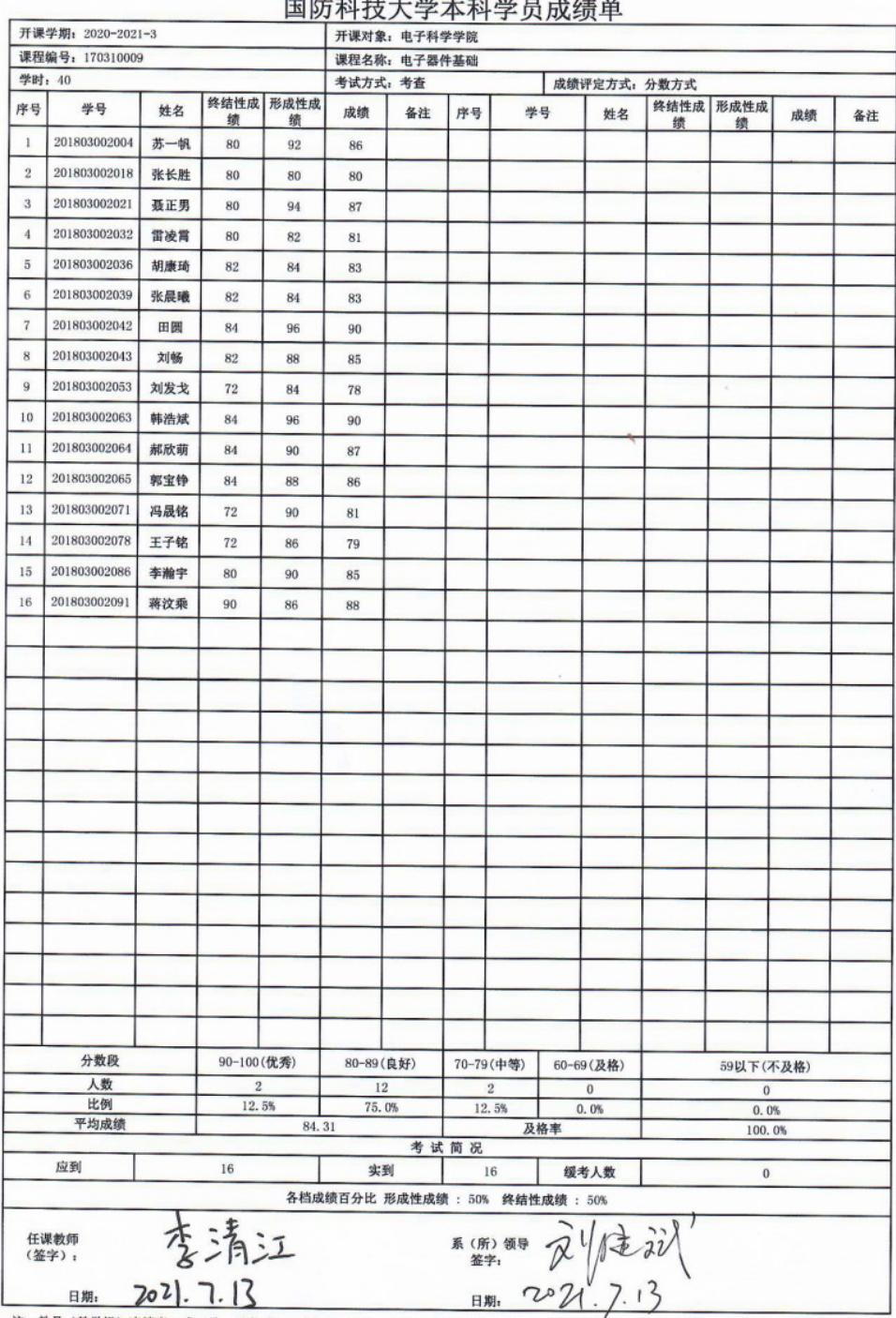

3. 课程成绩单

注:教员(教学组)应填表一式三份,于考后三天内报系(所),经系(所)领导签字后,一份存系(所),一份送学院教学科研工作办公室,一份送学员所在单位,由学院教学科研工作办公室将电子文档提交教务处。

4. 教学现场

5. 实验电路

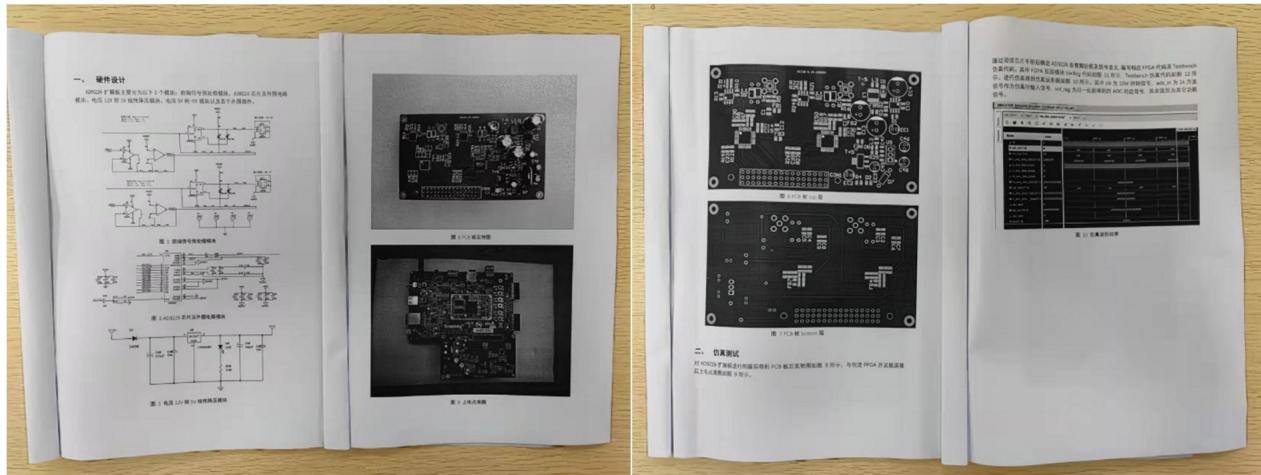

1)ADC 核心电路设计:

AD9226 芯片

前端信号预处理电路

$+ 5 \mathsf { V }$ 转-5V 电路

PCB 板 Top 和 Bottom 层

ADC 采集单元电路

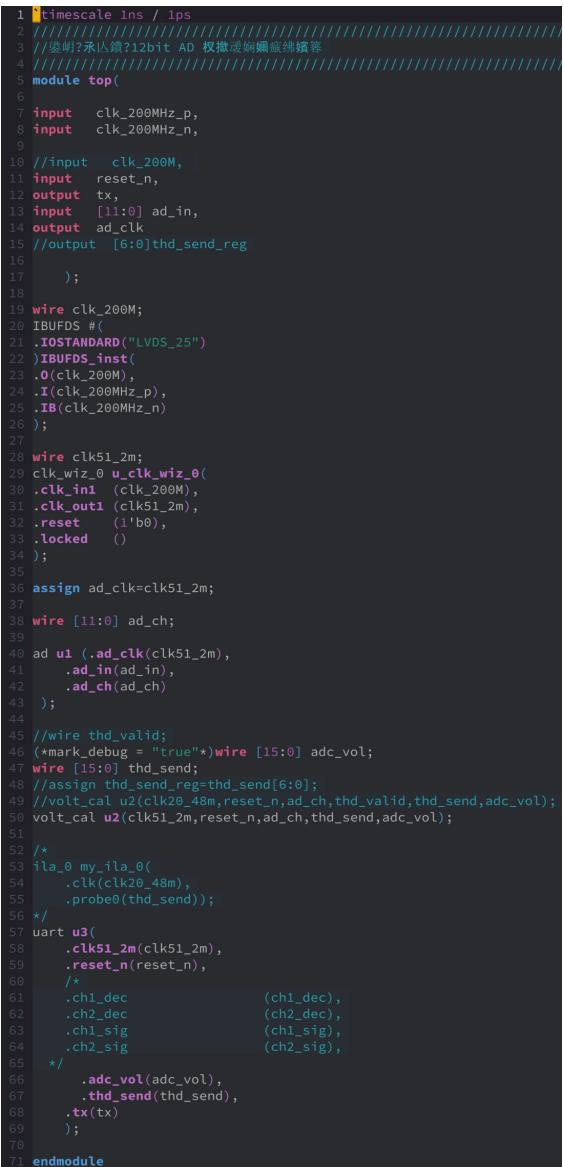

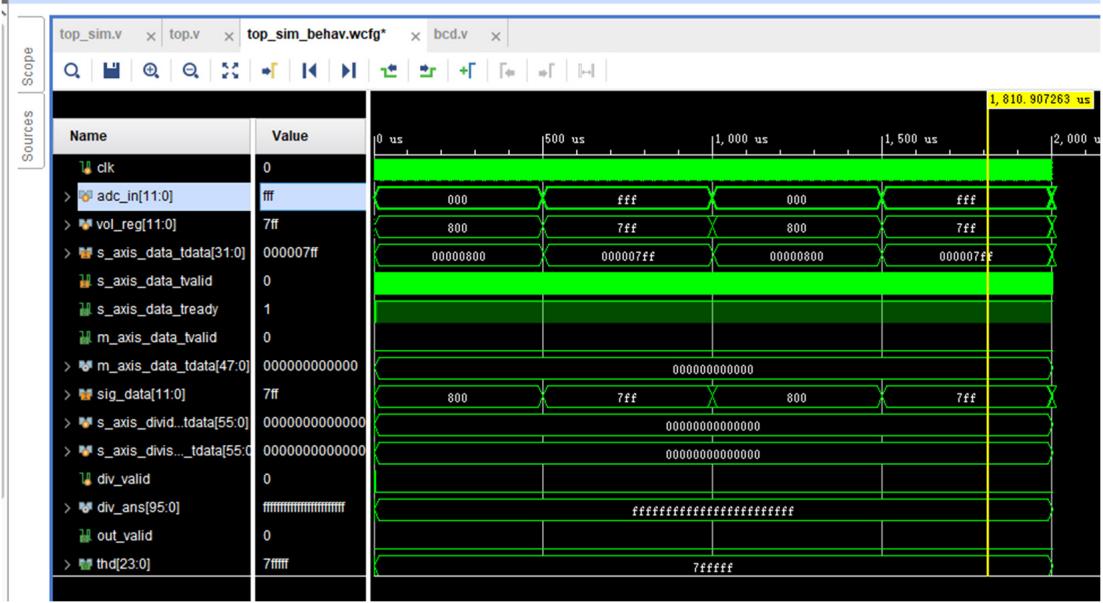

2)FPGA 编程及仿真结果:

timescale 1ns/1ps /1 Company: // Engineer: / Create Date: 2020/10/10 21:54:56 // Design Name: // Module Name: top_sim Project Name: // Target Devices: /1 Tool Versions: // Description: /1 /1 Dependencies: /1 /1 Revision: / Revision 0.01 - File Created /1 Additional Comments: /1 23 module top_sim( ); reg clk,rst; wire tx; reg [12:0] cnt; reg [11:0] adc_in; always #2.5 clk<=~clk; initial begin #0 clk=0; #0 rst=0; #0 cnt=0; //#0 adc_in=12'hffe; #0 adc_in=12'h0; #1000 rst=1; end wire ad_clk; integer now_time; integer vol_in; always #500000 begin //if (adc_in==12'hffe) adc_in=12'h801; //else adc_in=12'hffe; if(adc_in==12'h0o0)adc_in=12'hfff; else adc_in=12'h000; end wire valid[6:0]; wire [6:0] thd_reg; //top my_top(clk,rst,tx,adc_in,ad_clk,thd_reg); topmy_top(clk,rst,tx,adc_in,ad_clk); endmodule

Verilog 代码

SIMULATioN - Behavioral Simulation - Functional- sim_1-top_sim

Modelsim 仿真结果

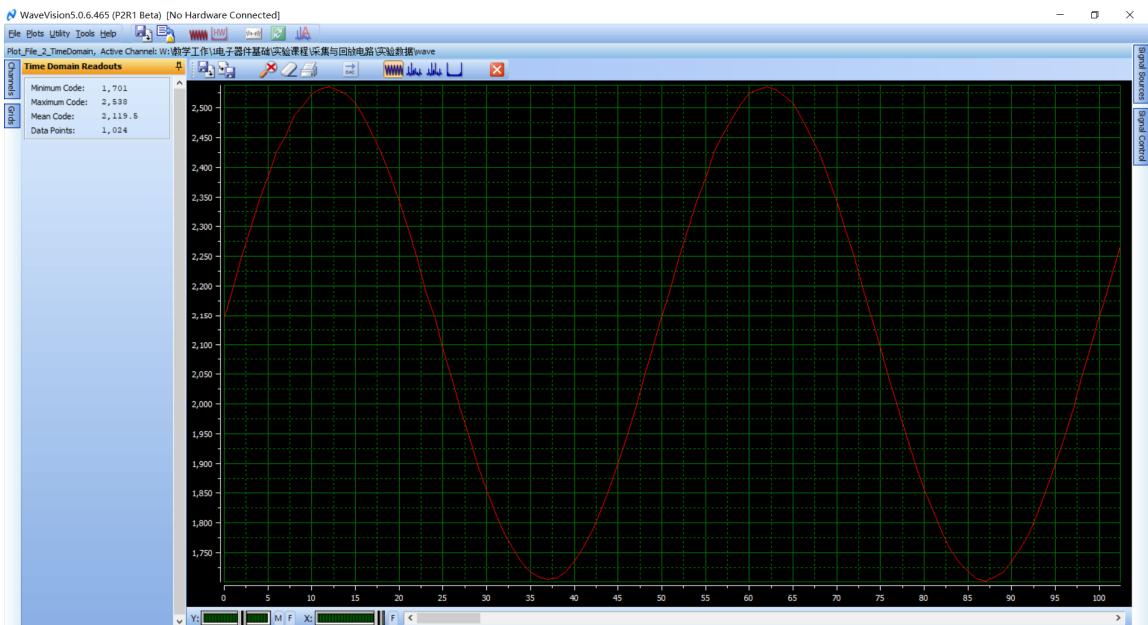

3)WaveVision 的测试结果:

Wavevision 显示的时域波形

Wavevision 显示的动态性能指标

6. 设计报告