基于FPGA的DDS函数发生器设计与实现

课程名称:FPGA技术

实验题目:基于FPGA的DDS函数发生器设计与实现

课程简要信息

课程名称:FPGA技术

课程学时:48

适用专业:电子信息、自动化、通信工程、物联网、电气自动化、生物医学工程等电类专业

学生年级:大学三年级

实验内容与任务(限500字)

函数发生器是各类电子电路测试、分析和研究中不可缺少的测量仪器之一。以现场可编程门阵列FPGA根据DDS(直接数字频率合成)技术实现函数发生器。通过应用FPGA中Verilog HDL语言编程和IP核的调用以及结合D/A转换电路、滤波电路等外围电路,实现频率和相位都可调的三角波、方波和正弦波输出。

基本要求:

-

以Xilinx Spartan6 系列的FPGA开发板作为主要的硬件开发平台,掌握开发板的结构、主要参数指标、板载资源及I/O口分布;

-

设计的函数发生器能输出频率和相位都可调的三角波、方波和正弦波,频率范围为0.1Hz-20MHz,最小步进值为0.1Hz,能实现输出频率的分段控制;

-

利用VHDL或Verilog HDL语言实现DDS信号发生器的频率处理(分频、倍频及频率选择)、按键及消抖、波形存储及波形读取(三角波、方波和正弦波)、频率控制字、相位控制、波形选择和LED灯等多个模块的设计,完成系统的软件仿真;

-

自行设计并制作满足精度、速度要求的D/A转换电路、低通滤波及放大电路等外围模块;

-

实现FPGA开发板与外围电路的接口;

-

信号源输出的波形及参数可通过示波器观察和测量。

实验过程及要求(限300字)

-

学习和理解DDS技术的实现原理及方法;

-

熟悉FPGA开发板Xilinx Spartan6 AX309的结构、主要参数指标、板载资源及I/O口分布;

-

选择合适的软件平台完成DDS信号发生器的频率处理、按键及消抖、波形存储及波形读取、频率控制字、相位控制、波形选择和LED灯等模块的软件仿真;;

-

构思系统的幅值及频率要求,选择合适的数/模转换方式及精度等级,设计出D/A转换电路;

-

设计满足精度要求的滤波及放大电路;

-

实现外围单元电路与开发板的接口;

-

将程序下载到FPGA开发板中,利用示波器对系统进行联合调试;

-

在调试过程中,发现错误并纠正错误,并进行调试过程的详细记录;

-

撰写设计报告,并通过分组演讲,学习交流不同解决方案的特点。

相关知识及背景(限150字)

该实验项目是解决工程实际问题的典型案例,结合了模拟电子技术、数字电子技术、FPGA技术等多方面内容,中间涉及到对FPGA的软件模块设计与实现、FPGA硬件单元调试、数模转换、信号放大、信号滤波、波形显示等多方面的知识与技术方法;并涉及硬件电路的设计、制作、组装、调试及软件编程、优化等问题。

教学目标与目的(限100字)

在实际的工程项目中引导学生掌握利用FPGA技术软件设计硬件化的方法与技巧;掌握DAC、放大电路、滤波电路等硬件单元的特点及实现方法;鼓励学生根据需求寻找不同的解决方案,提高学生的综合设计能力和动手能力。

教学设计与引导

本实验立足于工程实践,需要经历学习研究、方案选择、系统设计、软硬件调试、数据标定、设计总结等过程。在项目开展过程中,应在以下几个方面加强对学生的引导:

-

学习掌握DDS技术的原理及实现方法;

-

查阅资料,拟定采用DDS技术实现函数发生器的不同方案,比较直接利用FPGA器件实现的优缺点;

-

理解系统的性能指标要求,实现相应的软件模块,通过多次仿真验证,优化程序,使其性能达到最佳;

-

实验中需要将FPGA输出的数字信号转换为模拟信号,需要选择精度、速度满足要求的D/A转换器件;

-

D/A转换电路输出的信号还需要被滤波和放大,因此需要设计相应的滤波电路和放大电路;

-

将FPGA开发板与外围电路进行组装;

-

将程序下载到FPGA芯片内;

-

可用示波器观测输出波形,进行系统调试,发现错误并改正错误,对系统进行进一步的优化;

-

当硬件电路设计、制作、调试完成后,必须要用标准仪器设备进行实际测量,验证所设计系统的测试正确率与误差;

10)在实验完成后,可以组织学生以项目演讲、答辩、评讲的形式进行交流,了解不同解决方案及其特点,拓宽知识面。

在设计中,要注意学生设计的规范性;如系统结构与模块构成,模块间的接口方式与参数要求;在调试中,要注意电路工作的稳定性与可靠性;在测试分析中,要分析系统的误差来源并加以验证。

实验原理及方案

(1)系统结构

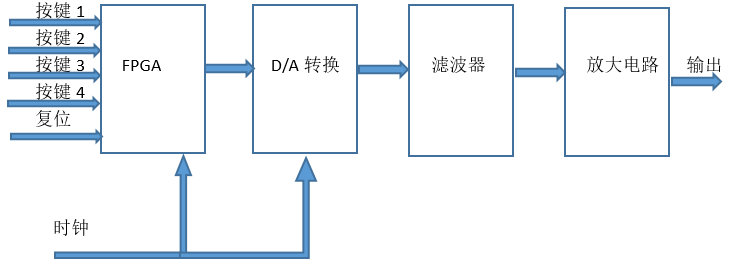

如图1所示,DDS函数发生器主要由4个硬件单元构成,其中FPGA是主要的功能单元,通过对其内部编程可实现相位累加器、波形存储器等功能,得到相应的输出幅度码,再经D/A转换器得到对应的阶梯波,最后通过低通滤波器对波形进行平滑处理及放大电路对波形进行放大,得到连续平滑的波形。

图1 DDS函数发生器的结构框图

(2)实现方案

1)方案比较

基于DDS函数发生器的实现的方案有很多种:

方案一:采用高性能DDS芯片(如AD9852、AD9854等)及模拟锁相环技术实现波形的产生,随着电子技术的快速发展,高性能的DDS产品日益更新,但模拟锁相环电路仍然比较复杂、不易调节、成本较高,这种方案实现的函数发生器具有频率调节不方便、频率输出范围小、输出波形类型少等特点,实现方案不够灵活。

方案二:采用单片机作为核心器件直接数字频率合成。利用C语言编程,实现方式容易,也容易实现多种波形输出;但由于运算位数、运算速度和晶振的影响,产生波形质量差,频率很难达到较高要求,并且单片机的I/O引脚少、存储容量少,这就直接导致外围电路复杂。

方案三:采用FPGA作为核心控制器件直接数字频率合成,结合简单的外围电路实现各种波形输出,这种方案不需要DDS器件,并且前端是全数字化的实现过程,所以具有电路结构简单、频率分辨率及稳定性高、频率切换速度快、控制灵活及性价比高等特点。

本次设计采用方案三实现。

2)基于FPGA的DDS设计

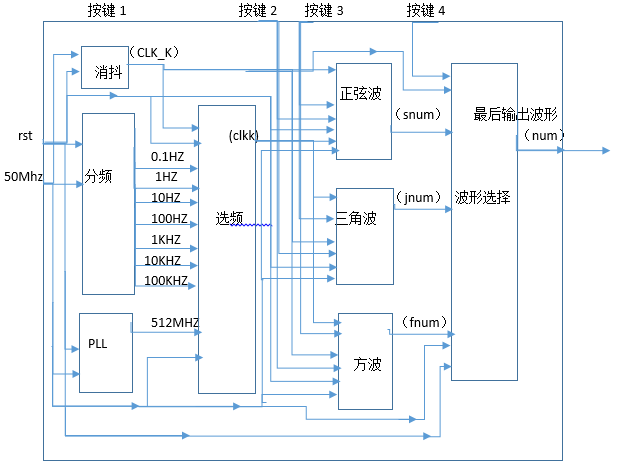

FPGA实现DDS的总体设计框图如图2所示。

图2 用FPGA实现DDS的总体设计框图

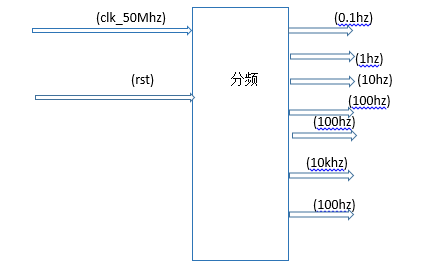

① 分频和倍频模块

首先将输出方波、三角波和正弦波的频率范围0.1hz-2Mh分段为0.1hz-1hz、1hz-10hz、10hz-100hz、100hz-1khz、1khz-10khz、10khz-100khz、100khz-1Mhz七段,频率步进分别对应0.1hz、1hz、10hz、100hz、1khz、10khz、100khz和2Mhz。输出频率与分频后频率的关系如表1所示。

表1 输出频率与分频后频率的关系

| 50M时钟分频计数次数 | 分频后频率(fkk) | Rom中数据个数 | rom输出频率(fout) |

|---|---|---|---|

|

|

256 |

|

|

|

256 |

|

| 9765(h 2625) |

|

256 |

|

| 977(h 3D1) |

|

256 |

|

| 98(h 62) |

|

256 |

|

| 10(h A) |

|

256 |

|

| 1(h 1) |

|

256 |

|

| 倍频 |

|

256 |

|

对于输出频率小于50Mhz的信号,采用计数分频的方式可得到0.1hz 、1hz、10hz、100hz、1khz、10khz和100khz的分频,其计数分频设计框图如图3 所示。

图3 计数分频设计框图

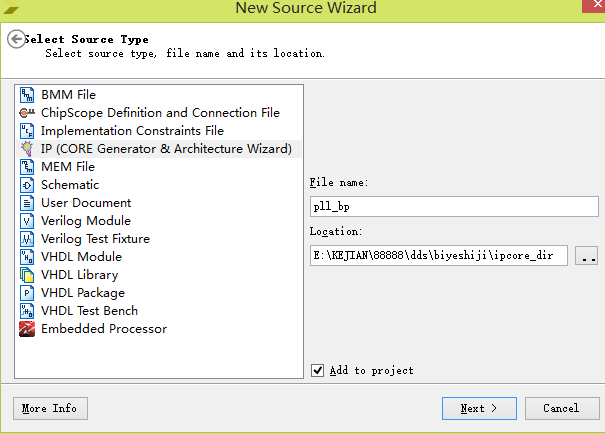

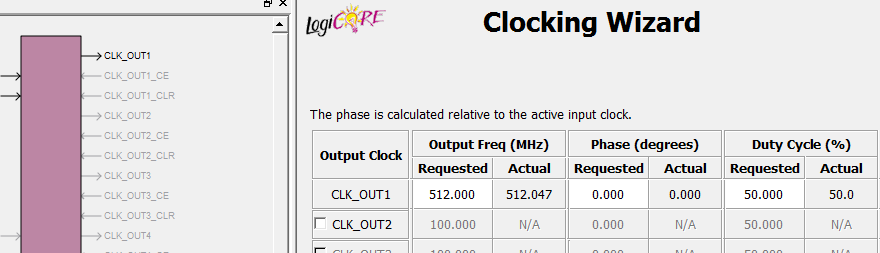

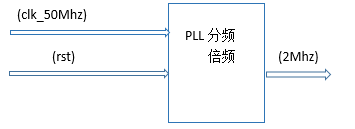

而对于输出频率高于50Mhz的信号,需要通过倍频的方式获取,倍频简单快捷的实现方法是采用锁相环PLL实现,可通过调用IP核完成。锁相环PLL的IP核生成过程如图4和5所示。

图4 锁相环PLL IP核的生成

图5 50Mhz倍频为512Mhz

生成的锁相环PLL模块如图6所示。

图6 锁相环PLL模块框图

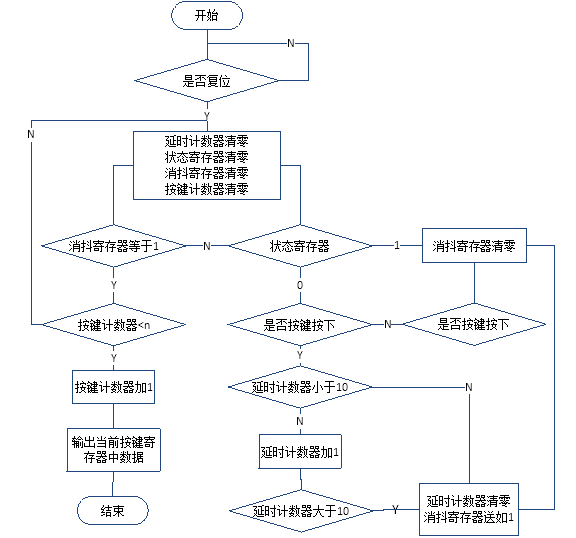

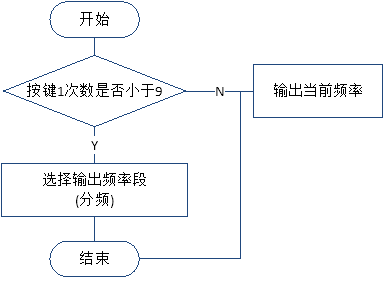

②按键模块

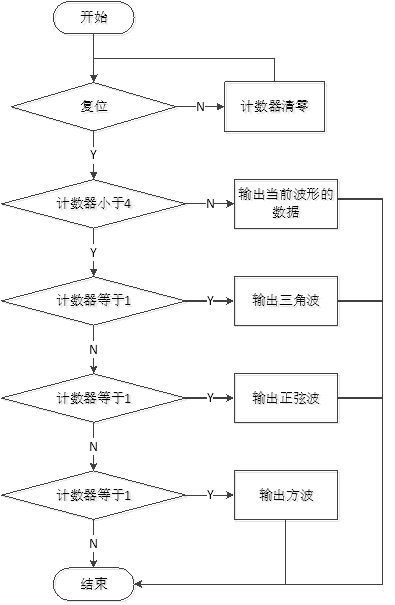

系统采用4个按键进行控制。按键1通过计数按键次数控制频率段的选择;按键2用来控制频率控制字;按键3控制波形相位选择;按键4来控制波形的输出类型,按键按一下是三角波,按键

按两下是正弦波,按键按三下是方波。按键控制流程图如图7所示。

图7

按键控制流程图

图7

按键控制流程图

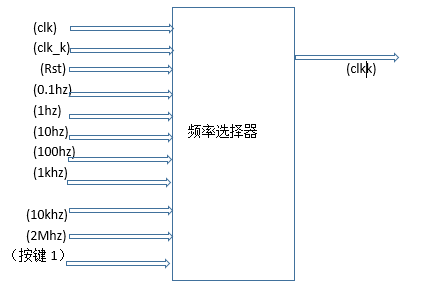

③频率段选择模块

这个模块由按键1、输入时钟0.1hz、1hz、10hz、100hz、1khz、10khz、100khz和2Mhz、消抖之后的时钟clk_k、复位rst作为输入,选择后的时钟(clkk)作为输出,模块框图和流程图如图8和图9所示。

图8 频率选择段模块框图

图9 频率选择段模块流程图

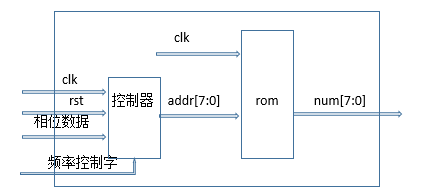

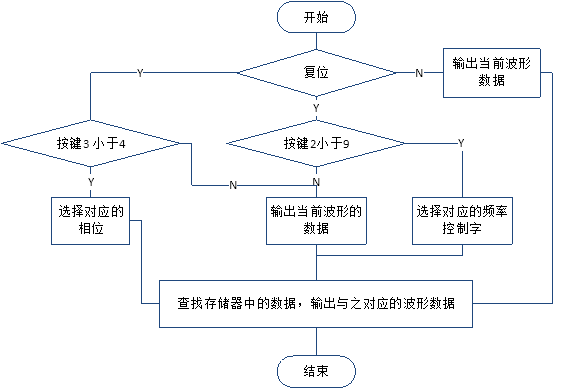

④波形存储读取模块

首先调用IP核,将事先准备好的波形数据存放在rom里,然后再用一个控制器把rom里面的数据读取出来,其设计结构框图如图10所示,设计流程图如图11所示。

图10 波形存储读取模块

图11 波形存储读取程序设计流程图

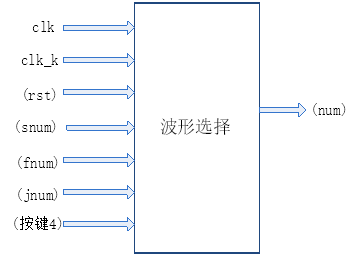

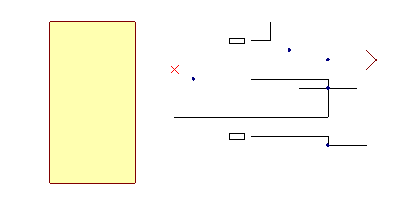

⑤波形选择模块

此模块包含有50Mhz的时钟(clk)、复位(rst)、按键消抖后的时钟 (clk_k)、正弦波(snum)、方波(fnum)、三角波(jnum)和(按键4)七个输入端及最后选择的波形(num)输出,波形选择模块框图如图12所示,程序流程图如图13所示。

图12 波形选择模块框图

图13 波形选择模块流程图

3)D/A转换模块的实现

FPGA实现DDS最后得到的是数字信号,要得到正弦波信号,需要用D/A转换器将其转换为模拟波形。

D/A转换器的型号很多,需要考虑其精度及速度问题。这里给出的参考器件是DAC904,其具有可伸缩电流输出在2mA与20mA之间、具有14 位输入、速度为165MSPS等特点。在速度和精度上都满足本次设计的要求。D/A转换电路如图14所示。

图14 D/A转换电路

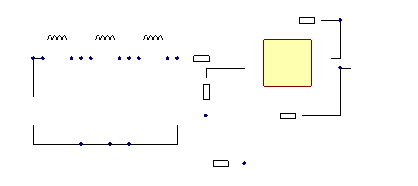

4)低通滤波及放大模块的实现

经D/A转换得到的波形是阶梯状的,为了得到平滑的输出波形,需要进行滤波和放大,滤波及放大参考电路如图15所示。

图15 低通滤波及放大电路

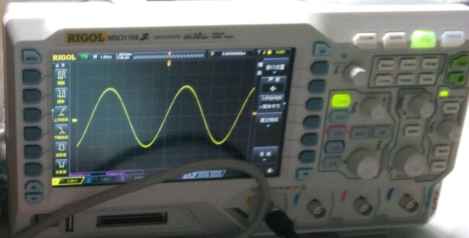

(3)实验结果参考

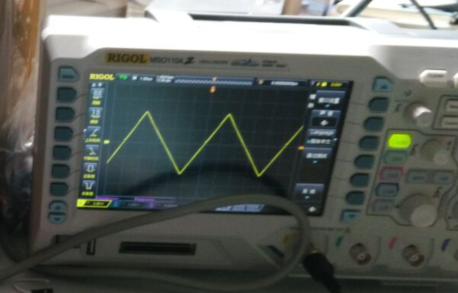

硬件系统在示波器上的调试结果如图16、图17、图18所示。

图16 正弦波输出

图17 三角波输出

图18 方波输出

教学实施进程

《基于FPGA的DDS函数发生器设计与实现》实验系统的时间跨度较长,因此有必要设置各个实验阶段的时间节点,向学生明确每个阶段应该完成的工作任务。

具体的教学实施过程如下:

-

课题组对实验内容及要求的审核,确定项目的难度适中及项目的可行性;

-

对学生进行分组,下达实验任务书;

-

进行实验方法、实验流程、功能模块简要介绍、考核方法的课堂教学;

-

布置针对实验任务的资料查阅、搜集汇总、整理;

-

安排小组讨论,通过抛出初步思路,引导学生在前期整理资料的基础上,提出个人的初步实验方案,组内同学并在相互讨论过程中进行思路的碰撞,不断发现问题、思考问题、解决问题;

-

学生进行选定方案的功能单元划分及单元电路软件仿真验证、测试;

-

学生进行外围电路的原理图、PCB图设计;

-

外协加工制作印制电路板;

-

学生列写BOM清单,采购或领取实验所需元器件;

-

在实验室进行电子元器件的焊接、装配;

-

通过外接实验仪器,开展实验电路软硬件系统的联合调试;注意必须采用分块调试的办法,逐单元进行故障排查、完成调试后再整机同时上电;

-

测试实验装置的功能是否达到设计任务书的要求,利用实验仪器或接口装置观察、测试相应的数据并记录在实验报告册中,尝试在现有方案的基础上进行功能的改进和扩展。

实验报告要求

-

实验需求分析:正确理解实验项目的内容和要求

-

实现方案论证:实验的蓝图,关系到实验的成败

-

理论推导计算:科学的计算分析

-

电路设计与参数选择:元器件的选型、设计方案的拟定与选择、电路参数的计算

-

电路测试方法:调试电路,修改电路的设计错误

-

实验数据记录:按一定规律记录获得的测试数据

-

数据处理分析:结果计算分析

-

实验结果总结与心得体会:误差分析,出现的问题及解决方案,心得体会

考核要求与方法(限300字)

-

实物验收:功能与性能指标的完成程度(如硬件设计、软件设计),完成时间。

-

实验质量:电路方案的合理性,焊接质量、组装工艺。

-

自主创新:功能构思、电路设计的创新性,自主思考与独立实践能力。

-

实验成本:是否充分利用实验室已有条件,材料与元器件选择合理性,成本核算与损耗。

-

实验数据:测试数据和测量误差。

-

实验报告:实验报告的规范性与完整性。

项目特色或创新(可空缺,限150字)

实验是基于FPGA的DDS函数发生器设计,可实现频率和相位都可调的三角波、方波、正弦波输出。具有频率分辨率及稳定度高、相位噪声低、控制灵活和性价比高等特点。设计的产品可应用于生产实践。综合了FPGA技术、数字电路、模拟电路、硬件设计与调试、软件编程等多方面知识,对提高学生的综合设计能力及动手能力有很大的促进作用。

参赛选手信息表

| 案例提供单位 | 西南科技大学 | 相关专业 | 通信工程 | |||

|---|---|---|---|---|---|---|

| 设计者姓名 | 刘春梅 | 电子邮箱 | 342751544@qq.com | |||

| 移动电话 | 13990170159 | 通讯地址 (含邮编) |

四川绵阳西南科技大学信息工程学院通信系 | |||

| 设计者姓名 | 杨超 | 电子邮箱 | ychao1983@126.com | |||

| 移动电话 | 18281916913 | 通讯地址 (含邮编) |

四川绵阳西南科技大学国防科技学院信息对抗系 | |||

| 设计者姓名 | 曹文 | 电子邮箱 | 530149775@qq.com | |||

| 移动电话 | 13981163352 | 通讯地址 (含邮编) |

四川绵阳西南科技大学信息工程学院电子工程系 | |||

| 相关x课程名称 | FPGA技术 | 学生年级 | 三年级 | 学时(课内+课外) | 48 | |

支撑 条件 |

仪器设备 | 计算机、FPGA实验箱、直流稳压电源、数字示波器、电焊台、万用表、信号发生器 | ||||

| 软件工具 | ISE Design Suite 14.7、Altium Designer13、proteus、VISIO | |||||

| 主要器件 | Spartan6 AX309 FPGA开发板、DAC904D/A转换器、LM7171运算放大器、电阻电容若干 | |||||