基于FPGA的JPEG图像压缩算法的电路实现

实验题目:基于 FPGA 的 JPEG 图像压缩算法的电路实现

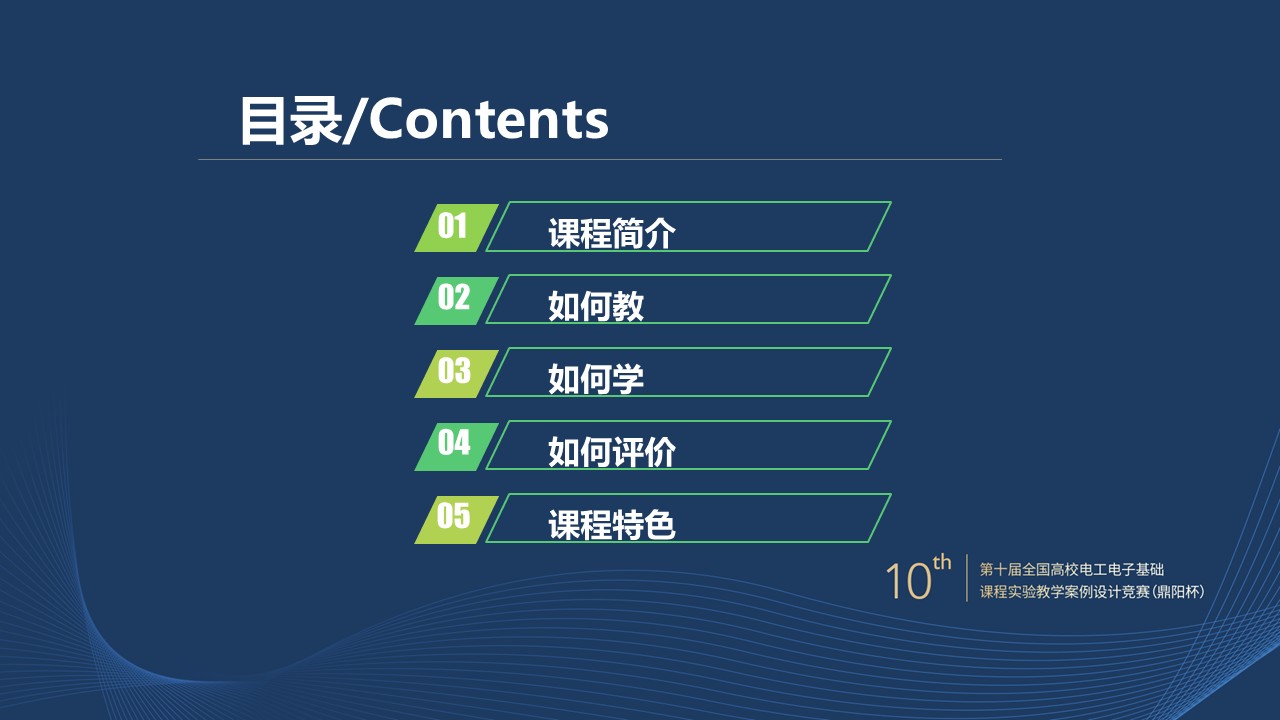

1. 课程简要信息

课程名称:数字系统设计实践课程学时:80项目学时:课内 $8 0 +$ 课外 40适用专业:集成电路设计与集成系统学生年级:大二学年 第三学期

2. 实验内容与任务(限 500 字,可与“实验过程及要求”合并)

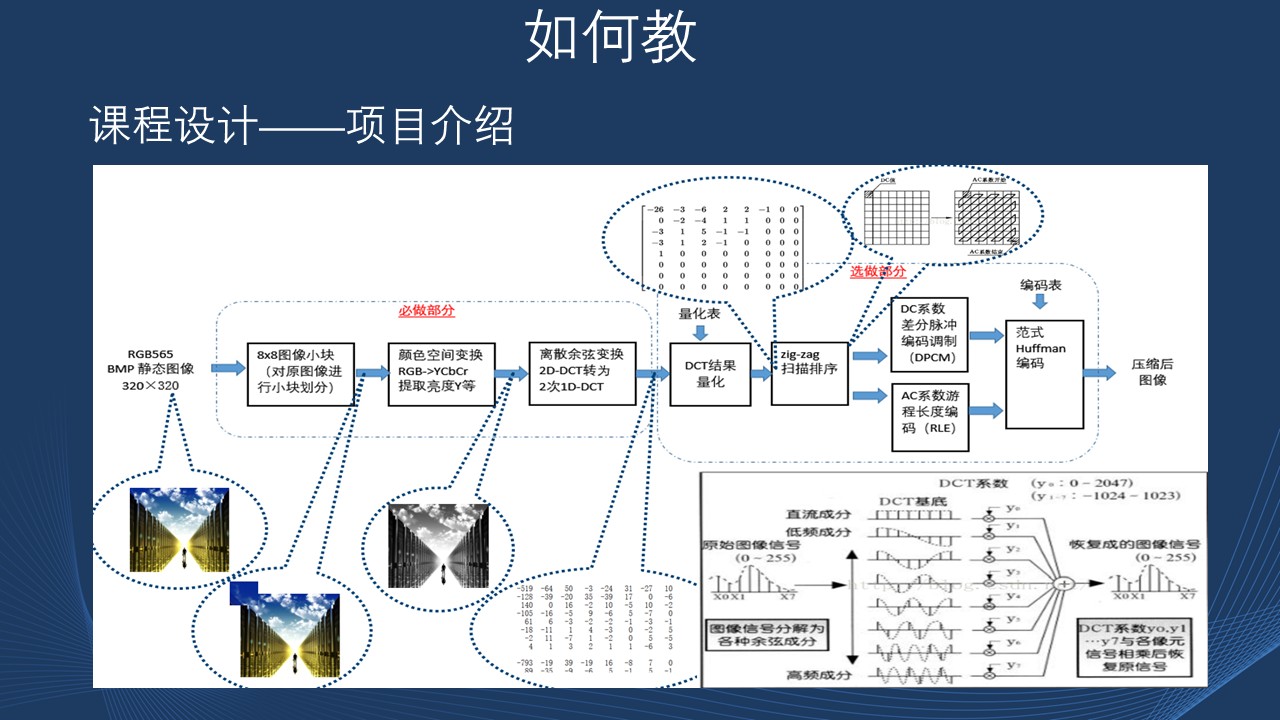

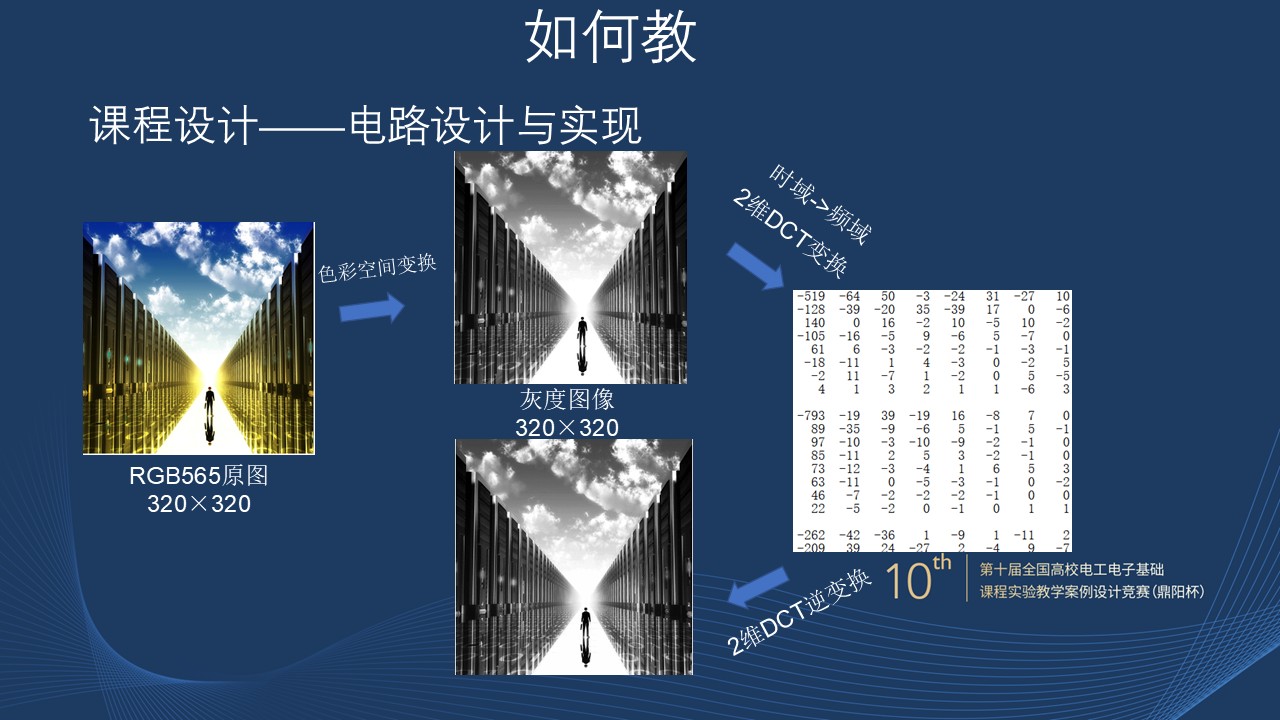

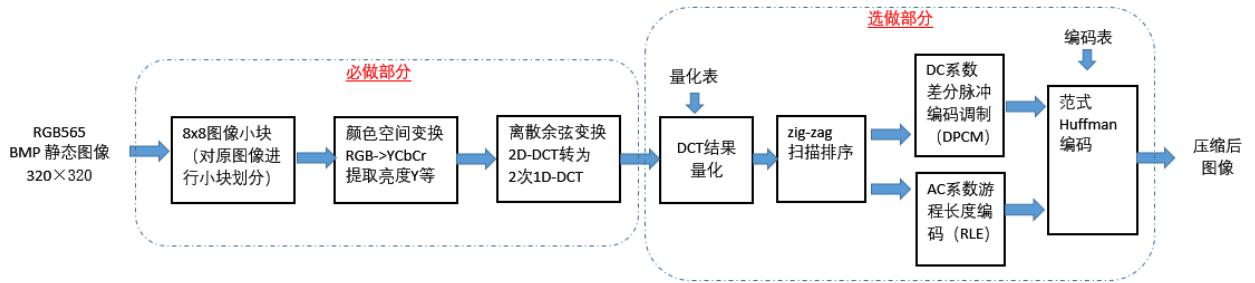

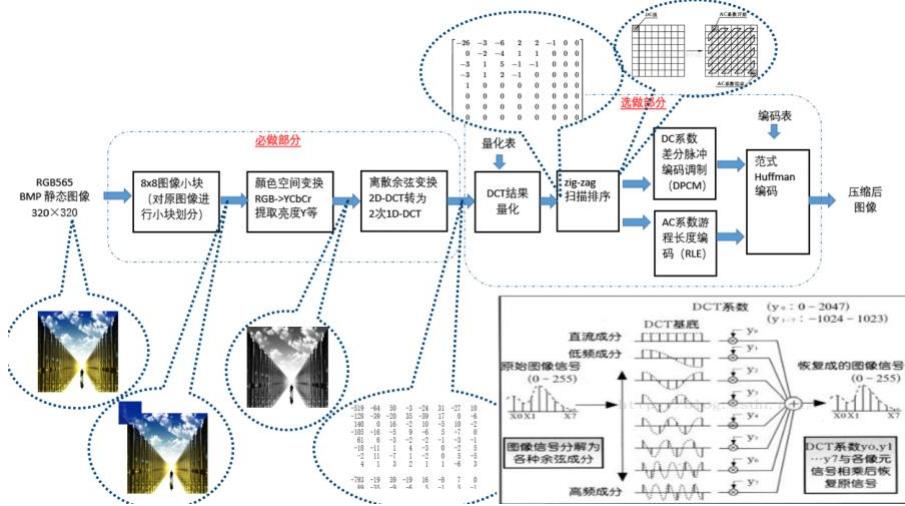

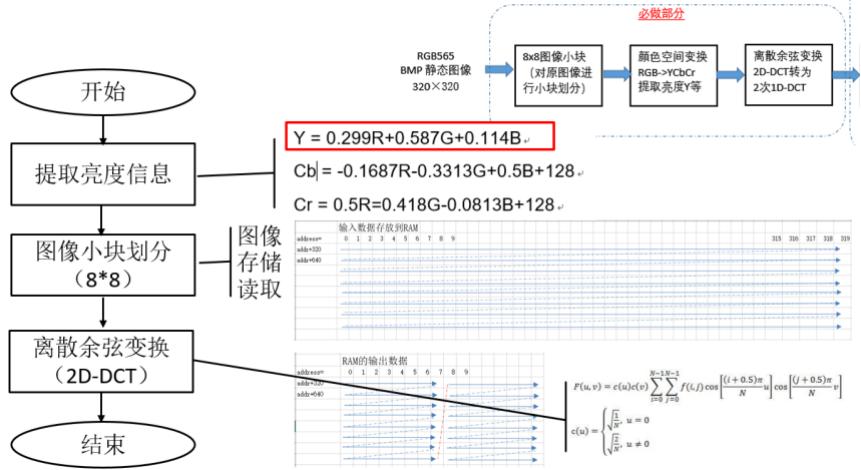

要求按照数字系统项目开发的基本流程,完成基于FPGA的JPEG图像压缩算法的设计与实现,包括颜色空间转换(R $\mathrm { G B - } { > } \mathrm { Y U V }$ )、离散余弦变换(DCT)、DCT 结果量化、zig-zag 扫描排序、DC系数差分脉冲编码调制(DPCM)、AC系数游程长度编码(RLE)、范式Huffman 编码等模块的需求分析、流程图整理、电路结构设计及Verilog编码、仿真。项目结束后需要完成整个项目的总结报告,对项目的各环节进行说明。JPEG图像压缩系统框图如下所示。

3. 实验过程及要求(限 300 字)

(1)必做部分要求

·根据分析项目各个步骤算法原理,明确电路各模块实现的功能;·梳理流程图,实现图像小块划分以及颜色空间变换模块;·根据系统需求设计合理的 FPGA 控制电路流程图,根据系统流程图,提取数据通路并设计状态机,确定DCT 模块结构;·用硬件描述语言实现所作设计;·采用EDA 工具对系统电路进行仿真、下载板子,确认各模块功能的正确性;·撰写项目总结报告,并进行答辩。

(2)选做部分要求

·实现 DCT 结果量化模块;

·实现 zig-zag 扫描排序模块;

·实现 DC 系数差分脉冲编码调制模块;

·实现 AC 系数游程长度编码模块;

·实现 Huffman 编码模块;

·对系统电路进行仿真,确认功能的正确性。

4. 相关知识及背景(限 150 字)

本项目是针对集成电路专业的二年级学生所学的《数字电路》、《高级数字系统设计》等课程开设的技能实习。需要掌握数字电路基础知识、现代数字电路设计思想以及 Verilog 硬件描述语言等。该项目将先修课的理论知识应用到实际项目开发过程中去,提高同学们的分析和解决问题能力,加深对理论知识的认知水平的同时,快速提高实践动手能力。

5. 实验环境条件

硬件:笔记本

软件: Quartus Prime、ModelSim

6. 教学目标与目的(限 150 字)

本实践学期课程是针集成电路设计与集成系统专业的二年级全体学生开设的技能实习。将把学生在二年级期间所学的数字电路,高级数字系统设计等课程的知识与实际工程结合起来,通过数字系统的设计、验证等手段将所学的理论知识应用到实践中去。从而使学生不但熟练地掌握所学的理论知识,而且能够将所学的知识熟练地应用于数字系统设计等实际的工程当中,进而提高学生的实际动手能力和应用知识解决问题的能力。

7. 教学设计与实施进程

本项目是一个完整的数字系统设计实践项目,需要经历学习研究、方案论证、系统设计、硬件编码、仿真测试、设计总结等过程。在实验教学中,主要进行如下设计和实施。

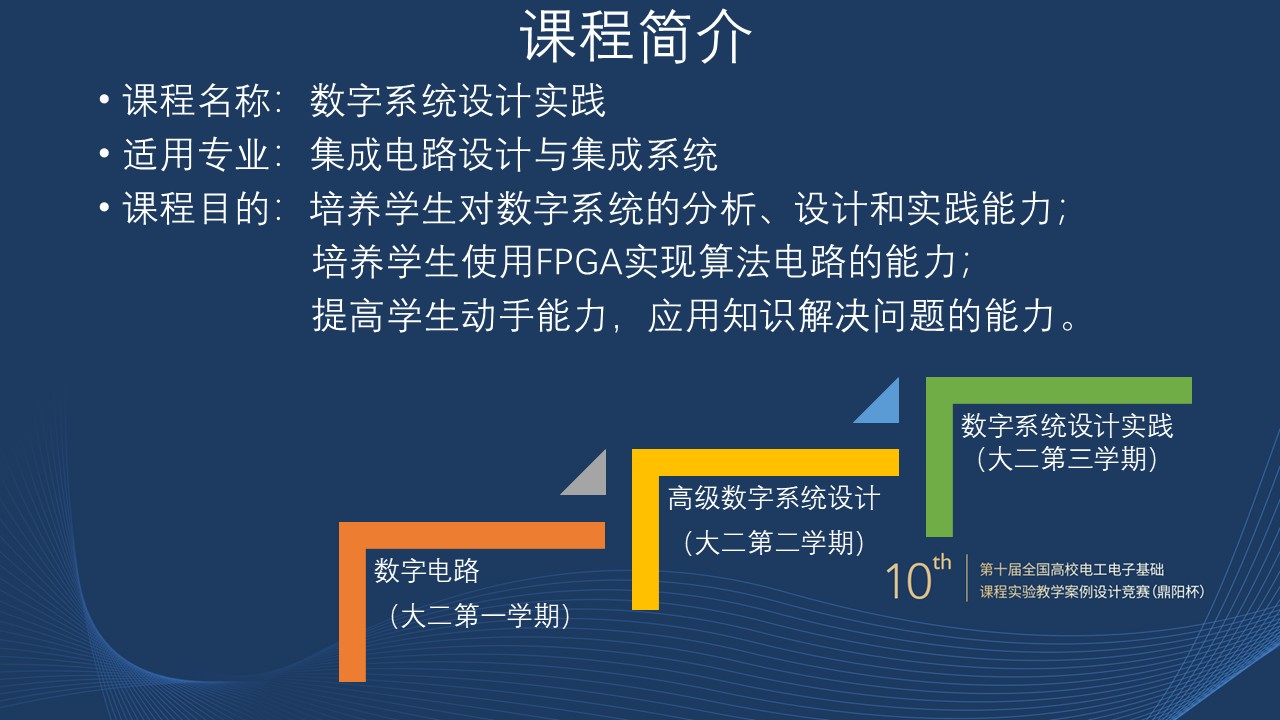

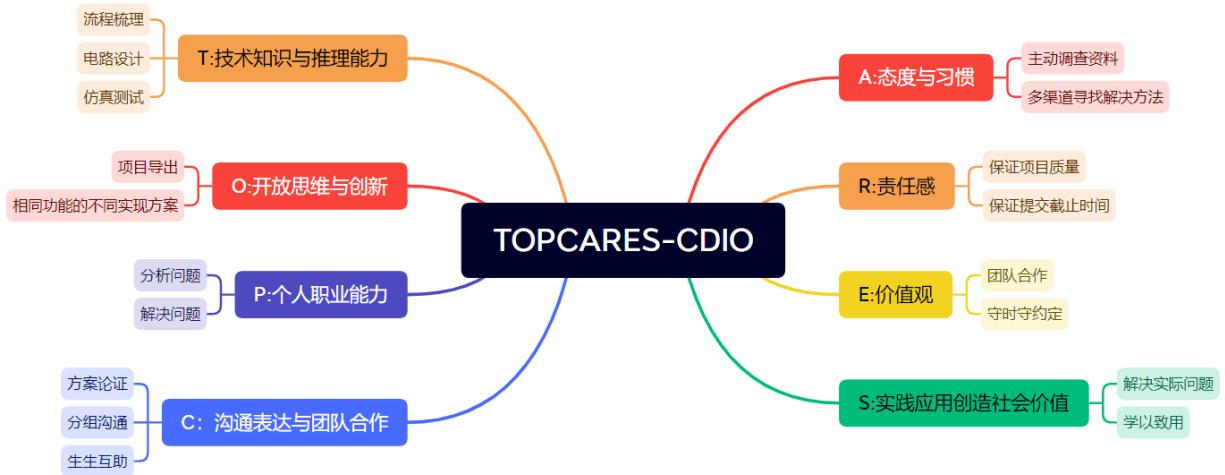

(0)教学理念

将学校“教育创造学生价值”的理念,在本项目中落地生根,详情可参考下图。

(1)教学阶段

本项目共 80 学时课程,可划分为以下几个阶段。

| 阶段名称 | 内容说明 | 学时 |

| 项目介绍 | 项目介绍、算法分析及项目预期效果演示 | 8 |

| 重要知识回顾及拓展 | 回顾本项目中可能用到的控制方式、回顾前修课程中Verilog 编码相关知识点 | 8 |

| 整体流程图设计 | 基于必做部分,梳理整体流程图,进行模块划分 | 4 |

| 子模块设计(颜色空 | 基于各个子模块的具体功能,确认子模块功能,梳理流程图和 | 36 |

| 及图像小块划分、DCT变换模块设计) | 间转换、亮度值存取」端口信息,设计控制单元和数据通道,采用合适的控制方式实现各子模块功能。 | |

| 顶层设计、仿真验证及联合调试 | 设计顶层,搭建测试平台,通过波形、输出图片等形式进行功能确认。 | 20 |

| 书写项目报告 | 介绍项目报告要求 | 4 |

(2)教学组织

根据教学阶段不同,课前、课中、课后的组织形式和侧重点略有不同,具体组织过程如下所示。

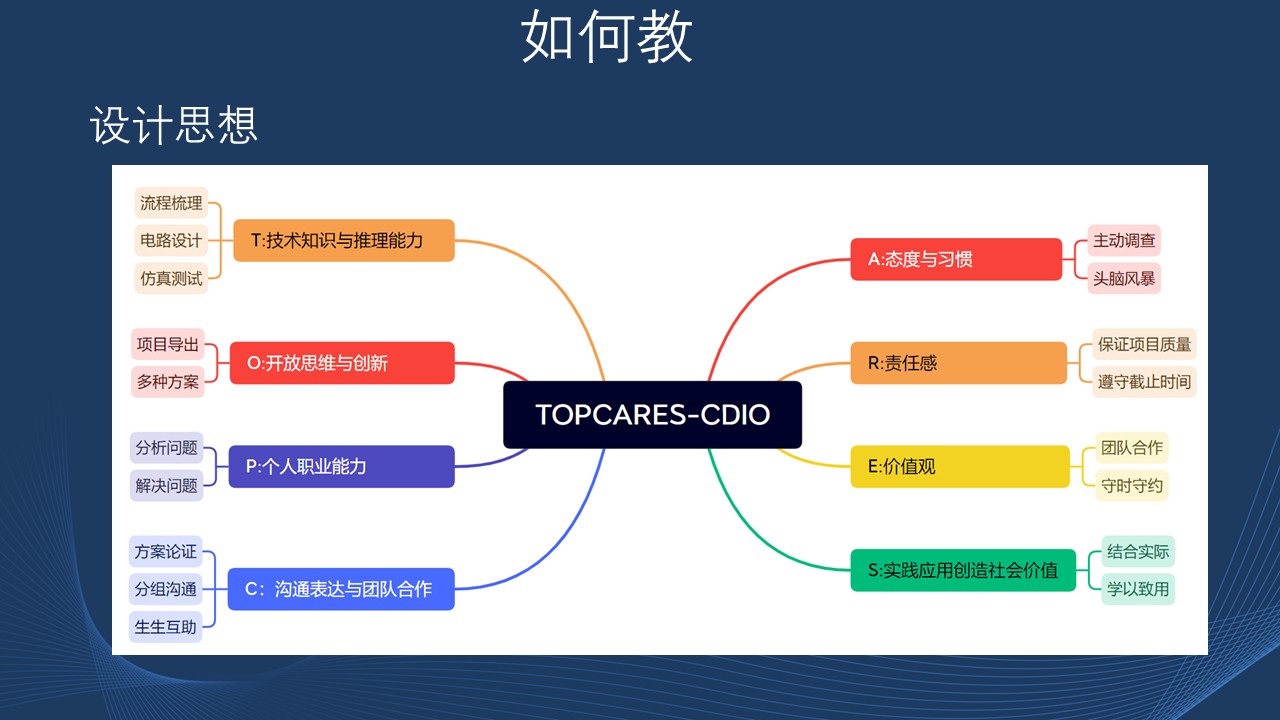

(2-1)项目介绍

在项目介绍阶段,主要目的是为了让学生了解本项目的内容及要求,对项目有整体了解,对课程有清醒认知。

【课前】抛出思考题:在摄像头分辨率日益增长的今天,拍摄图片的清晰度也变得越来愈高,如何在仅有的存储空间内存储更多照片?图像存储面临哪些问题?可以如何解决?

※目的:请同学思考并在课上讨论,旨在让学生自己分析总结图像存储面临的问题及解决办法,进而引出本次实践项目题目。

【课中】采用讲授教学法,介绍课程信息及要求。并采用讨论教学法,引出图像存储存在的问题,并引出本次实践项目的题目。随后介绍实践项目的流程、各个阶段的功能及意义。并通过演示教学法演示项目最终展示的成果,使学生对项目整体形成一个宏观印象。

在每个阶段讲解之后,通过“雨课堂”进行互动问答,帮助学生加深对知识的理解与掌握,同时根据报告,实时调整课程进度。雨课堂实时报告如下图所示。

【课后】布置课后准备及调查任务

1、安装课程所需 EDA工具。

2、调查 JPEG 图像压缩算法各阶段的实现方法。

(2-2)重要知识回顾及拓展

该阶段,主要介绍本项目常用的 RAM读写、乒乓操作、流程先设计等控制方式,辅助学生在日后的设计中选择合适的控制方式进行电路设计。并且针对学生硬件编码能力薄弱的问题,将凝练后的组合电路、时序电路、状态机的编码规则再次集中讲解,方便学生随用随查,提高学习效率。

【课前】抛出思考题:如何使用 Verilog 描述组合电路、时序电路以及状态机?

【课中】采用讲授教学法与讨论教学法,引出各个控制方式的特点、应用场景及设计注意点,并采用“雨课堂”的方式进行课堂互动,针对学生掌握薄弱的内容,课堂随机调整上课节奏,进行二次强调及巩固。将各类电路的Verilog编码规则以“know how”的形式分享给学生,帮助学生快速回顾并巩固前修课程知识,为本项目后期的编码环节夯实基础。

由于编码调试环节相对枯燥,学生难免产生退缩畏惧的情绪,可以在课上结合“毛竹的生长过程”,进行隐形思政教育,鼓励学生注重平时的知识积累,才能够像竹子一样长期在地下扎根,短期内厚积薄发,实现快速成长。

每天都能看到它的生长/它的进步/它的收获吗?

前5年,毛竹丝毫不长,到了第6年雨季到来的时候,它可以每天6英尺的速度向上急窜15天左右,最后大约可以长到90英尺高,并成为竹林中的身高冠军。

注重平时知识的积累,才能够实现厚积薄发。

【课后】布置练习电路,要求学生用 Verilog 硬件描述语言实现,趁热打铁帮助学生快速掌握Verilog 编码的关键点。

(2-3)整体流程图设计

从本次课程开始,该实践项目将正式进入设计阶段。

【课前】抛出思考题:结合项目介绍及个人调查,梳理必做部分的流程图。

【课中】采用讨论教学法,分享各位同学提出的流程图,以学生为中心进行讨论,分析每个流程图的优缺点并得到合理的流程图,从而进行系统整体设计及模块划分。

【课后】梳理第一个子模块(颜色空间转换)的功能及端口表。

(2-4)子模块设计

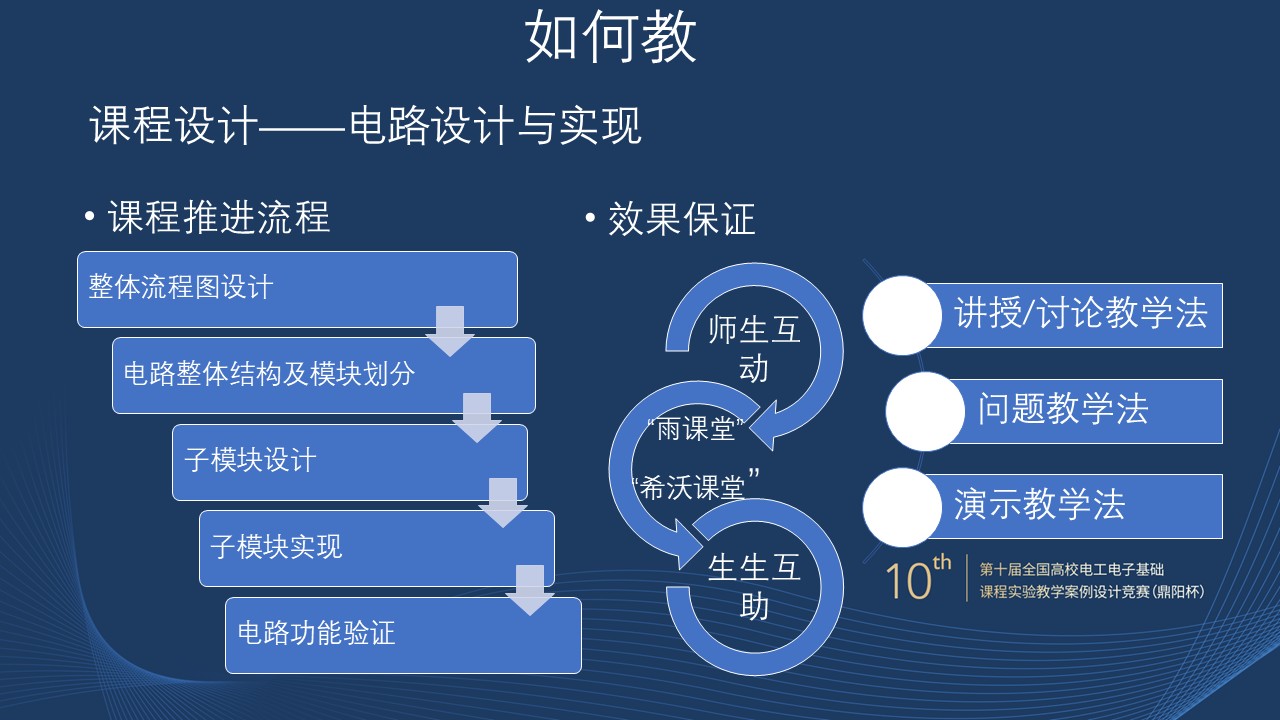

本阶段将进行项目各个子模块的设计,根据每个子模块的特点不同,侧重点也不同。

【课前】完成前一次课程的任务。

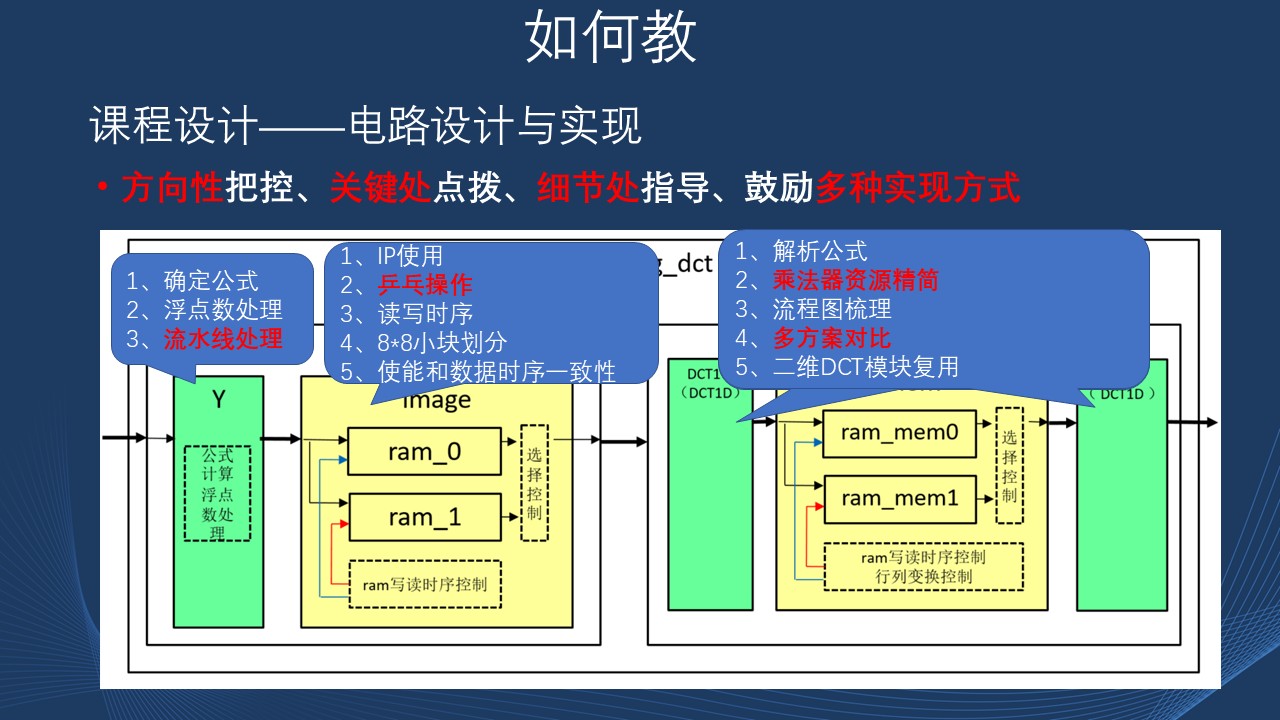

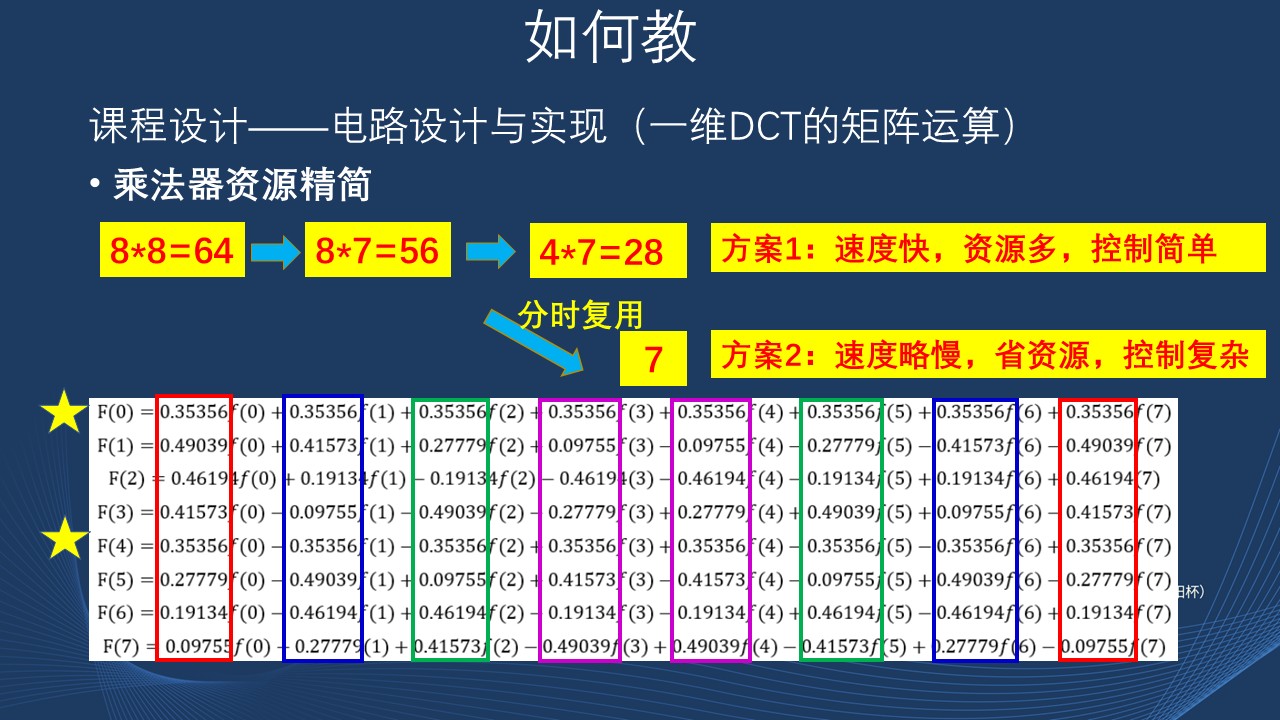

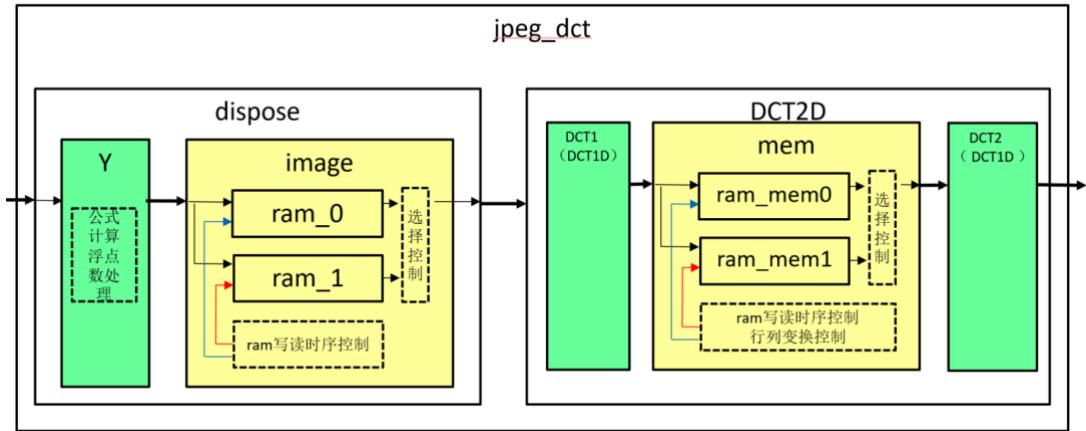

【课中】主要采用讲授教学法与讨论教学法,进行各个子模块的设计,通过“雨课堂”测试确认学生当堂掌握情况并实时调整上课进度。在颜色空间转换模块中,主要讨论算法及其实现方法、浮点数处理及流水线控制的问题。在亮度值存取及图像小块划分模块,主要讨论 RAM 读写时序实现以及乒乓操作控制的问题。在 DCT 变换模块中,先从一维 DCT 入手,梳理流程图并设计状态机及数据通道。在一维DCT功能实现的基础上,引申至二维DCT变换。一维DCT 在设计的过程中可以让学生们从电路规模、资源以及效率等多维度考虑,寻求不同的设计方案。

※注意,在该阶段,授课老师需要频繁巡视全场,掌握每位同学的进度,及时总结共通性问题与全班分享。推荐采用问题教学法让学生主动发现问题,并通过讨论得到解决方案。并且可以分组讨论,形成师生互助,生生互助的模式。在生生互助中提高学生的表达、团队互助、组织协调等能力。历年课堂的组织图片可参考下图。

【课后】完成课上未完成的内容。

(2-5)顶层设计、仿真验证及联合调试【课前】完成所有子模块的设计。

【课中】在完成子模块设计的基础上,梳理顶层结构和端口表,并向学生提供基础验证环境。在此基础上,学生完善验证环境并进行仿真,通过波形以及输入输出图片数据的对比,确认电路功能的正确性。

【课后】完成课上未完成的任务。

(2-6)书写项目报告【课前】回顾整个项目的设计过程。

【课中】基于项目报告模板,向学生讲解项目报告的书写要求。

【课后】在规定时间内提交项目报告及成果物。

在整个教学实施过程中通过微视频辅助学生课前课后预习复习,通过“雨课堂”的课中测试,实时把握学生的知识吸收情况。以下为微视频以及“雨课堂”测试题样例的截图。

RAMIP生成操作演示.mp4

第1次课项目介绍--算法分析.mp4

G 第2次课项目介绍--项目预期效果演示.mp4

第3次课重要知识回顾及拓展--控制方式.mp4

第4次课重要知识回顾及拓展--VerilogHDL.mp4

D 第5次课-整体流程图及模块划分.mp4

第6次课-提取亮度值Y.mp4

D 第7次课-Y值存取及图像小块划分.mp4

G 第8次课-01DCT变换公式.mp4

第8次课-02DCT变换模块划分和端子表.mp4

第9-10次课-01DCT变换流程图设计.mp4

第9-10次课-02DCT变换数据通道提取.mp4

第9-10次课-03DCT变换状态机设计.mp4

D 第11-13次课-01DCT变换数据通道代码实现.m...

G 第11-13次课-02DCT变换状态机代码实现.mp4

G 第11-13次课-03DCT变换模块例化实现.mp4

第14次课-1维DCT结果的存储及行列变换.mp4

第16次课系统仿真验证及联合调试.mp4

RAM写操作时的地址变化范围是多少?

A 0~319

$\textcircled{1}$ 0~320

0 0~320*8-1

$\textcircled{1}$ 0~320*8

8. 实验原理及方案

(1)项目介绍

以图像压缩算法基本流程为基础,分解各个阶段的功能,详情如下图所示。

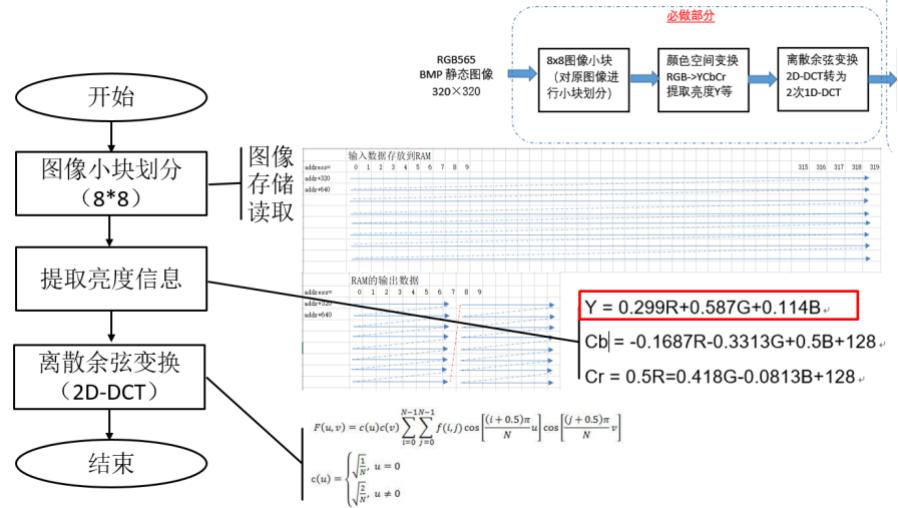

(2)整体流程图(初版)

依据项目介绍,整理初版流程图,详情如下图所示。

(3)整体流程图(改进版)

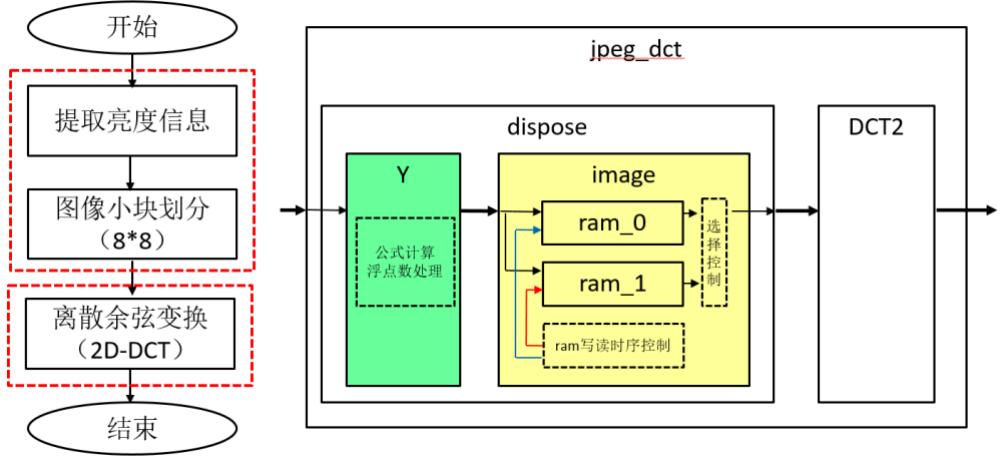

因初版流程图的电路规模较大,从优化电路资源的角度考虑,微调流程图中的处理步骤,详情如下图所示。

(4)模块划分

基于流程图,进行系统设计及子模块划分,详情如下图所示。

(5)子模块设计(5-1)颜色空间变换模块【公式】 $\mathbf { Y } = 2 . 4 6 0 \mathbf { R } + 2 . 3 7 6 \mathbf { G } + 0 . 9 3 8 \mathbf { B } - 1 2 8$

【给学生的提示】

- Verilog 中浮点数的处理可以采用左移扩大为整数后对应舍去低位的方法来处理。

- 考虑到组合电路的效率问题,可采用流水线方式进行控制。

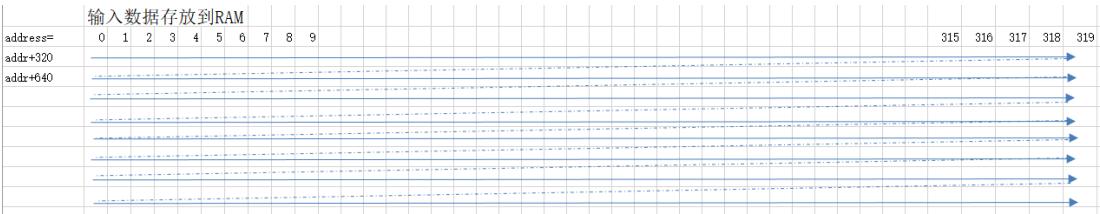

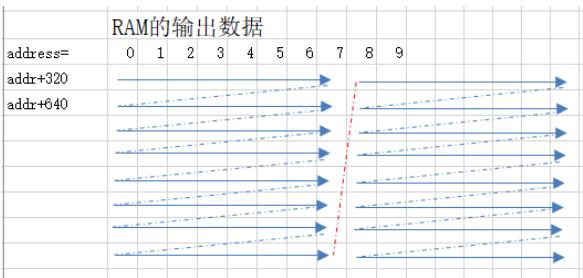

(5-2)亮度值存取及图像小块划分

【给学生的提示】可采用讲授教学法与讨论教学法,帮助学生解决以下问题。

-

端口表的设计,尤其是根据 RAM大小确定地址线位宽。

-

确保图片存取的流畅性,采用乒乓操作的控制方法。

-

RAM写访问时,写控制信号/写数据/写地址总线的设计细节问题。

-

RAM读访问时,读控制信号/读地址的更新问题、读数据的选择等细节问题。

-

两块 RAM 的读写切换的设计。

-

对比写地址和读地址设计的区别,讨论如何实现图像小块划分。可以通过以下两张图辅助学生理解。

(5-3)DCT 变换模块

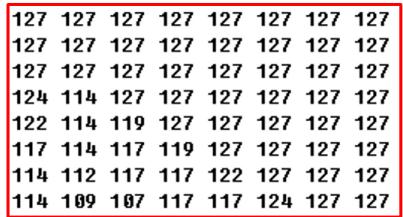

【概念解析】通过下图,帮助学生理解离散余弦变换是时域到频域的变换。

DCT变换后的数值

原始图像块的数值

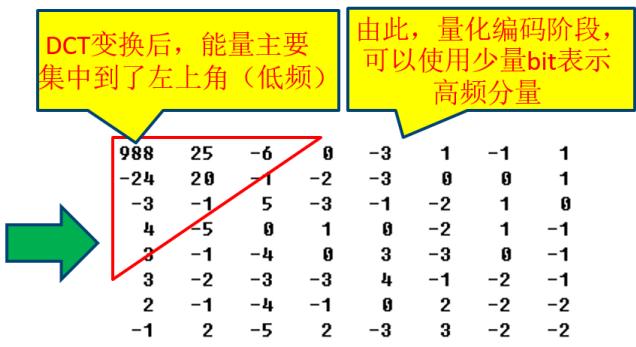

【一维 DCT 公式解析】

$$ F ( u ) = \sqrt { \frac { 2 } { N } } { \sum _ { x = 0 } ^ { N - 1 } } f ( x ) \mathrm { c o s } \frac { ( 2 x + 1 ) u \pi } { 2 N } $$

通常取 $N = 8$ $\mathrm { { \bf { F } } } ( { \bf { u } } ) = { \frac { \sqrt { 2 } } { \sqrt { 8 } } } * f ( 0 ) c o s { \frac { u \pi } { 1 6 } } + { \frac { \sqrt { 2 } } { \sqrt { 8 } } } f ( 1 ) c o s { \frac { 3 u \pi } { 1 6 } } + { \frac { \sqrt { 2 } } { \sqrt { 8 } } } * f ( 2 ) * c o s { \frac { 5 u \pi } { 1 6 } } + { \frac { \sqrt { 2 } } { \sqrt { 8 } } } * f ( 3 ) * c o s { \frac { 7 u \pi } { 1 6 } } + \cdots ,$

${ \mathrm { \Lambda } } ^ { z } ( 0 ) = 0 . 3 5 3 5 6 f ( 0 ) + 0 . 3 5 3 5 6 f ( 1 ) + 0 . 3 5 3 5 6 f ( 2 ) + 0 . 3 5 3 5 6 f ( 3 ) + 0 . 3 5 3 5 6 f ( 4 ) + 0 . 3 5 3 5 6 f ( 5 ) + 0 . 3 5 3 5 6 f ( 6 ) + 0 . 3 5 3 5 6 f ( 7 )$ F $( 1 ) = 0 . 4 9 0 3 9 f ( 0 ) + 0 . 4 1 5 7 3 f ( 1 ) + 0 . 2 7 7 7 9 f ( 2 ) + 0 . 0 9 7 5 5 f ( 3 ) - 0 . 0 9 7 5 5 f ( 4 ) - 0 . 2 7 7 7 9 f ( 5 ) - 0 . 4 1 5 7 3 f ( 6 ) - 0 . 4 9 0 3 9 f ( 7 ) .$ ) $^ { \ddagger } ( 2 ) = 0 . 4 6 1 9 4 f ( 0 ) + 0 . 1 9 1 3 4 f ( 1 ) - 0 . 1 9 1 3 4 f ( 2 ) - 0 . 4 6 1 9 4 ( 3 ) -$ $4 f ( 1 ) - 0 . 1 9 1 3 4 f ( 2 ) - 0 . 4 6 1 9 4 ( 3 ) - 0 . 4 6 1 9 4 f ( 4 ) - 0 . 1 9 1 3 4 f ( 5 )$ $1 9 4 ( 3 ) - 0 . 4 6 1 9 4 f ( 4 ) - 0 . 1 9 1 3 4 f ( 5 ) + 0 . 1 9 1 3 4 f ( 6 ) + 0 . 4 6 1 9 4 ( 7 )$ ) F $\begin{array} { r } { 3 ) = 0 . 4 1 5 7 3 f ( 0 ) - 0 . 0 9 7 5 5 f ( 1 ) - 0 . 4 9 0 3 9 f ( 2 ) - 0 . 2 7 7 7 9 f ( 3 ) + } \end{array}$ $1 ) - 0 . 4 9 0 3 9 f ( 2 ) - 0 . 2 7 7 7 9 f ( 3 ) + 0 . 2 7 7 7 9 f ( 4 ) + 0 . 4 9 0 3 9 f ( 5 ) +$ $7 9 f ( 3 ) + 0 . 2 7 7 7 9 f ( 4 ) + 0 . 4 9 0 3 9 f ( 5 ) + 0 . 0 9 7 5 5 f ( 6 ) - 0 . 4 1 5 7 3 f ( 7 )$ 7) F $4 ) = 0 . 3 5 3 5 6 f ( 0 ) - 0 . 3 5 3 5 6 f ( 1 ) - 0 . 3 5 3 5 6 f ( 2 ) + 0 . 3 5 3 5 6 f ( 3 ) +$ $. 3 5 3 5 6 f ( 2 ) + 0 . 3 5 3 5 6 f ( 3 ) + 0 . 3 5 3 5 6 f ( 4 ) - 0 . 3 5 3 5 6 f ( 5 ) - 0 . 3 5 3 5$ 56f(6)+0.35356f(7) F $5 ) = 0 . 2 7 7 7 9 f ( 0 ) - 0 . 4 9 0 3 9 f ( 1 ) + 0 . 0 9 7 5 5 f ( 2 ) + 0 . 4 1 5 7 3 f ( 3 ) -$ $1 ) + 0 . 0 9 7 5 5 f ( 2 ) + 0 . 4 1 5 7 3 f ( 3 ) - 0 . 4 1 5 7 3 f ( 4 ) - 0 . 0 9 7 5 5 f ( 5 ) +$ 0.49039f(6)-0.27779f(7) F(6) $= 0 . 1 9 1 3 4 f ( 0 ) - 0 . 4 6 1 9 4 f ( 1 ) + 0 . 4 6 1 9 4 f ( 2 ) - 0 . 1 9 1 3 4 f ( 3 ) - 0 . $ .19134f(4)+0.46194f(5)-0.46194f(6)+0.19134f(7) F $7 ) = 0 . 0 9 7 5 5 f ( 0 ) - 0 . 2 7 7 7 9 ( 1 ) + 0 . 4 1 5 7 3 f ( 2 ) - 0 . 4 9 0 3 9 f ( 3 ) + 0 . 4 9 0 3 9 f ( 4 ) - 0 . 4 1 5 7 3 f ( 5 ) + 0 . 2 7 7 7 9 f ( 6 ) - 0 . 0 9 7 5 5 f ( 7 )$

分析公式总结规律,尝试改变电路结构,节省资源消耗。通过分析系数的关系,可以将64 次乘法运算降低至28次。

维DCT的矩阵运算

矩阵系数的特点:

$\textcircled{1}$ f(O)和f(7)的矩阵系数值相等。f(1)和f(6),f(2)和f(5),f(3)和f(4),同样规律。$\textcircled{2}$ f(O)和f(7)的矩阵系数符号,奇数行相同,偶数行相反。f(1)和f(6),f(2)和f(5),f(3)和f(4),同样规律。

$\textcircled{3}$ 矩阵系数值都小于0.5

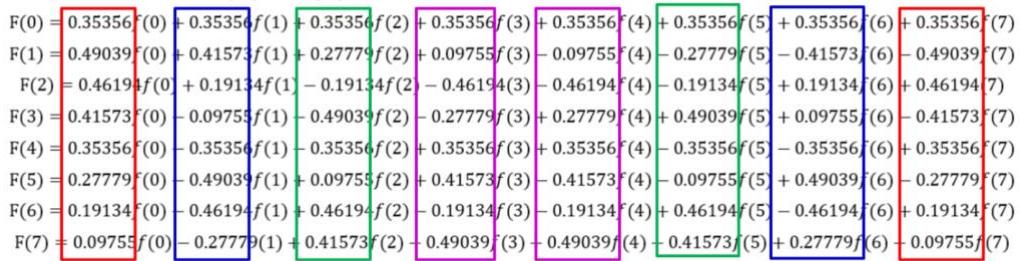

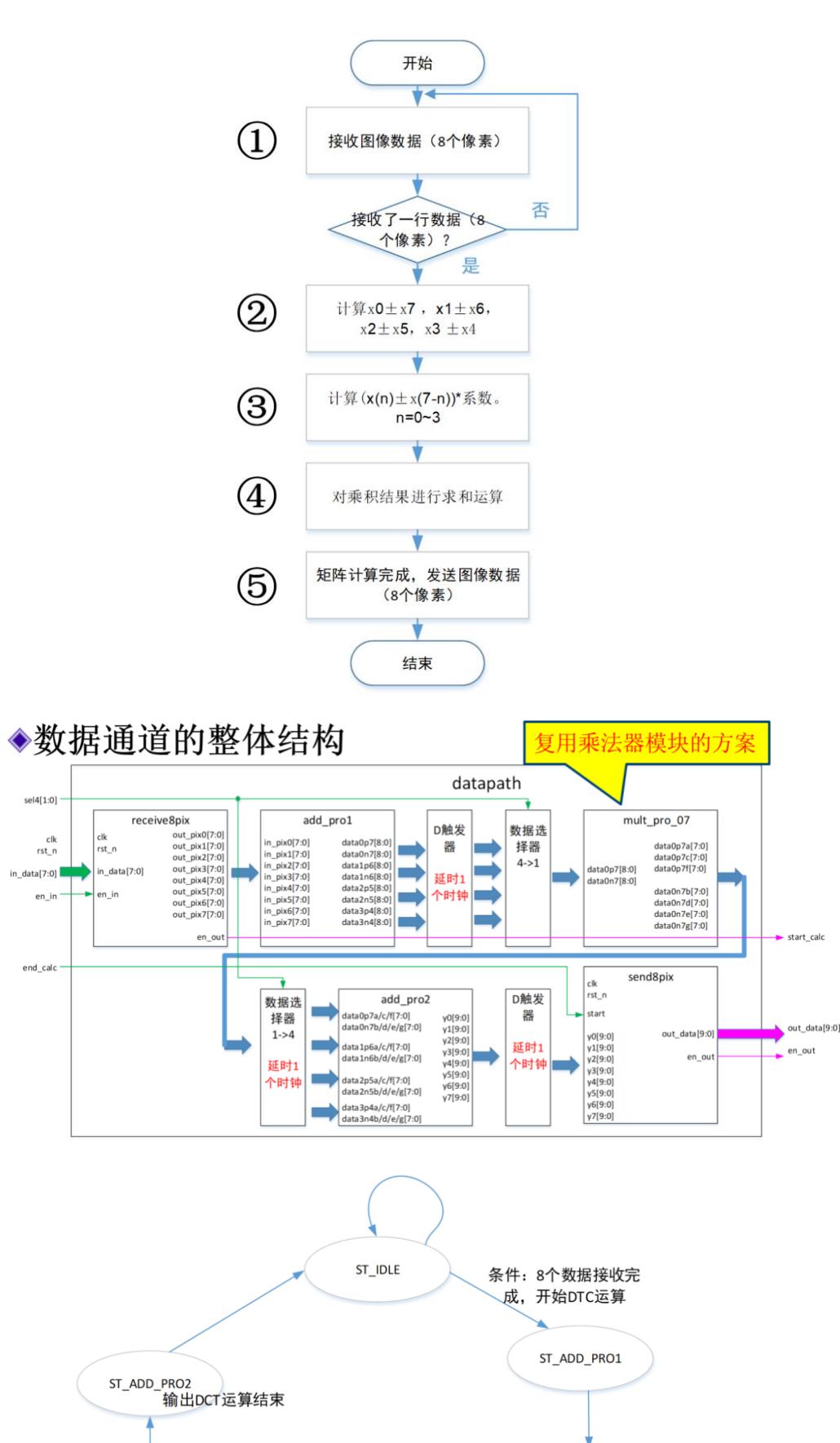

【一维 DCT 电路实现】

首先整理流程图,根据流程图提取数据通道和状态机。设计详情如下所示。

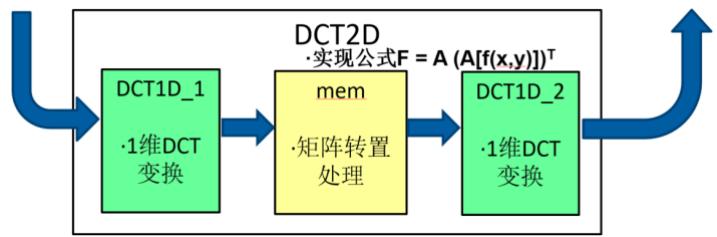

【二维 DCT 电路实现】

(6)顶层设计、仿真验证及联合调试

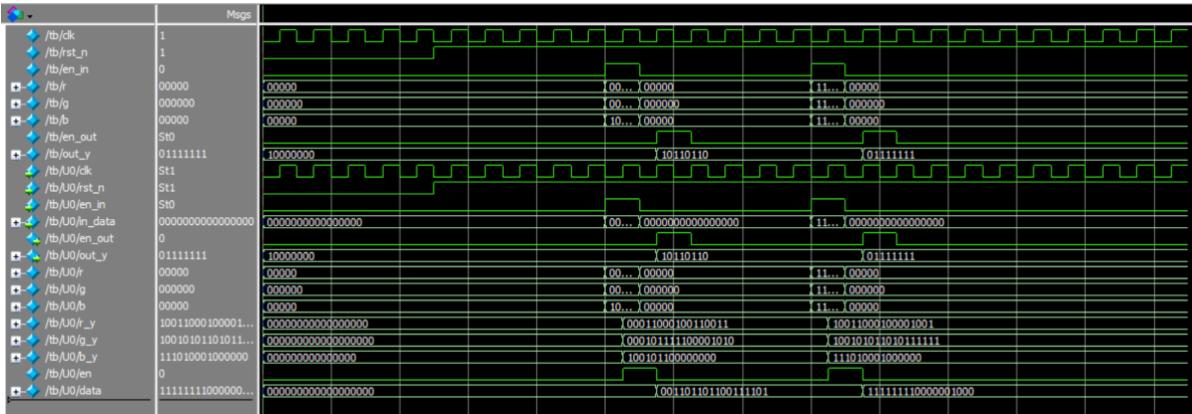

在仿真验证过程中,向学生提供基础版本的验证平台,学生基于该平台进行个性化修改后,通过观察波形、输入输出图片信息来确认设计模块功能的正确性。为防止学生遗忘工具的使用,配备特定的讲解视频。其中顶层电路图、仿真波形以及测试输入输出图片如下所示。

9. 实验报告要求

项目报告需要按照以下目录内容进行书写。

第 1 章 绪论 ..1.1 概述 ..1.2 国内外现状..

第 2 章 关键技术介绍.2.1 专有名词介绍..2.2 关键技术介绍..

第3 章 系统分析...3.1 JPEG 图像压缩算法分析 . 13.2 颜色空间变换算法分析.. 23.3 离散余弦变换算法分析.. 23.4 选作部分算法分析... 23.5 整体及 1DCT 流程图设计 . 2

第 4 章系统设计 ... 24.1 初步模块划分.. 24.2 颜色空间变换模块设计.. 24.3 $3 2 0 \times 8$ 转 $8 \times 8$ 模块设计 . 24.4 1DCT 数据通道 . 24.5 1DCT 状态机 ... 24.6 行列转置模块设计.. 24.7 选作部分模块设计.. 2

第5 章 系统实现... 35.1 开发环境介绍... 35.2 Y 模块实现 .. 35.3 image 模块实现 ... 35.4 1DCT 数据通路实现 . 35.5 1DCT 控制单元实现 . 35.6 mem 行列转置模块实现 35.7 选作部分模块设计.. 3

第 6 章 系统仿真和验证.. 36.1 模块仿真.. 36.2 系统仿真... 36.3 实机验证.. 3

第 7 章 项目总结.. 3

线下授课时,采用分组教学,每组提交一份项目报告。受疫情影响切换为线上授课时,调整为每个学生独立成组。两种不同形式下学生提交的项目报告截图如下所示。

19003160124蒋文生.zipW 20003160201代英杰.docW 20003160202李天阳.docW 20003160203杨帆.docW 20003160204刘城江.docW 20003160206谷裕.docW 20003160207王龙龙.doc20003160208刁天伟.doc

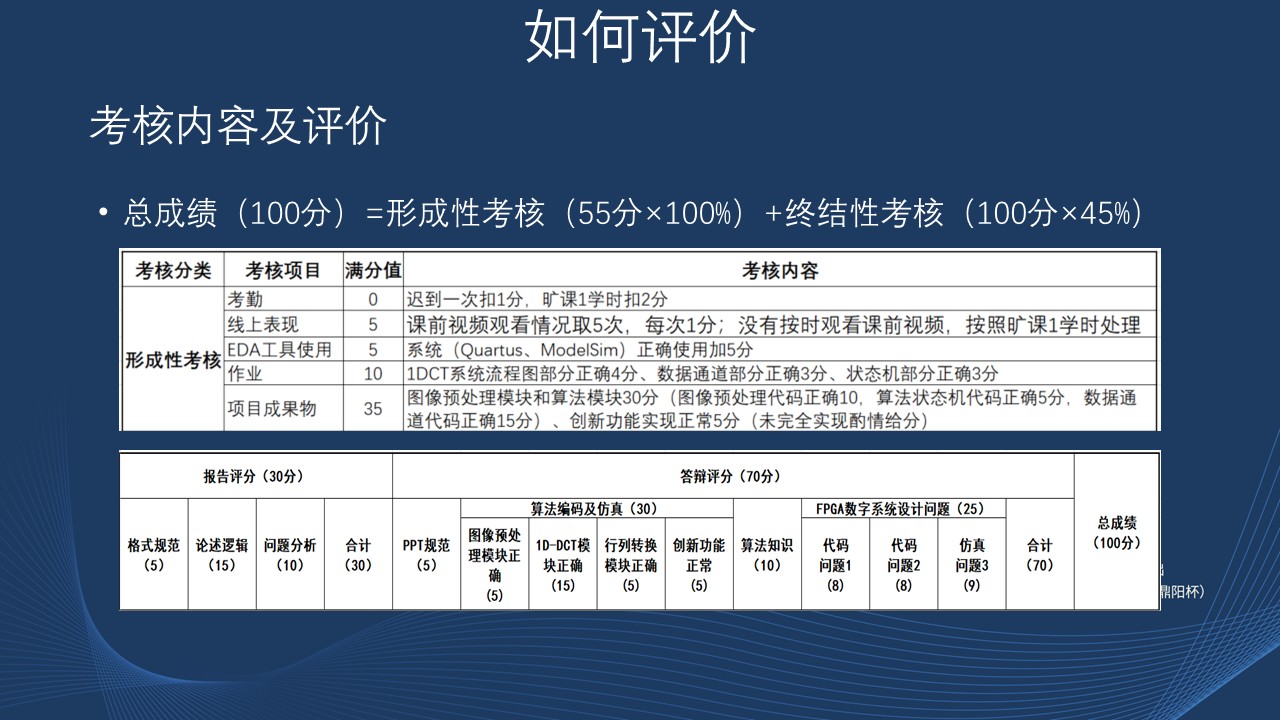

10.考核要求与方法(限 300 字)

1.项目总成绩构成

项目总成绩(100分) $\equiv$ 形成性考核成绩(55分 $\times 1 0 0 %$ ) $^ +$ 终结性考核成绩(100 分 $\times 4 5 %$ )

2.形成性考核与评价

| 考核项目 | 满分值 | 评价标准 |

| 考勤 | 0 | 迟到一次扣1分,旷课1学时扣2分 |

| 线上表现 | 5 | 课前视频观看情况取5次,每次1分;没有按时观看课前视频,按照旷课1学时处理 |

| EDA工具使用 | 5 | 系统(Quartus、ModelSim)正常使用加5分 |

| 作业 | 10 | 1DCT系统流程图部分正确4分、数据通道部分正确3分、状态机部分正确3分 |

| 项目成果物 | 35 | 图像预处理模块和算法模块30分(图像预处理代码正确10,算法状态机代码正确5分,数据通道代码正确15分)、创新功能实现正常5分(未完全实现酌情给分) |

3.终结考核与评价

终结性考核方式 1:答辩 考核时长: 180 分钟

| 报告评分(30分) | 答辩评分(70分) | 总成绩 (100分) | ||||||||||||||||||

| 格式规范 (5) | 论述逻辑 (15) | (10) | 问题分析 | 合计 (30) | PPT规范 | 算法编码及仿真(30) | FPGA数字系统设计问题(25) | |||||||||||||

| 图像预处 | 代码 | 仿真 | 合计 | |||||||||||||||||

| (5) | 理模块正 确 | 1D-DCT模 块正确 | 行列转换 模块正确 | 创新功能 正常 | 算法知识 (10) | 代码 问题1 | 问题2 | 问题3 | (70) | |||||||||||

| (5) | (15) | (5) | (5) | (8) | (8) | (9) | ||||||||||||||

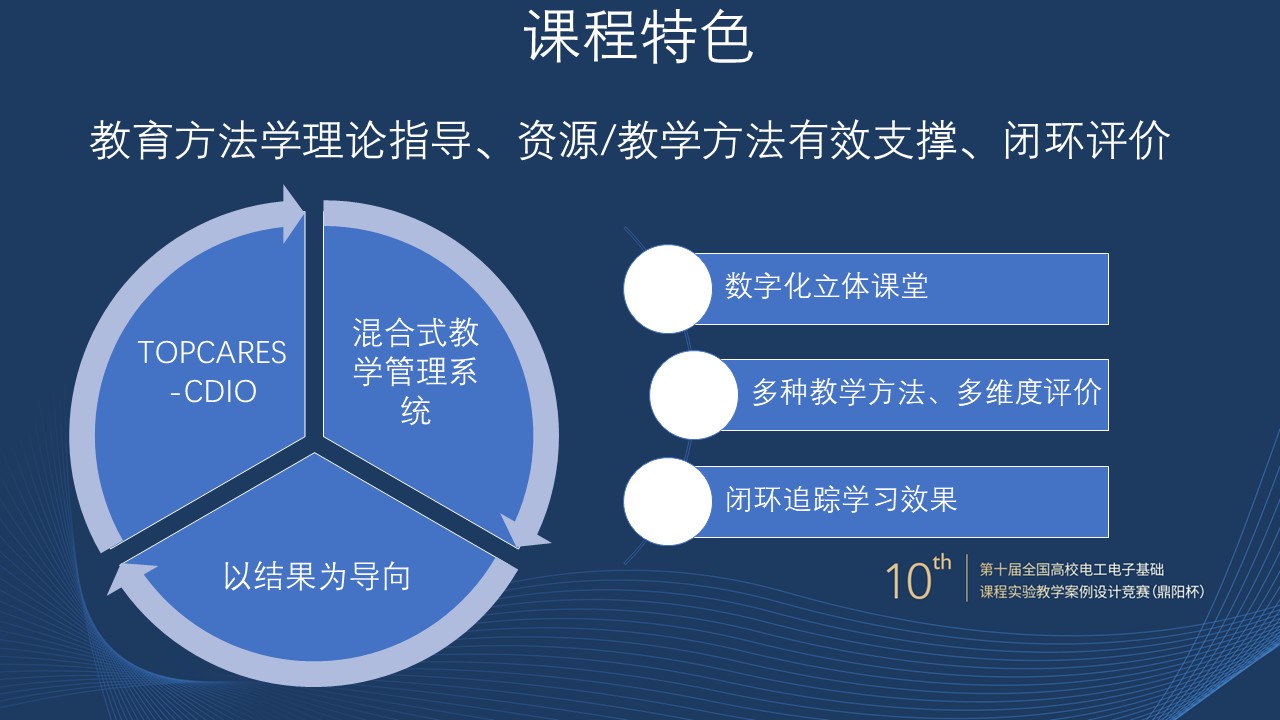

11.项目特色或创新(可空缺,限 150 字)

本项目共有以下几个创新点。

(1)引题。通过布置思考任务,学生在调查讨论的基础上,自行总结项目题目。

(2)课堂组织。采用数字化立体课堂,可以通过数据清晰掌握学生动态,结合隐形思政,调整学生学习状态,调动学习积极性。依托校内学习平台,采用混合式教学模式,课前课中课后均配备相应任务,实现随时/随地可学。平台资源样例可参考下图。

| 序号 | 资源类型 | 资源名称 | 资源介绍 | 操作 | ||

| 课前学习 添加资源资源排序 | ||||||

| 1 | 作业 | 知识回顾及拓展 | 进入作业删除 | |||

| 课中学习 添加资源资源排序 | ||||||

| 课件 | 第3次课重要知识回顾及拓展--控制方式 | 在线版本:第3次课重要知识回顾及拓展--控制方式.pptx | 查看删除 | |||

| 2 | 微课 | 第3次课重要知识回顾及拓展--控制方式 | 微课:第3次课重要知识回顾及拓展--控制方式.mp4 | 查看删除 | ||

| 3 | 课件 | 第4次课重要知识回顾及拓展--VerilogHDL | 在线版本:第4次课重要知识回顾及拓展-VerilogHDL.pptx | 查看删除 | ||

| 4 | 微课 | 第4次课重要知识回顾及拓展--VerilogHDL | 微课:第4次课重要知识回顾及拓展-VerilogHDL.mp4 | 查看删除 | ||

| 课后学习 添加资源资源排序1 作业 VerilogHDL编码 | ||||||

| VerilogHDL编码 | 进入作业删除 | |||||

(3)以学生为中心,采用多种教学方法,调动学生主观能动性,促进理论知识的吸收,提高动手能力。

12. 附录

本项目教学大纲详情如下。

一、 前言

1.项目简介

本项目是集成电路设计与集成系统专业的实践学期二级项目。采取以练为主、以讲为辅的方法,通过实践,培养学生全面掌握基于 FPGA的数字系统设计、验证和优化流程。熟练掌握硬件描述语言的应用和 EDA工具使用的能力。本项目通过分析 JPEG 静态图像压缩算法为基础,按照基于 FPGA 的数字系统设计流程,以 FPGA 为载体来实现算法的硬件电路。在 FPGA 电路的实现过程中,要用到设计、编码、仿真、综合布局布线等过程。除基本颜色空间转换(RGB- ${ \mathrm { . > Y U V } }$ )、离散余弦变换算法外,学生可以根据具体情况选择增加 DCT 结果量化、zig-zag 扫描排序、DC 系数差分脉冲编码调制(DPCM)、AC 系数游程长度编码(RLE)、范式 Huffman 编码等功能。并且进行项目答辩、提交实践学期项目报告一份。本课程与前修课程《高级数字系统设计》、《数字电路》紧密衔接,共同培养学生对数字系统的分析、设计和实践能力;与后续片上系统设计与开发等专业课程相衔接,从而培养学生对数字集成电路的设计与开发能力。

2.项目设计(开发)的基本理念、方法与思路

通过对本专业服务面向的分析,确定了专业培养目标,接着对专业培养目标进行三级分解,并与 TC 能力形成对应,之后确立了本课程开设的必要性。课程的设计,从“知识、能力、素质”出发,采用由课程的培养目标逆向推导出课程的各个环节,包括教学目标、学生预期学习成果、教学内容、实施方式等。使其符合学生的认知规律和职业能力培养规律,并选取典型的学习项目,通过实践训练,逐步培养学生的职业工作能力和自主学习能力。在学生学习完本门课程后对学生的学习效果进行评估、梳理、分析,作为课程持续改进的重要依据。

二、 项目基本信息

1.项目代码:51003P2020

2.项目名称:数字系统设计实践

3.项目英文名称:Digital System Design Project

4.项目类别: 项目 ,混合式教学项目的目标类别 BEII

5.项目来源:

6.授课对象:本科

7.开课单位:智能与电子工程学院

8.先修课程: 数字电路 / 高级数字系统设计

9.学时安排:

| 学分 | 课内总学时 | 理论授课学时 | 随堂实验学时 | 实验室学时 | 课外学时 |

| 4.080.0 | 4.080.0 | 80.0 | 40.0 |

三、 项目预期学习效果

1.项目总体教学目标

通过本实践学期课程的学习,学生能够具有算法分析及数字系统电路设计能力,并学会查阅和加工资料;能够运用数字系统设计方法,能够运用数据通路和控制单元的设计方法,完成基于 FPGA 的数字系统电路设计以及仿真验证,并增加拓展创新功能;能够运用一个完整的数字系统设计流程对本组项目完成情况进行评价,并进行相关技术文档的写作。在实践过程中学会合作,项目交流,培养良好的学习习惯。

2.项目预期学习效果

| 行 | TOPCARES(3级能力指标) | 专业毕业要求 | 课程/项目教学目标或预期学习效果 | 培养路径 | |

| 素 | 2.3.5主动锤炼创新意识 | 集成电路设计茶统 | 能够主动开展创新活动,锤炼创新意识。 | 培养学生良好的学习习惯 | 在课程进行过程中,注重对学生学习习惯的培养和提示,发现问题及时纠正 |

| 知识 | 集成系统专业知识和方设计合处理等过程,提出并践行工程解决方案 | 成系统 | 掌握并应用C语言及数据结构、基础电路的分析与设计、信号与系统等学科专业基1.4.2 能够运用电子信息集成础知识;半导体物理、制造工艺等专业基类学科、集成电路设计与电路础知识;FPGA数字系统设计、数字集成电路设计、测试与验证等专业知识;模拟、法,经过分析、判断和综与集混合集成电路设计、片上系统(SoC)设计等专业知识,经过分析、判断和综合处理等过程,针对集成电路及其相关领域的实际复杂工程问题,提出并践行工程解决方案。 | 评价所设计的系统的时序、功耗等性能指标分析,并优化。 | 采用项目实践,完成性能指标分析过程及 EDA 工具的使用 |

| 运用高级数字系统作业、讨论、自学等设计方法,分析需环节强化分析解决求,设计较复杂数字问题的方法和过系统,并有创新意程,尽量引导学生识; | 通过案例与项目实践相结合,并通过运用高级数字系统作业、讨论、自学等设计方法,分析需环节强化分析解决求,设计较复杂数字问题的方法和过系统,并有创新意程,尽量引导学生主动思考,运用所学知识、方法、工具等解决问题 | ||||

| 综合基于FPGA的数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | ||||

| 运用基础知识解决例、练习、讨论、作实际问题 | 通过课堂讲授案运用基础知识解决例、练习、讨论、作业、项目实践等巩固知识 | ||||

| 能力 | 8.6.5能够应用集成电路设计、验证、测试及集成集成系统开发等专业能力,进行数字集成电路、模拟集设计开发等专业领域多学科成系学背景下复杂工程系统的统构思。 | 电路 | 各能够通过收集、检索、阅读和分析科技资求,设计较复杂数字问题的方法和过料与文献,进行数字集成电路、模拟集成系统,并有创新意程,尽量引导学生成电路、片上系统设计与与集电路、片上系统设计与开发等专业领域多学科背景下复杂工程系统的构思。 | 运用高级数字系统作业、讨论、自学等设计方法,分析需环节强化分析解决识; | 通过案例与项目实践相结合,并通过运用高级数字系统作业、讨论、自学等设计方法,分析需环节强化分析解决主动思考,运用所学知识、方法、工具等解决问题 |

| 综合基于FPGA的数通过课堂讲授案字系统设计与验证例、练习、讨论、项流程,包括系统设目实践等巩固知识 | 综合基于FPGA的数通过课堂讲授案字系统设计与验证例、练习、讨论、项流程,包括系统设目实践等巩固知识 | ||||

| TOPCARES(3级能力指标) | 专业毕业要求 | 课程/项目教学目标或预期学习效果 | 培养路径 | ||

| 计、仿真验证、物理电路验证,以及设计的迭代过程。 | |||||

| 运用基础知识解决例、练习、讨论、作实际问题 | 通过课堂讲授案运用基础知识解决例、练习、讨论、作业、项目实践等巩固知识 | ||||

| 能力 | 8.7.7 能够应用集成电路设计、验证、测试及集成集成行数字集成电路、模拟集成电路、片上系统设计与开发等专业领域多学科成系景下复杂工程系统的设计。背景下复杂工程系统的统设计。 | 系统开发等专业能力,进电路能够通过框图、流程图、状态图、原理图设计等,进行数字集成电路、模拟集成电路、与集片上系统设计与开发等专业领域多学科背开发等专业领域多学科成系景下复杂工程系统的设计。 | 运用高级数字系统作业、讨论、自学等设计方法,分析需环节强化分析解决求,设计较复杂数字问题的方法和过系统,并有创新意程,尽量引导学生识; | 通过案例与项目实践相结合,并通过运用高级数字系统作业、讨论、自学等设计方法,分析需环节强化分析解决求,设计较复杂数字问题的方法和过系统,并有创新意程,尽量引导学生主动思考,运用所学知识、方法、工具等解决问题 | |

| 运用 Verilog HDL对组合逻辑电路和时序逻辑电路进行建模; | 通过项目实践,强化语言的使用方法和规则 | ||||

| 综合基于FPGA的数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | ||||

| 运用基础知识解决例、练习、讨论、作实际问题 | 通过课堂讲授案运用基础知识解决例、练习、讨论、作业、项目实践等巩固知识 | ||||

| 能力 | 8.8.7能够应用集成电路设计、验证、测试及集成系统开发等专业能力,实电路施数字集成电路、模拟集成电路、片上系统设计与开发等专业领域多学科背景下复杂工程系统设统计。 | 集成设计与集成系 | 能够通过使用集成电路设计EDA工具、常用实验仪器设备和电子元器件等,实施数字集成电路、模拟集成电路、片上系统设计与开发等专业领域多学科背景下复杂工程系统设计。 | 综合基于FPGA的数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 |

| 运用 EDA工具,将采用项目实践,学所设计的系统,下载生进行实验探索,到FPGA开发板,实完成物理电路下现物理电路,并完成载、调试过程;完成调试等。 | 运用 EDA工具,将采用项目实践,学所设计的系统,下载生进行实验探索,到FPGA开发板,实完成物理电路下现物理电路,并完成载、调试过程;完成小车外围电路的焊 | ||||

| 中 | TOPCARES(3级能力指标) | 专业毕业要求 | 课程/项目教学目标或预期学习效果 | 培养路径 | |

| 接及调试过程。 | |||||

| 运用基础知识解决例、练习、讨论、作实际问题 | 通过课堂讲授案运用基础知识解决例、练习、讨论、作业、项目实践等巩固知识 | ||||

| 运用Verilog HDL 搭建仿真环境,编写Testbench,评价系统仿真验证结果; | 通过项目实践,尽量引导学生主动思考,强化仿真验证方法及EDA工具的使用方法 | ||||

| 前 | 8.9.7能够应用集成系统开发等专业能力,运行片上系统设计与开发领域多学科背景下复杂工程系统。 | 集成电路设计与集成系统 | 能够应用基于FPGA的数字系统设计、片上系统设计与开发等专业能力,运行多学科背景下的复杂工程系统。 | 评价所设计的系统的时序、功耗等性能指标分析,并优化。 | 采用项目实践,完成性能指标分析过程及 EDA 工具的使用 |

| 综合基于FPGA的数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | ||||

| 运用基础知识解决例、练习、讨论、作实际问题 | 通过课堂讲授案运用基础知识解决例、练习、讨论、作业、项目实践等巩固知识 | ||||

KT 点设计

| KT编号 | 内容 | 对应布鲁姆目标掌握程度 | 是香重点 | 难易度 | 是香学 | 关键前修KT点编号 |

| KT1 | 介绍实现基于FPGA的 JPEG图像压缩算法所要完成的工作,并作项目效果演示。 | 2. 理 解(Understand) | 否 | 中 | 否 | |

| KT2 | 简单时序控制方式的讲解 | 2. 理 解(Understand) | 否 | 中 | 否 | |

| KT3 | VerilogHDL语法回顾 | 1. 识 记(Remember) | 否 | 易 | 是 | |

| KT4 | 根据系统需求设计合理的 FPGA 电路模块图 | 4.分析(Analyze) | 是 | 中 | 否 | KT1_介绍实现基于FPGA的JPEG图像压缩算法所要完成的工作,并作项目效果演示。 |

| KT编号 | 内容 | 对应布鲁姆目标掌握程度 | 是否重点 | 难易度 | 是香自学 | 关键前修KT点编号 |

| KT5 | 图像预处理模块及DCT算法流程图设计 | 3.运用(Apply) | 是 | 中 | 香 | KT1_介绍实现基于FPGA的JPEG图像压缩算法所要完成的工作,并作项目效果演示。KT2_简单时序控制方式的讲解 |

| KT6 | 详细电路设计 | 6.创造(Create) | 是 | 难 | 否 | KT1_介绍实现基于FPGA的 JPEG图像压缩算法所要完成的工作,并作项目效果演示。KT2_简单时序控制方式的讲解KT4_根据系统需求设计合理的 FPGA 电路模块图KT5_图像预处理模块及DCT算法流程图设计 |

| KT7 | 电路VerilogHDL 实现。 | 3.运用(Apply) | 是 | 中 | 否 | KT3_VerilogHDL语法回顾 |

| KT8 | 搭建仿真环境,在ModelSim中对电路功能进行仿真 | 5.评价(Evaluate)是 | 中 | 否 | KT1_介绍实现基于FPGA的JPEG图像压缩算法所要完成的工作,并作项目效果演示。KT3_VerilogHDL语法回顾KT4_根据系统需求设计合理的 FPGA 电路模块图KT5_图像预处理模块及DCT算法流程图设计KT6_详细电路设计KT7_电路 VerilogHDL 实现。 | |

| KT9 | 在QuartusII中,对电路进行管脚分配、时序设置及综合、完成布局布线3.运用(Apply)和生成编程文件 | 香 | 中 | 否 | KT4_根据系统需求设计合理的 FPGA 电路模块图KT7_电路 VerilogHDL 实现。 | |

| KT10 | 撰写项目总结报告、准备答辩 PPT。3.运用(Apply) | 否 | 易 | 是 | KT1_介绍实现基于FPGA的 JPEG图像压缩算法所要完成的工作,并作项目效果演示。KT2_简单时序控制方式的讲解KT3_VerilogHDL语法回顾KT4_根据系统需求设计合理的 FPGA 电路模块图KT5_图像预处理模块及DCT算法流程图设计KT6_详细电路设计KT7_电路 VerilogHDL 实现。KT8_搭建仿真环境,在ModelSim中对电路功能进行仿真KT9_在QuartusII中,对电路进行管脚分配、时序设置及综合、完成布局布线和生 | |

| KT编号 | 内容 | 对应布鲁姆目标掌握程度 | 是否重点 | 难易程健 | 学 | 关键前修KT点编号 |

| 成编程文件 |

KT 点与预期学习效果映射

| 目标 | TOPCARES(3级能力指标) | 专业毕业要求 | 课程/项目教学目标或预期学习效果 | 培养路径 | 对应的KT编号 |

| 素质 | 2.3.5主动锤炼创新意识 | 意识。 | 习习惯 | 在课程进行过程中,注重对学4_根据系统需求设培养和提示,发路模块图现问题及时纠6_详细电路设计正 | 程中,注重对学4_根据系统需求设现问题及时纠6_详细电路设计 |

| 知识 | 1.4.2 能够运用电子信息理、制造工艺等专业基础知识;类学科、集成电路设计FPGA数字系统设计、数字集成电与集成系统专业知识和路设计、测试与验证等专业知识;方法,经过分析、判断和模拟、混合集成电路设计、片上系并践行工程解决方案 | 掌握并应用C语言及数据结构、基础电路的分析与设计、信号与系统等学科专业基础知识;半导体物1.4.2 能够运用电子信息理、制造工艺等专业基础知识;类学科、集成电路设计FPGA数字系统设计、数字集成电与集成系统专业知识和路设计、测试与验证等专业知识;方法,经过分析、判断和模拟、混合集成电路设计、片上系综合处理等过程,提出统(SoC)设计等专业知识,经过综合基于FPGA的分析、判断和综合处理等过程,针数字系统设计与验对集成电路及其相关领域的实际证流程,包括系统复杂工程问题,提出并践行工程解设计、仿真验证、决方案。 | 运用基础知识解决实际问题 | 通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电论、作业、项目路模块图实践等巩固知5_图像预处理模块识 | 2_简单时序控制方式的讲解3_VerilogHDL语法回顾通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电实践等巩固知5_图像预处理模块及DCT算法流程图设计6_详细电路设计7_电路VerilogHDL实现。 |

| 物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | 6_详细电路设计7_电路VerilogHDL实现。8_搭建仿真环境,在 ModelSim 中对电路功能进行仿真9_在 QuartusII 中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成编程文件 | |||

| 求,设计较复杂数并通过作业、讨路模块图 | |||||

| 目标类 | TOPCARES(3级能力指标) | 专业毕业要求 | 课程/项目教学目标或预期学习效果 | 培养路径 | 对应的KT编号 |

| 意识; | 强化分析解决及DCT算法流程图问题的方法和设计过程,尽量引导6_详细电路设计学生主动思考,运用所学知识、方法、工具等解决问题 | 强化分析解决及DCT算法流程图过程,尽量引导6_详细电路设计,7_电路 VerilogHDL实现。 | |||

| 评价所设计的系统的时序、功耗等性能指标分析,并优化。 | 采用项目实践,9_在QuartusII中,完成性能指标对电路进行管脚分分析过程及配、时序设置及综EDA 工具的使合、完成布局布线用 | 采用项目实践,9_在QuartusII中,完成性能指标对电路进行管脚分分析过程及配、时序设置及综EDA 工具的使合、完成布局布线和生成编程文件 | |||

| 能力 | 8.6.5能够应用集成电路设计、验证、测试及集成系统开发等专业能力,进行数字集成电路、模拟集成电路、片上系统设计与开发等专业领域多学科背景下复杂工程系统的构思。 | 能够通过收集、检索、阅读和分析科技资料与文献,进行数字集成电路、模拟集成电路、片上系统设计与开发等专业领域多学科背景下综合基于FPGA的复杂工程系统的构思。 | 运用基础知识解决实际问题 | 通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电论、作业、项目路模块图实践等巩固知5_图像预处理模块识 | 2_简单时序控制方式的讲解3_VerilogHDL 语法回顾通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电实践等巩固知5_图像预处理模块及DCT算法流程图设计6_详细电路设计7_电路VerilogHDL实现。 |

| 数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | 6_详细电路设计7_电路VerilogHDL实现。8_搭建仿真环境,在 ModelSim 中对电路功能进行仿真9_在 QuartusII 中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成编程文件 | |||

| 求,设计较复杂数并通过作业、讨路模块图意识; | 强化分析解决及DCT算法流程图 | 强化分析解决及DCT算法流程图 | |||

| TOPCARES(3级能力指标) | 专业毕业要求 | 课程/项目教学目标或预期学习效果 | 培养路径 | 对应的KT编号 | |

| 问题的方法和过程,尽量引导6_详细电路设计学生主动思考,运用所学知识、方法、工具等解决问题 | □设计过程,尽量引导6_详细电路设计7_电路VerilogHDL实现。 | ||||

| 力 | 8.7.7能够应用集成电路设计、验证、测试及集成系统开发等专业能力,进行数字集成电路、模拟集成电路、片上系统设计与开发等专业领域多学科背景下复杂工程系统的设计。 | 能够通过框图、流程图、状态图、综合基于FPGA的原理图等,进行数字集成电路、模数字系统设计与验拟集成电路、片上系统设计与开发证流程,包括系统等专业领域多学科背景下复杂工设计、仿真验证、程系统的设计。 | 运用基础知识解决实际问题 | 通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电论、作业、项目路模块图实践等巩固知5_图像预处理模块识 | 2_简单时序控制方式的讲解3_VerilogHDL语法回顾通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电实践等巩固知5_图像预处理模块及DCT算法流程图设计6_详细电路设计7_电路 VerilogHDL实现。 |

| 物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | 6_详细电路设计7_电路 VerilogHDL实现。8_搭建仿真环境,在 ModelSim 中对电路功能进行仿真9_在 QuartusII 中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成编程文件 | |||

| 运用高级数字系统字系统,并有创新过程,尽量引导设计意识; | 通过案例与项目实践相结合,4_根据系统需求设并通过作业、讨计合理的 FPGA 电论、自学等环节路模块图学生主动思考,6_详细电路设计运用所学知识、方法、工具等解实现。决问题 | 目实践相结合,4_根据系统需求设并通过作业、讨计合理的 FPGA 电学生主动思考,6_详细电路设计7_电路VerilogHDL | |||

| 运用Verilog HDL对组合逻辑电路和时序逻辑电路进行建模; | 通过项目实践,强化语言的使用方法和规则 | 3_VerilogHDL 语法回顾7_电路VerilogHDL实现。 | |||

| 力 | 8.8.7能够应用集成电路设计、验证、测试及集成能够通过使用集成电路设计 EDA系统开发等专业能力,设计与开发等专业领域专业领域多学科背景下复杂工程多学科背景下复杂工程系统设计。系统设计。 | 设计、验证、测试及集成能够通过使用集成电路设计 EDA工具、常用实验仪器设备和电子元能实施数字集成电路、模器件等,实施数字集成电路、模拟拟集成电路、片上系统集成电路、片上系统设计与开发等设计与开发等专业领域专业领域多学科背景下复杂工程 | 运用基础知识解决实际问题 | 通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电论、作业、项目路模块图实践等巩固知5_图像预处理模块识 | 2_简单时序控制方式的讲解3_VerilogHDL 语法回顾通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电实践等巩固知5_图像预处理模块及DCT算法流程图设计6_详细电路设计7_电路 VerilogHDL实现。 |

| 综合基于FPGA的数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | 6_详细电路设计7_电路 VerilogHDL实现。8_搭建仿真环境,在ModelSim中对电路功能进行仿真9_在QuartusII 中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成编程文件 | |||

| 运用Verilog HDL搭建仿真环境,编写 Testbench,评价系统仿真验证结果; | 通过项目实践,尽量引导学生主动思考,强化仿真验证方法及 EDA工具的使用方法 | 8_搭建仿真环境,在 ModelSim 中对电路功能进行仿真 | |||

| 并完成调试等。 | 采用项目实践,外围电路的焊和生成编程文件接及调试过程。 | 外围电路的焊和生成编程文件 | |||

| 目标分类 | TOPCARES(3级能力指标) | 专业毕业要求 | 课程/项目教学目标或预期学习效果 | 培养路径 | 对应的KT编号 |

| 能 | 8.9.7能够应用集成系统开发等专业能力,运行片上系统设计与开发领域多学科背景下复杂工程系统。 | 能够应用基于 FPGA 的数字系统设计、片上系统设计与开发等专业能力,运行多学科背景下的复杂工程系统。 | 运用基础知识解决实际问题 | 通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电论、作业、项目路模块图实践等巩固知5_图像预处理模块识 | 2_简单时序控制方式的讲解3_VerilogHDL 语法回顾通过课堂讲授4_根据系统需求设案例、练习、讨计合理的 FPGA 电实践等巩固知5_图像预处理模块及DCT算法流程图设计6_详细电路设计7_电路VerilogHDL实现。 |

| 综合基于FPGA 的数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 通过课堂讲授案例、练习、讨论、项目实践等巩固知识 | 6_详细电路设计7_电路VerilogHDL实现。8_搭建仿真环境,在 ModelSim 中对电路功能进行仿真9_在 QuartusII 中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成编程文件 | |||

| 评价所设计的系统的时序、功耗等性能指标分析,并优化。 | 采用项目实践,9_在QuartusI中,完成性能指标对电路进行管脚分分 析过程及配、时序设置及综EDA工具的使合、完成布局布线用 | 采用项目实践,9_在QuartusI中,完成性能指标对电路进行管脚分分 析过程及配、时序设置及综EDA工具的使合、完成布局布线和生成编程文件 |

四、 教学内容与要求

第一单元 项目介绍和分析

1.教学内容与要求

| 知识点(群)与技能点(能力) | 对应掌握程度 | 重点否 | 难易程度 | 自学否 |

| KT1_介绍实现基于FPGA的JPEG 图像压缩算法所要完成的工作,并作项目效果演示。 | 2. 理 解(Understand) | 香 | 中 | 香 |

2.教学实施建议

主要通过课件、微视频、讨论,分组实践等方式,实现对项目要求的理解,鼓励学生课下通过查阅各种线上线下资源,完成自主学习与知识回顾过程,加深印象,为本门课程的实践奠定基础。 本单元的混合式教学概要设计: (1)课前:视频 2 个 (2)课中:视频 2 个、课件 (3)课后:视频 2 个、作业1 套

第二单元 重要知识回顾及拓展

1.教学内容与要求

| 知识点(群)与技能点(能力) | 对应掌握程度重点否难易程度自学否 | 重点否 | 难易程度 | 自学否 |

| KT2_简单时序控制方式的讲解 | 2.理解(Understand)否 | 中 | 否 | |

| KT3_VerilogHDL语法回顾 | 1.识记(Remember)否 | 否 | 易 | 是 |

2.教学实施建议

主要通过线上的方式,实现对时序控制原理的理解,鼓励学生参考线上资源和课下通过查阅资料,进一步理解 RAM读写操作时序、乒乓操作、流水线控制方式的原理及 VerilogHDL实现方法;理解时序电路、组合电路模块、状态机的描述方式,实例化方法。 本单元的混合式教学概要设计:(1)课前:视频7 个 (2)课中:视频 7 个、课件 (3)课后:视频 7 个、作业 1 套

第三单元 系统设计及实现

1.教学内容与要求

| 知识点(群)与技能点(能力) | 对应掌握程度 | 重点否 | 难易程度 | 自学否 |

| KT5_图像预处理模块及DCT算法流程图设计3.运用(Apply)是 | 3.运用(Apply) | 否 | ||

| KT6_详细电路设计 | 6.创造(Create)是 | 难 | 香 | |

| KT7_电路 VerilogHDL 实现。 | 3.运用(Apply)是 | 中 | 香 |

2.教学实施建议

主要通过课上案例讲授、讨论、实验等方式,使学生对高级数字系统设计方法,有一个更加深入的认识,着重分析实际问题、解决实际问题的方法,引导学生线上和线下主动思考,完成模块划分、流程图的设计及 VerilogHDL 实现,帮助学生及时发现问题,及时纠正问题,提高熟练程度。同时,培养良好的学习习惯。 本单元的混合式教学概要设计: (1)课前:视频 10 个 (2)课中:视频 10 个、课件 (3)课后:视频 10 个、作业 2 套第四单元 系统仿真验证及联合调试

1.教学内容与要求

| 知识点(群)与技能点(能力) | 对应掌握程度 | 重点否 | 难易程度 | 自学否 |

| KT8_搭建仿真环境,在ModelSim中对电路功能进行仿真 | 5.(Evaluate) | 是 | 中 | 香 |

| KT9_在QuartusII中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成编程文件 | 3.运用(Apply) | 否 | 中 | 否 |

2.教学实施建议

主要通过课上案例讲授、讨论等方式,使学生对电路仿真方法,有一个更加深入的认识,着重分析实际问题、解决实际问题的方法,引导学生线上和线下主动思考,完成仿真过程及综合布局布线和时序功耗分析过程,帮助学生及时发现问题,及时纠正问题,提高熟练程度。 本单元的混合式教学概要设计: (1)课前:视频 1 个 (2)课中:视频1 个、课件 (3)课后:视频1 个

第五单元 技术报告和答辩

1.教学内容与要求

| 知识点 (群)与技能点(能力) | 对应掌握程度 | 重点否 | 难易程度 | 自学否 |

| KT10_撰写项目总结报告、准备答辩 PPT。3.运用(Apply)否 | 3.运用(Apply) | 易 | 是 |

2.教学实施建议

主要通过查阅资料、课上讲授、讨论等方式,实现对设计的总结,并撰写成项目报告。

五、项目实施计划表

| 项目单元代码 | 项目单元名称项目内容 | 项果 | 课内 | ||

| UP(1) | 析 | 项目介绍和分介绍实现基于FPGA 的 JPEG 图像压缩算法所要完成的工作,并作项目效果演示。 | 设计文档 | 课堂 | |

| UP(2) | 重要知识回顾及拓展 | 简单时序控制方式的讲解,VerilogHDL 语法回顾 | 设计文档 | 课堂 | |

| UP(3) | 现 | 系统设计及实根据系统需求设计合理的FPGA 电路模块图、图像预处理及DCT算法流设 计程图,并完成详细电路设计及VerilogHDL实现。 | 文档 | 课堂 | |

| UP(4) | 及联合调试 | 系统仿真验证搭建仿真环境,在ModelSim 中对电路功能进行仿真、对电路进行管脚分配、时序设置及综合、在QuartusII中完成布局布线。 | 设计文档 | 课堂 | |

| UP(5) | 技术报告和答辩 | 撰写项目总结报告、准备答辩 | 设计文档 | 课堂 | |

| 合计 | 0.0 | ||||

六、 项目考核与评价

1.项目总成绩构成

项目总成绩(100 分) $\equiv$ 形成性考核成绩(55 分 $\times 1 0 0 %$ ) $^ +$ 终结性考核成绩(100 分 $\times 4 5 %$ )

2.形成性考核与评价

| 考核项目 | 促进的预期学习效果 | 评价标准 | 备注 | ||

| 考勤0培养学生良好的学习习惯 | 迟到一次扣1分,旷课1学时扣2分 | 扣分制,扣分上限不超过20分 | |||

| 课堂表现 | 0 | 培养学生良好的学习习惯 | 回答问题、课堂纪律等 | ||

| 线上表现 | 5 | 培养学生良好的学习习惯 | 课前视频观看情况取5次,每次1分;没有按时观看课前视频,按照旷课1学时处理 | ||

| EDA工具5使用 | 运用VerilogHDL 搭建仿真环境,编写 Testbench,评价系统仿真验证结果;运用 EDA工具,将所设计的系统,下载到FPGA开发板,实现物理电路,并完成调试等。 | 系统(Quartus、ModelSim)正常使用加5分 | |||

| 作业 | 10 | 运用高级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识; | 1DCT系统流程图部分正确4分、数据通道部分正确3分、状态机部分正确3分 | ||

| 项目物 | 运用基础知识解决实际问题 综合基于 FPGA 的数字系统设计图像预处理模块和算法模块 30与验证流程,包括系统设计、仿真验证、物理电路验证,以及分(图像预处理代码正确10,算成 果35设计的迭代过程。运用高级数字系统设计方法,分析需求,设法状态机代码正确5分,数据通计较复杂数字系统,并有创新意识;运用VerilogHDL对组合道代码正确15分)、创新功能实逻辑电路和时序逻辑电路进行建模;运用VerilogHDL 搭建仿现正常5分(未完全实现酌情给 | ||||

| 真环境,编写Testbench,评价系统仿真验证结果;运用EDA分)工具,将所设计的系统,下载到FPGA开发板,实现物理电路,并完成调试等。评价所设计的系统的时序、功耗等性能指标分析,并优化。 |

3.终结考核与评价

终结性考核方式 1:答辩 考核时长: 180 分钟

| 预期学习效果 | 知识点(群)与技能点(能力) | 对应掌握程度 | 是否难中重点 | 是否难中易 | 所占比例 | 备注 |

| 运用基础知识解决实际问题 | 简单时序控制方式的讲解 VerilogHDL语法回顾 根据系统需求设计合理的FPGA 电路模块图图像预处理模块及DCT 算法流程图设计 详细电路设计 电路 VerilogHDL 实现。 | 2.理解(Understand) 1.识记否(Remember)4.分析是(Analyze) 3.运用(Apply)6.是创造(Create)3.运用(Apply)是 | 香是 | 中易中中难中 | 0.20 | |

| 综合基于 FPGA 的数字系统设计与验证流程,包括系统设计、仿真验证、物理电路验证,以及设计的迭代过程。 | 详细电路设计 电路 VerilogHDL 实现。搭建仿真环境,在ModelSim中对电路功6.创造(Create)3.运用能进行仿真 在 QuartusII 中,对电路进行(Apply)5.评价(Evaluate) 3.管脚分配、时序设置及综合、完成布局布运用(Apply)线和生成编程文件 | 是是是香 | 难中中中 | 0.15 | ||

| 运用高级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识; | 根据系统需求设计合理的 FPGA 电路模块图 图像预处理模块及 DCT 算法流程图设计 详细电路设计 电路 VerilogHDL实现。 | 4.分析(Analyze)3.运用(Apply)6.创造(Create)3.运用(Apply) | 是是是是 | 中中难中 | 0.15 | |

| 运用 Verilog HDL对组合逻辑电路和时序逻辑电路进行建模; | VerilogHDL 语法回顾 电路 VerilogHDL1.识记(Remember)3.运用否实现。 | (Apply) | 是 | 易中 | 0.12 | |

| 运用Verilog HDL搭建仿真环境,编写 Testbench,评价系统仿真验证结果; | 搭建仿真环境,在 ModelSim 中对电路功能进行仿真 | 5.评价(Evaluate) | 0.2 | |||

| 运用 EDA工具,将所设计的系统,下载到 FPGA开发板,实现物理电路,并完成调试等。 | 在 QuartusII中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成3.运用(Apply)编程文件 | |||||

| 评价所设计的系统的时序、在QuartusII中,对电路进行管脚分配、化。 | 评价所设计的系统的时序、在QuartusII中,对电路进行管脚分配、功耗等性能指标分析,并优时序设置及综合、完成布局布线和生成3.运用(Apply)编程文件 | 香 | 中0.05 | 中0.05 | ||

| 培养学生良好的学习习惯 | 根据系统需求设计合理的 FPGA 电路模4.分析(Analyze)6.创造是块图 详细电路设计 | (Create) | 是 | 中难 | 0.16 |

按照《学生参加学科竞赛加分奖励办法(试行)》(东软校教发〔2012〕20 号)文件执行。

七、 教学方法与教学手段

1.教学方法

讨论教学法 、 练习教学法 、 实验教学法 、 案例教学法

2.教学手段

本课程主要采用讨论教学法、练习教学法、实验教学法、案例教学法等多种教学方法,辅助采用多媒体等现代教学方法,充分结合线上、线下,调动学生学习兴趣,促进学生积极思考与实践,进而促进学生职业能力的提高。

1、讨论法:在教师的指导下,学生以全班或小组为单位,围绕项目的中心问题,各抒己见,通过讨论或辩论活动,获得知识或巩固知识的一种教学方法。

2、练习教学法:学生在教师的指导下巩固知识、运用知识、形成技能技巧的方法。

3、实验教学法:在教师的指导下,学生以小组为单位,通过实验操作进行研究和学习方法

4、案例教学法:教师提出案例,鼓励学生积极参与讨论,引导学生一步步找到解决方案。

八、 教材及课程资源

1.教材及参考书

《FPGA 设计实例教程》,山丹等,东软电子出版社,ISBN ,2016-1-1,T-C 教材

《高级数字系统设计与 VerilogHDL》,山丹,东软电子出版社,ISBN ,2019-2-8,T-C 教材

《高级数字系统设计》,孙晓凌,,ISBN ,2016-3-16,自编讲义

《项目指导书》,山丹、丛国涛、张晓旭,,2020-5-25

2.课程资源的开发与利用

(1) 项目指导书:项目开始时,线上发布发给学生,作为整个项目的指导。(2) 外围电路资料:介绍外围电路模块时,线上发布

(3) 微视频:共9 个,在相应课次前线上发布

(4) 测试题库:涵盖5 次线上

(5) 作业题库:涵盖5 次线上

(6) 问题库:涵盖5 次线上

(7) 答辩题库:最后答辩时使用

(8) Demo 基础设计 $^ +$ 代码:数字系统 VerilogHDL实现之初给出,可参考(9) 创新功能样例框架:共3 个,基本功能实现后,线上给出

(10) 参考文献

九、 学习策略与技巧

| 预期学习效果 | 知识点(群)与技能点(能力) | 对应掌握程度 | 是否重点 | 中 | 学习任务/活动简要设计 | 周周 | 周周 | 起结学习指导、始束学习支架设计等 | |

| 培养学生良好的学习习惯培养学生良好的学习习惯 | 根据系统需求设计合理的 FPGA 电路模块图 详细电路设计 | 4.分析(Analyze)是6.创造(Create) | 中 | 线上表现 | 课前视频观看情况取5次,每次1分;没有按时观看课前视频,按照旷课1学时处理 | 学生通过PPT、实验指导书、视频等预习项目所需知识,课上进行提问或测试,并辅助以QQ群答疑,完成线上学习在线指导等。 | |||

| 运用 EDA工具,将所设计的在QuartusII中,对电路系统,下载到FPGA开发板,进行管脚分配、时序设置等。运用 Verilog HDL搭建生成编程文件 搭建仿真评价(Evaluate)仿真环境,编写 Testbench,评价系统仿真验证结果; | 运用 EDA工具,将所设计的在QuartusII中,对电路系统,下载到FPGA开发板,进行管脚分配、时序设置环境,在 ModelSim 中对电路功能进行仿真 | 是R | R | R | 完成Quartus 和ModelSim软件安装 | 学生通过查阅资料及软件安装文档和视频等完成安装过程,课上逐个检查,并辅助以QQ群答疑,完成在线指导等。 | |||

| 运用高级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识;运用高级数字系统设计方法,分析需求,设计较复杂数字析需求,设计较复杂数字系FPGA 电路模块图 详细造(Create)统,并有创新意识;运用高!级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识; | 电路VerilogHDL 实现。图像预处理模块及DCT3.运用(Apply)3.是电路设计 | 是是 | 中中中难 | 作业 | 1DCT系统流程图设计、数据通道和状态机电路设计 | 学生通过PPT、实验指导书、视频、课上讲授等完成项目设计,课上进行分组展示、点评、提问,并辅助以QQ群答疑,完成线上学习在线 | |||

| 预期学习效果 | 知识点(群)与技能点(能力) | 对应掌握程度 | 1 | 学习任务/活动简要设计 | 起结学习指导、始東学习支架设计等 | ||||

| 指导等。 | |||||||||

| 运用VerilogHDL对组合逻辑电路和时序逻辑电路进行建模;运用基础知识解决实际问题 运用 EDA工具,将所设计的系统,下载到FPGA开发板,实现物理电路,并完成调试等。运用高级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识;运用高级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识;运用高级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识;运用VerilogHDL 搭建仿真环境,编写 Testbench,评价系统仿真验证结果;运用高级数字系统设计方法,分析需求,设计较复杂数字系统,并有创新意识; | VerilogHDL语法回顾简单时序控制方式的讲解在 QuartusII 中,对电路进行管脚分配、时序设置及综合、完成布局布线和生成编程文件电路VerilogHDL 实现。图像预处理模块及 DCT 算法流程图设计根据系统需求设计合理的 FPGA 电路模块图 搭建仿真环境,在 ModelSim 中对电路功能进行仿真 详细电路设计 | 识 记(Remember) 2.理解(Understand) 3.运用(Apply) 3.运用(Apply)3.运用(Apply)4.分析(Analyze)5.评价(Evaluate) 6.创造(Create) | 香否否是是是 | 项目成果物 | 图像预处理模块和算法模块的数据通道和状态机1VerilogHDL代码设计,以及创新功能实现 | 4 | 学生通过PPT、实验指导书、视频、课上讲授等完成代码设计,并辅助以QQ群答疑,完成线上学习在线指导等。 | ||

十、 课程教学基本条件

(一)任课教师基本要求

专任教师的学历层次为硕士以上,具有较好的电子技术方面的专业知识,具有较好的数字系统设计、调试能力,能够用清晰简洁的专业语言讲授理论知识,具有较高的理论和实践教学能力,具有运用各种教学方法与手段的能力。

(二)教学设施要求

学生实验除仿真验证外,提供专用实验室“数字系统设计实验室”完成物理电路实现,提供资源丰富的 FPGA 开发板资源,供学生学习使用,并配备具有多年实践教学经验的教师,全程指导、辅助学生完成实验。

十一、 质量保障措施

1、 信息员反馈机制

课程实施过程中,采取信息员机制,学生可以随时对课程进展情况,包括速度、难易程度、接受情况、期望等进行反

馈,教师根据学生反馈调整课程进展,力求最大限度提高学生的学习效果。

2、 成绩分析及总结

课程考核结束后,对形成性考核和终结性考核成绩进行分析,梳理、总结,学生能力达成情况可进行定量计算,之后,分析原因及对策,反馈作用于下一轮的大纲制定以及教学的各个环节。在课程实施后对成绩进行分析,挑选好、中、差,每个分数段,按学生人数比例选择分析对象,进行统计,得出目标能力达成度。