基于FPGA的Reed-Solomon编码及显示

实验题目:基于 FPGA 的 Reed-Solomon 编码及显示

1. 课程简要信息

课程名称:数字电子技术基础实验

课程学时:课内 20学时,课外20学时

适用专业:自动化、智能电网、测控

学生年级: 自动化 1703、04 班,2018-2019(2);智能电网 1801、02、03 班,2019-2020(1);测控 1801、02 班,2019-2020(2)

2. 实验内容与任务

2.1 设计由本原多项式 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ 定义的有限域 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 内乘法运算电路

2.2 设计由本原多项式 $f ( x ) = x ^ { 8 } + x ^ { 7 } + x ^ { 2 } + x + 1$ 定义的有限域 $\mathrm { G F } ( 2 ^ { 8 } )$ 内乘 法运 算电路

2.3 设计由本原多项式 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ 定义的有限域 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 内 Reed-Solomon 编码器

2.4 设计1 位数码管显示电路显示 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 内所有域元素

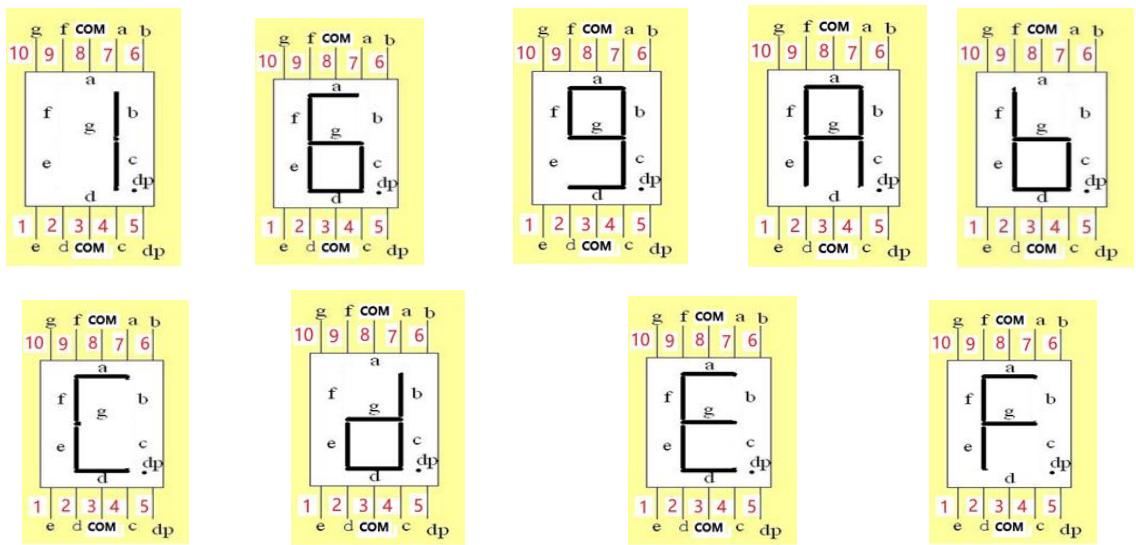

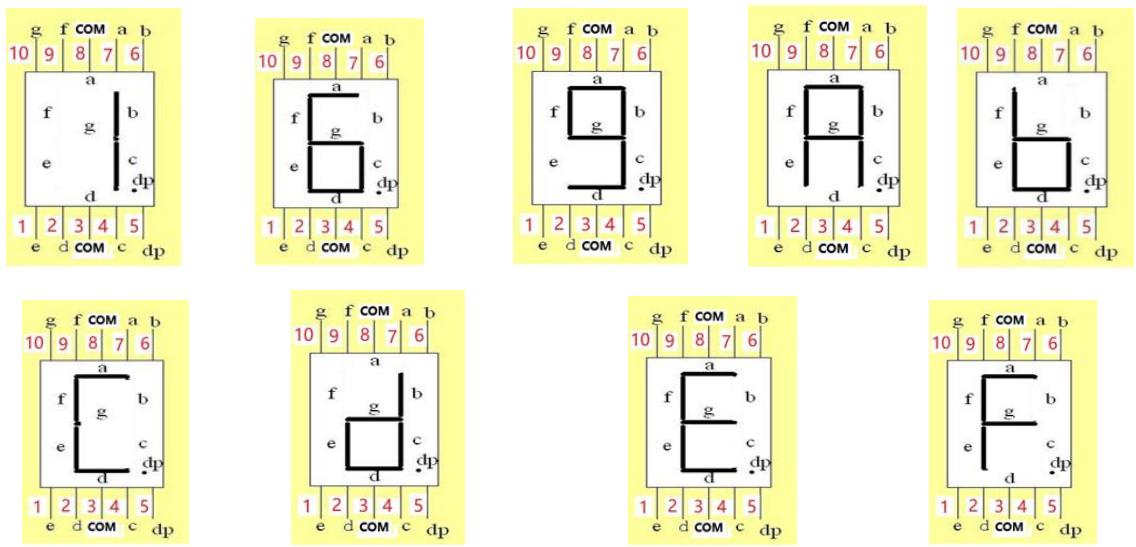

设计一个七段显示译码器,要求与共阴数码管配套,显示一位十六进制数的类似手写形状,其中的几个字型要求如下:1、6、9、A、B、C、D、E、F 必须显示为如图 1 所示的形状:

图1 显示的形状

(1)要求用门电路实现。

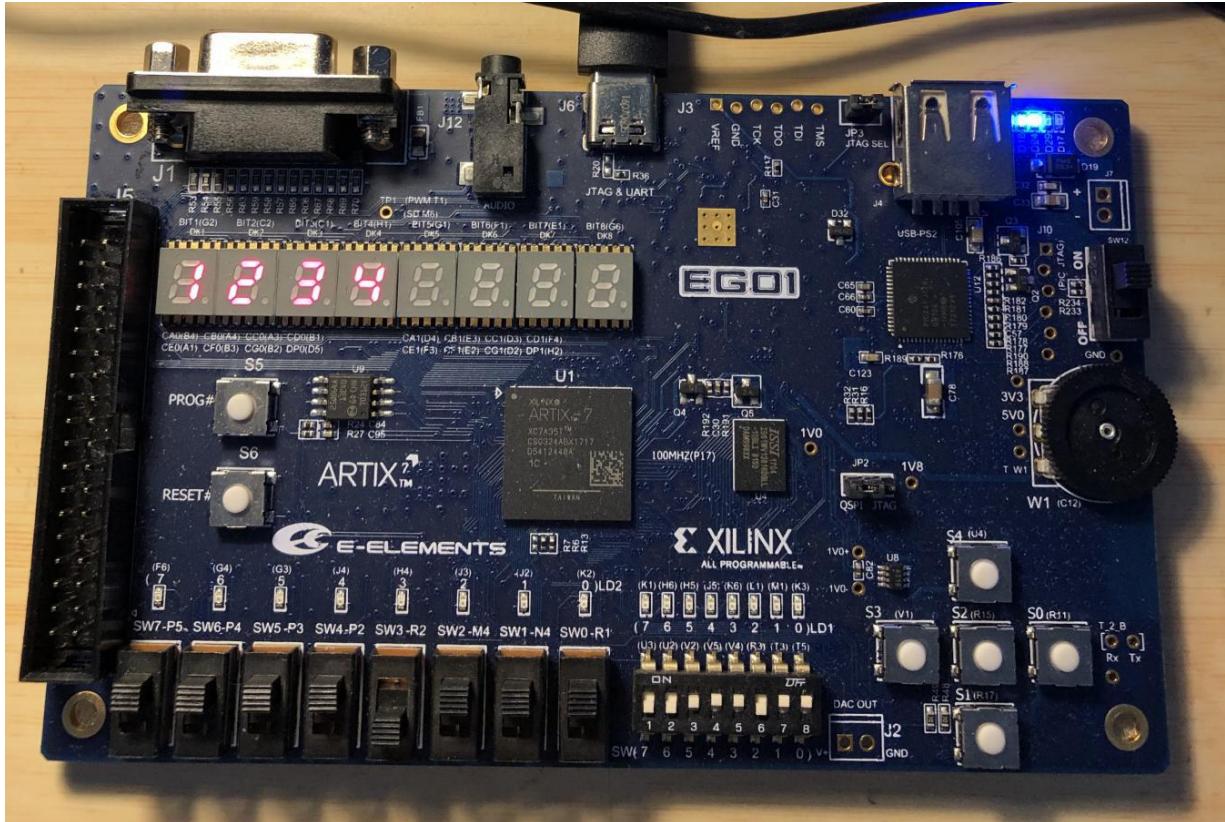

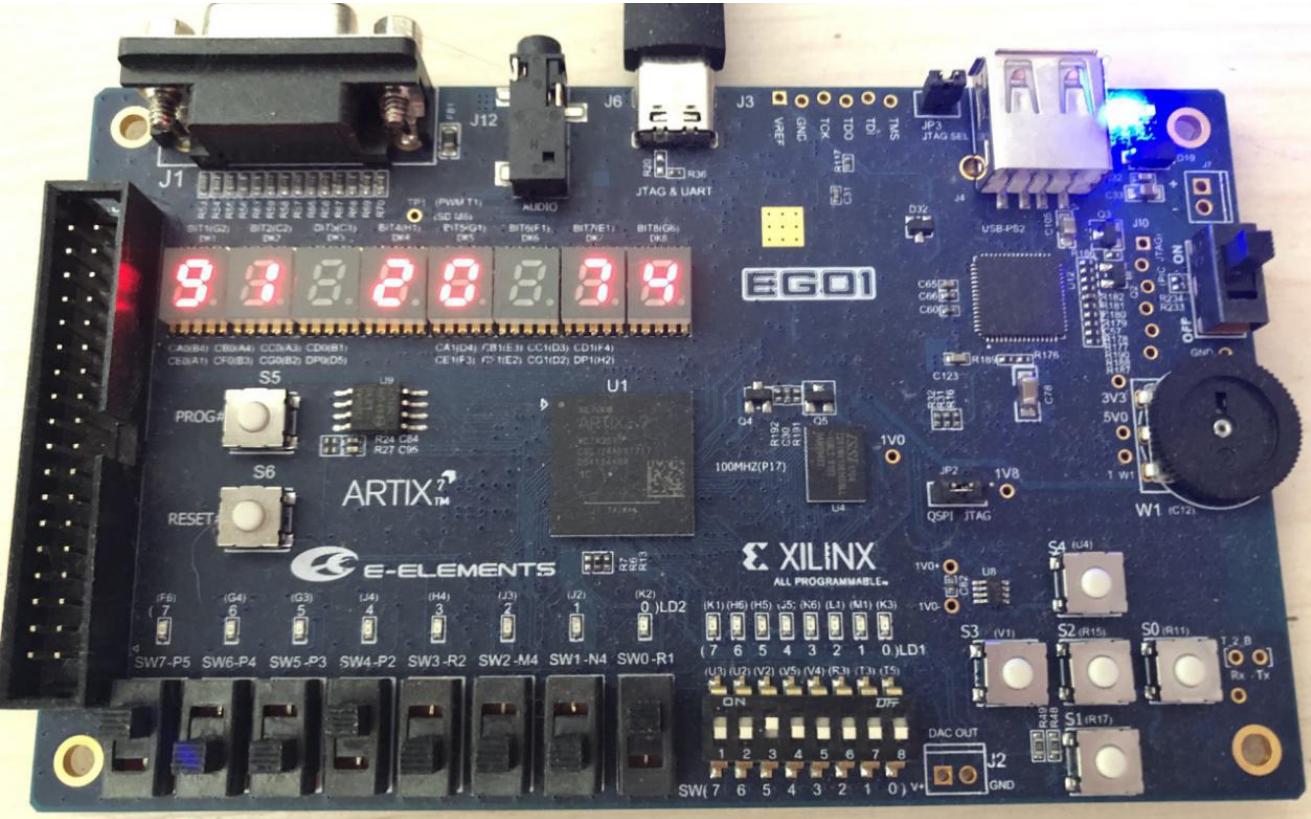

(2)编写 Verilog-HDL 程序,使用 EGO1 口袋实验板上 FPGA 芯片 XC7A35TCSG324-1 实现。在最右侧的数码管上显示。

2.5 设计2 位数码管静态、动态显示电路

(1)设计 2 位共阴数码管静态显示电路,显示两个域元素 9、0。Multisim12 软件仿真。

(2)设计 2 位共阴数码管动态显示电路,显示两个域元素 9、0。Multisim12 软件仿真。

(3)设计 2 位共阳数码管静态显示电路,显示两个域元素 9、0。Multisim12 软件仿真。

(4)设计 2 位共阳数码管动态显示电路,显示两个域元素 9、0。Multisim12 软件仿真。

(5)在 EGO1 口袋实验板上设计 2 位共阴数码管动态显示电路,显示两个域元素 9、0。要求使用EGO1 口袋实验板的最左侧的 2 个数码管。

2.6 设计4 位数码管静态、动态显示电路

(1)设计 4 位共阴数码管静态显示电路,显示四个域元素 1、2、3、4。Multisim12 软件仿真。(2)设计 4 位共阴数码管动态显示电路,显示四个域元素 1、2、3、4。Multisim12 软件仿真。(3)在 EGO1 口袋实验板上设计 4 位共阴数码管动态显示电路,显示四个域元素 1、2、3、4。要求使用 EGO1 口袋实验板的最左侧的 4 个数码管。

2.7 设计8 位数码管动态显示电路

(1)设计 8位共阴数码管动态显示电路,显示八个域元素 1、2、3、4、5、6、7、8。Multisim12软件仿真。

(2) 在 EGO1 口袋实验板上设计 8 位共阴数码管动态显示电路,显示八个域元素 1、2、3、4、5、6、7、8。

2.8 在 EGO1 口袋实验板 8 位共阴数码管上显示任务 2.1 的有限域乘法运算结果

2.9 在 EGO1 口袋实验板 8 位共阴数码管上显示任务 2.2 的有限域运算乘法结果

2.10 在 EGO1 口袋实验板 8 位共阴数码管上显示任务 2.3的RS 编码

3. 相关知识及背景

纠错编码是信道编码的一种,基本原理是发送端在待传输的信息符号后按照一定的规则增加校验符号,构成一个码字再送到信道传输。RS 码是应用极其广泛的信道纠错编码,其中乘法运算单元是核心模块。用数码管来直观显示有限域乘法运算结果、编码过程及校验符号可增加趣味性,并可综合训练学生对组合逻辑模块、HDL 等知识点的掌握以及EDA软件的使用。

4. 教学目标与目的

训练学生对二进制译码器、数据选择器、非二进制译码器(显示译码器)、二进制计数器等常用逻辑模块的理解和综合应用;训练Verilog-HDL、VHDL 的混合编程能力;引领学生从知识点编码器出发,探究Reed-Solomon编码器的工程实际应用。

5. 教学设计与引导

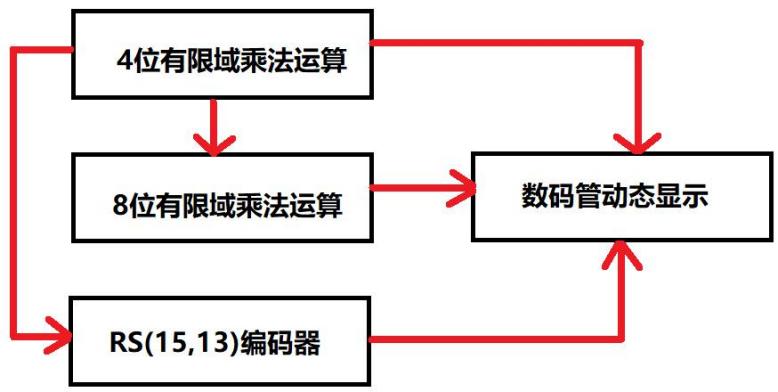

实验任务整体框图如图 2 所示。设计 4 位有限域元素的乘法运算电路,推广至8 位有限域元素的乘法运算电路,然后设计 4 位有限域上 Reed-Solomon 编码器,用 VHDL语言描述乘法器和编码器。用 Verilog-HDL 描述数码管动态显示电路,使用EGO1 口袋实验板的8 个数码管显示域元素及乘法运算结果,显示信息符号及校验符号。

图 2 实验任务整体框图

在数制、码制、逻辑代数、普通代数的基础上引出“有限域”的概念学生是可以接受的,在此基础上定义有限域的加法、乘法、除法运算,并给出逻辑门电路的实现,在讲解普通编码器、优先编码器的基础上,拓展编码器的工程实际应用,给出定义在有限域上的 Reed-Solomon 纠错编码器,并用同步时序逻辑电路来实现。通过本实验案例Reed-Solomon 纠错编码器部分的设计,可拓展学生的视野,引导学生认识专业基础课与工程实际应用的紧密联系。

通过本实验案例数码管动态显示部分的设计,学生从理论到实践的全方位的、深入的、循序渐进的体验式探究学习,可综合训练二进制译码器、数据选择器、非二进制译码器(显示译码器)等常用组合逻辑模块概念、计数器这一最典型时序逻辑模块的理解与应用。

此实验案例可以训练 VHDL、Verilog-HDL 语言混合编程能力,顶层设计使用Verilog-HDL 语言,底层分别使用 VHDL 描述编码器、Verilog-HDL 描述数码管显示电路。可训练VIVADO 软件测试平台、仿真功能的使用。

本实验案例涉及到 PN结、二极管、二极管的正偏、二极管的反偏、发光二极管的正偏、发光二极管的反偏、共阴数码管、共阳数码管等模拟电路相关知识点。

(1)乘法运算及RS(15,13)编码器

为了便于学生接受有限域的概念,首先给出了一个规模比较小的 4位二进制码的有限域,然后再拓展到8位二进制码的有限域。为了便于理解工作原理,给出了一个4 位二进制码的有限域上的RS(15,13)编码器,在其基础上,对于学有余力的学生可尝试设计 RS(255,223)编码器。循序渐进讲解编码器工作原理的示意图如图3(a)所示。

(2)数码管动态显示

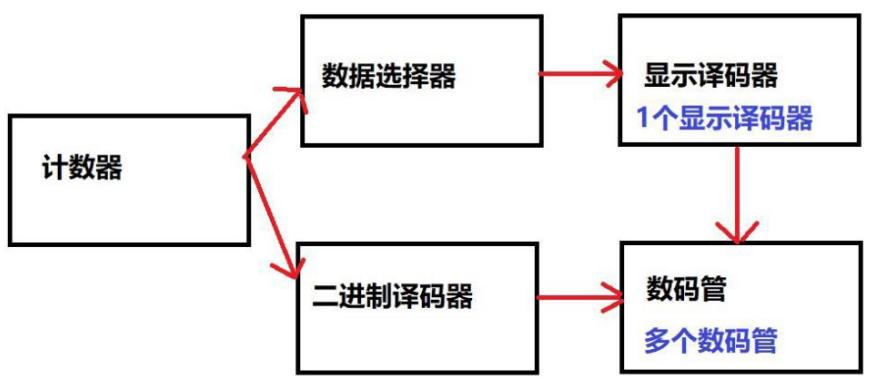

循序渐进讲解数码管动态显示电路工作原理的示意图如图3(b)所示。

图 3 循序渐进式学习步骤

$\textcircled{1} 1$ 位数码管的显示

首先用门电路设计数码管显示译码器,约定、真值表、卡诺图法化简、画出逻辑电路图可帮助学生进一步熟悉组合逻辑电路的一般设计方法。这一设计过程还可帮助学生深刻理解显示译码器的概念,熟悉 4 个输入信号、7 个输出信号以及它们之间的逻辑关系,帮助学生理解为什么某种显示译码器芯片必须与共阴数码管配套使用,而某个显示译码器芯片又必须与共阳数码管配套使用。学生亲自参与的设计与仅仅读厂家的数码管显示译码器芯片数据手册收获更大。了解数码管可涉及PN结、PN结的正偏、PN结的反偏、发光二极管、数码管的共阴接法、数码管的共阳接法等多个模电知识点,可提高学生的综合应用能力。

然后用 Verilog-HDL 描述数码管显示译码器,使用 EDA 软件在 EGO1 口袋实验板最右侧数码管位置显示一个域元素符号,可帮助学生深刻理解EGO1 口袋实验板的硬件环境,这是实验能否顺利进行的基础。EGO1 口袋实验板有8个数码管,四个为一组,两组完全独立,每组的 a、b、c、d、e、f段分别别连接在一起,数码管的公共端由FPGA的引脚再通过BJT三极管控制,了解EGO1 板的硬件环境可涉及数码管的共阴接法、数码管的共阳接法、BJT 三极管的饱和状态、BJT 三极管的截止状态等多个模电知识点,可训练学生的读图能力。

$\textcircled{2}$ 静态显示与动态显示的概念

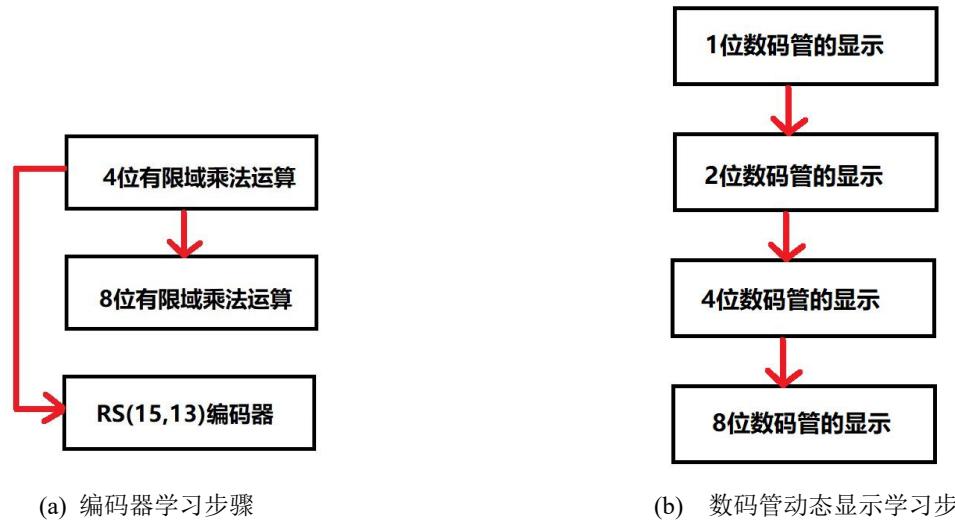

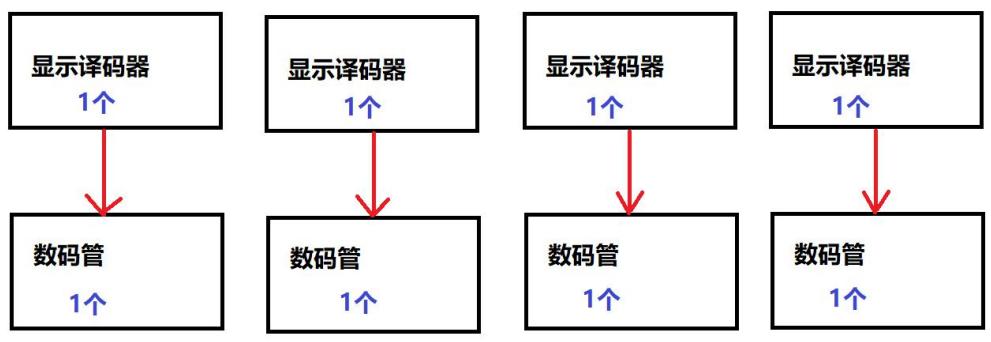

为了节省端口,很多电子系统采用动态显示的概念,为了更好得理解动态显示的概念,先引出静态显示的概念作为对比。图 4 为静态显示原理框图,图5为动态显示原理框图。

图 4 静态显示原理框图

图 5 动态显示原理框图

使用 Multisim12 软件搭接 2 位、4 位数码管的静态显示电路,为解释动态显示的概念奠定基础。分别使用共阳、共阴两种数码管完成静态显示电路设计,比较二者的区别,帮助学生深刻理解共阴数码管的使用,为理解EGO1 口袋实验板的共阴数码管奠定基础。

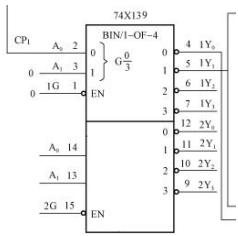

$\textcircled{3}$ 2位数码管的动态显示

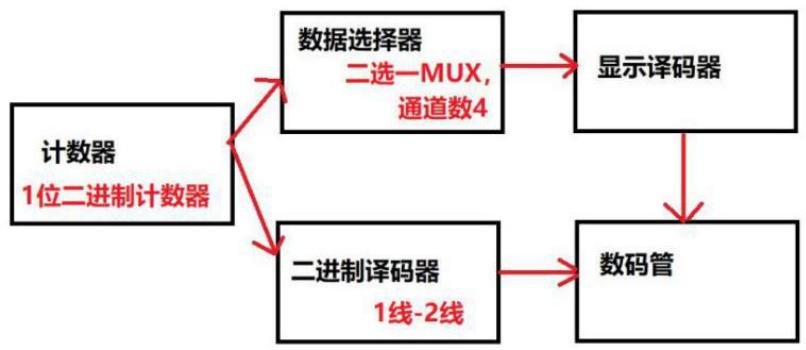

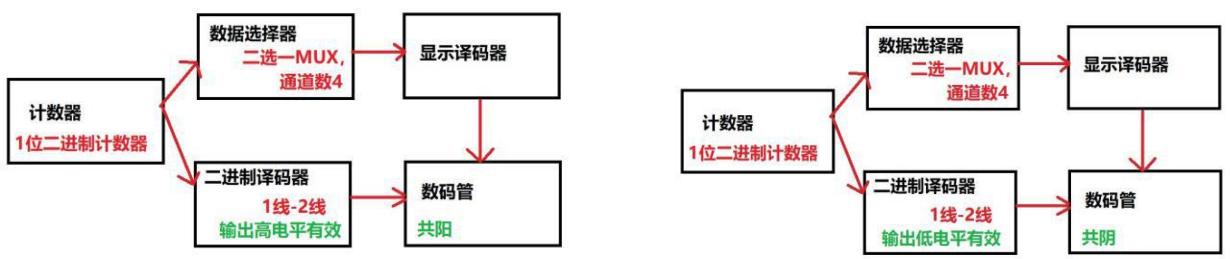

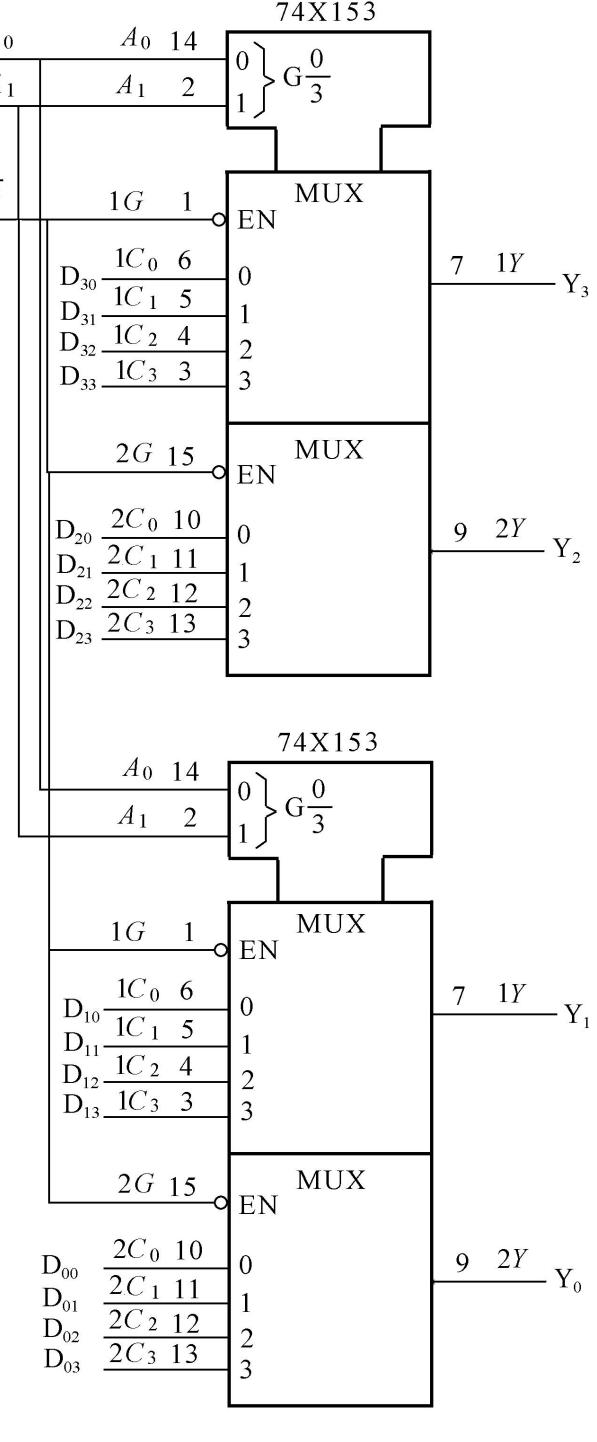

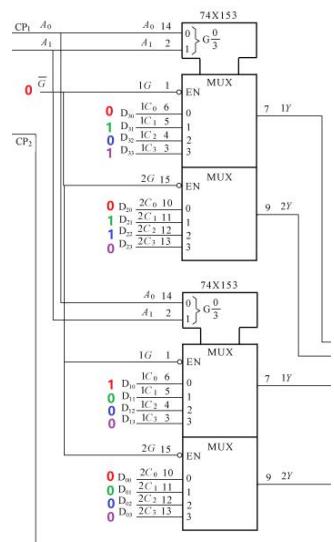

使用Multisim12软件搭接 2位数码管的动态显示电路,使用中规模组合逻辑模块实现。加深学生对 1 线-2 线二进制译码器、二选一数据选择器(通道数为 4)、显示译码器、1位二进制计数器等基本概念的理解。其中还涉及二选一数据选择器的通道数的扩展。如图6所示。

图 6 2 位数码管动态显示原理框图

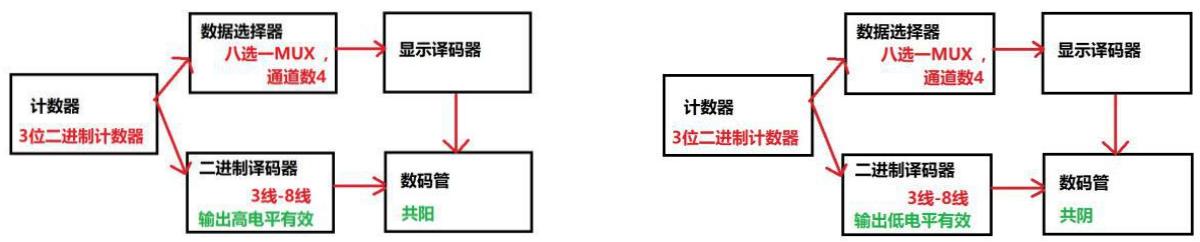

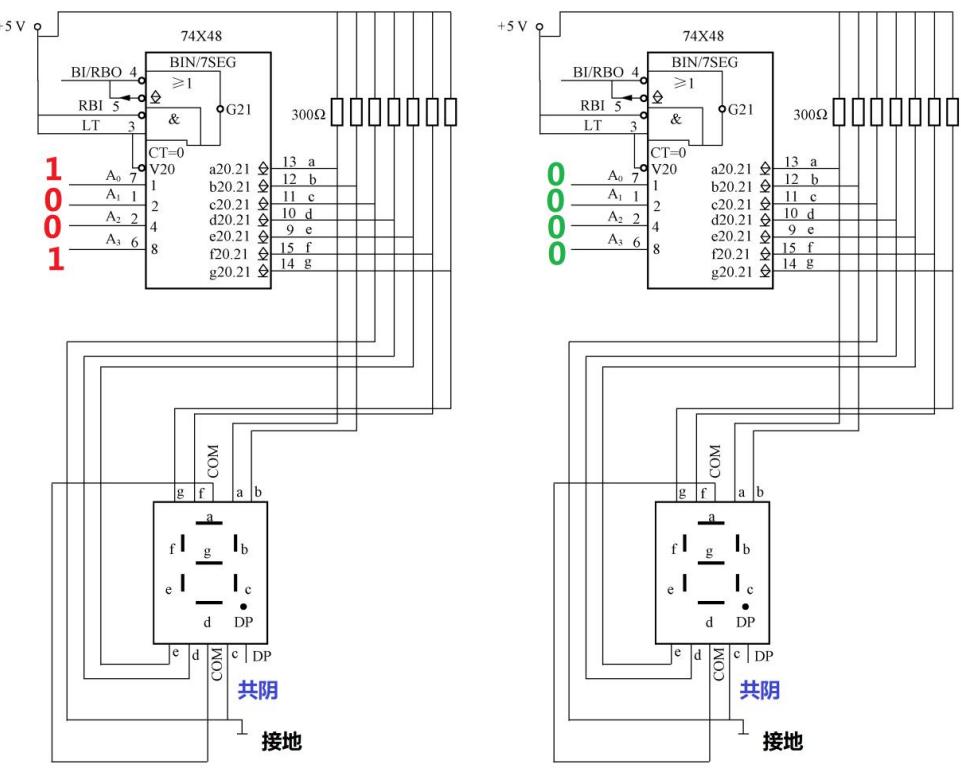

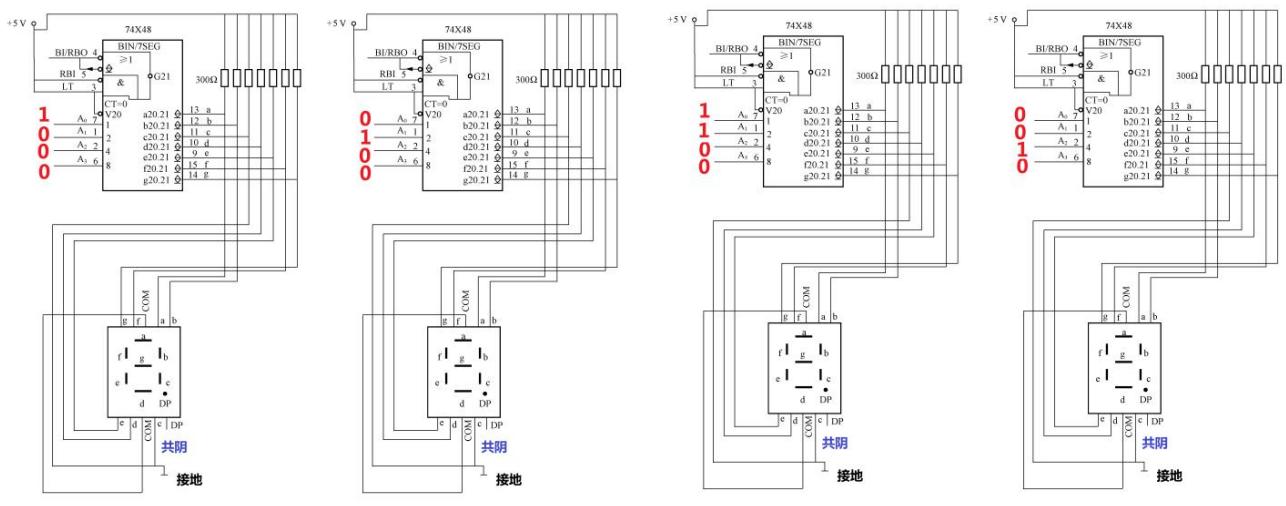

对共阳、共阴两种数码管的设计做对比,帮助学生深刻理解共阴数码管的使用,为理解EGO1 口袋实验板的共阴数码管奠定基础。如图7所示。

图 7 共阴与共阳对比

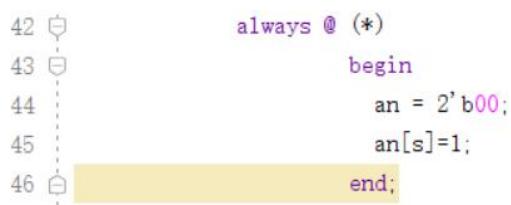

④ 2 位数码管的动态显示的 Verilog-HDL 描述

在充分讲解MSI模块实现的2位共阴数码管动态显示电路的基础上,用Verilog-HDL语言描述电路,然后将 Verilog-HDL 语言描述与电路图一一对应,可加快学生对Verilog-HDL 语言的理解。学生可快速掌握 1 线-2 线二进制译码器、二选一数据选择器、显示译码器、1 位二进制计数器等模块的 Verilog-HDL 描述,在使用 Verilog-HDL 语言的过程中去学习语言的基本语法和结构。

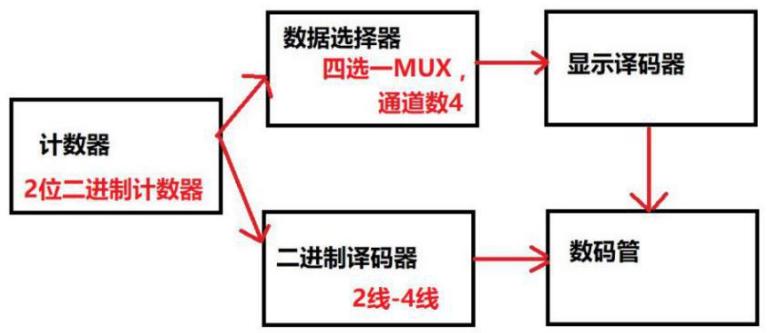

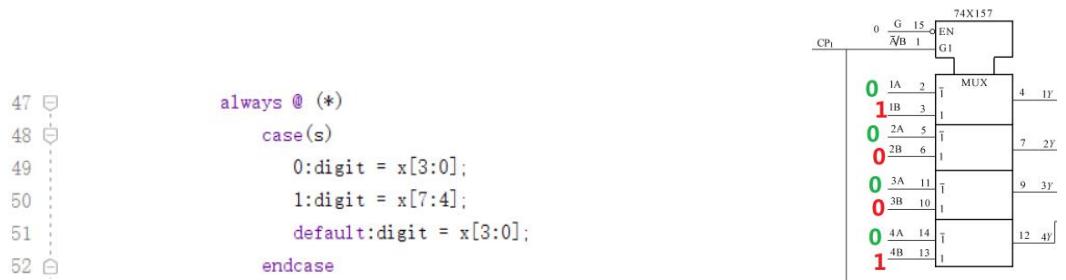

$\textcircled{5}$ 4位数码管的动态显示

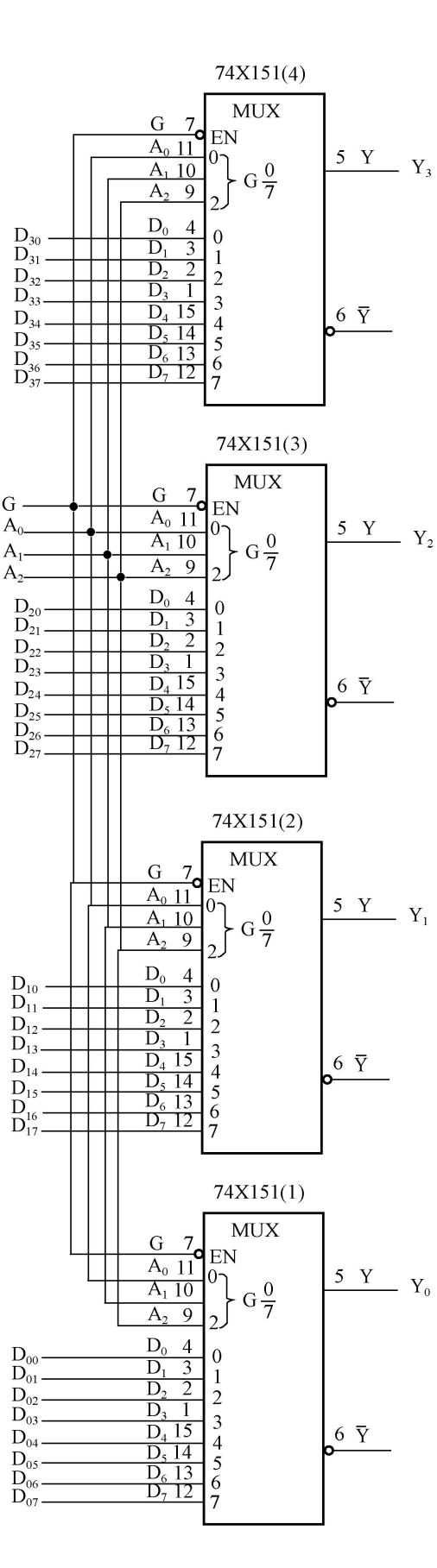

在2位数码管动态显示电路的基础上,使用Multisim12 软件搭接4 位数码管的动态显示电路,使用中规模组合逻辑模块实现。加深学生对2 线-4 线二进制译码器、四选一数据选择器(通道数为 4)、显示译码器、2 位二进制计数器等基本概念的理解。可涉及数据选择器的扩展、二进制译码器的扩展、二进制计数器的扩展,其中还涉及四选一数据选择器的通道数的扩展。原理框图如图8所示。

图 8 4位数码管动态显示原理框图

对共阳、共阴两种数码管的设计做对比,帮助学生深刻理解共阴数码管的使用,为理解EGO1 口袋实验板的共阴数码管奠定基础。如图9所示。

图 9 共阴与共阳对比

$\textcircled{6}$ 4 位数码管的动态显示的 Verilog-HDL 描述

在2位数码管的动态显示的 Verilog-HDL 描述的基础上,只需改变某些信号数组的下标即可。将 Verilog-HDL 语言描述与中规模组合逻辑模块实现的电路图一一对应,可加快学生对 Verilog-HDL 语言的理解。学生可深刻体会使用HDL 语言描述电路的优势。

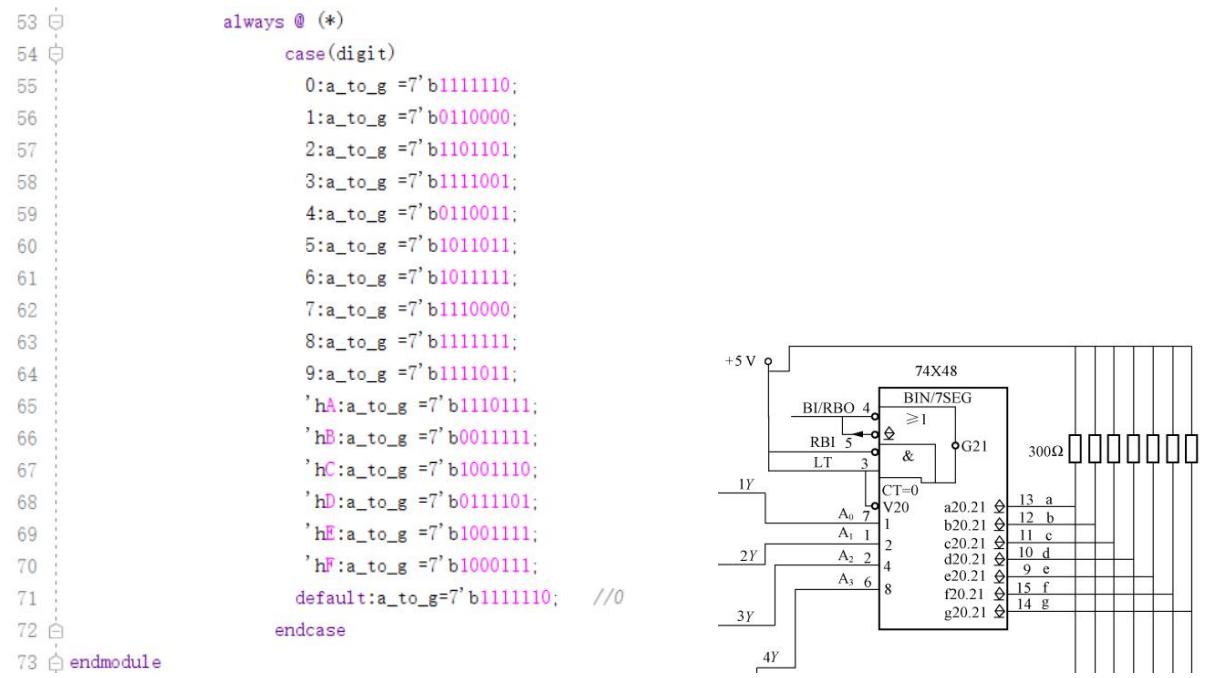

$\textcircled{7}$ 8 位数码管的动态显示的 Verilog-HDL 描述

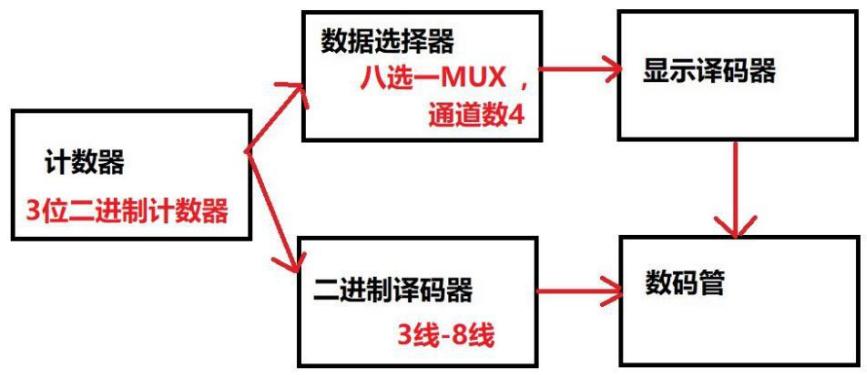

在 4 位数码管的动态显示的 Verilog-HDL 描述的基础上,只需改变某些信号数组的下标即可。可加深学生对 3 线-8 线二进制译码器、八选一数据选择器(通道数为 4)、显示译码器、3位二进制计数器等基本概念的理解。原理框图如图10所示。

图 10 8位数码管动态显示原理框图

对共阳、共阴两种数码管的设计做对比,帮助学生深刻理解共阴数码管的使用,为理解EGO1 口袋实验板的共阴数码管奠定基础。如图11所示。

图 11 共阴与共阳对比

6. 实验原理及方案

6.1 设计由本原多项式 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ 定义的有限域 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 内乘法运算电路

若元素数目为一素数的幂,则由此有限个元素与相应定义的加法运算、乘法运算组成的域称为有限域,记为 $\mathrm { G F } ( \mathfrak { p } ^ { \mathrm { m } } )$ 。

考虑 $\scriptstyle { \mathtt { p } } = 2$ 的情况,对于 $\mathrm { m } { = } 4$ ,本原多项式为 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ 的 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 域的各种表示形式的元素列表如表 1 所示。

表 1 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 域的各种表示形式的元素列表

| power | evaluation | decimal value | binary value |

| a | X | 2 | 0010 |

| α² | x² | 4 | 0100 |

| 8 | x | 8 | 1000 |

| α4 | x²+1 | 9 | 1001 |

| α | x² +x+1 | 11 | 1011 |

| 86 | x²+x²+x+1 | 15 | 111 |

| 87 | x² +x+1 | 7 | 0111 |

| a8 | x²+x²+x | 14 | 1110 |

| 89 | x²+1 | 5 | 0101 |

| α10 | x²+x | 10 | 1010 |

| α1 | x²+x²+1 | 13 | 1101 |

| α12 | x+1 | 3 | 0011 |

| α13 | x²+x | 6 | 0110 |

| α14 | x²+x² | 12 | 1100 |

| q15 | 1 | 1 | 0001 |

给定 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 域本原多项式 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ ,域中的任意两个元素 $M _ { 1 }$ 和 $N _ { 1 }$ 。

$M _ { 1 }$ 和 $N _ { 1 }$ 的二进制表示形式分别为:

$$ \begin{array} { c } { { M _ { 1 } = m _ { 3 } m _ { 2 } m _ { 1 } m _ { 0 } } } \ { { { } } } \ { { N _ { 1 } = n _ { 3 } n _ { 2 } n _ { 1 } n _ { 0 } } } \end{array} $$

$M _ { 1 }$ 对应的多项式为: $M = m _ { 3 } x ^ { 3 } + m _ { 2 } x ^ { 2 } + m _ { 1 } x + m _ { 0 }$

$N _ { 1 }$ 对应的多项式为: $N = n _ { 3 } x ^ { 3 } + n _ { 2 } x ^ { 2 } + n _ { 1 } x + n _ { 0 }$

实现 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 域上乘法运算 $P = M \times N$ 的具体算法如下:

第一步:将 $M$ 和 $N$ 两个多项式按常规方法相乘,得到一个次数不大于 6 的多项式 $P _ { 1 }$ 。

$$ \begin{array} { l } { P _ { 1 } = M \times N = ( m _ { 3 } x ^ { 3 } + m _ { 2 } x ^ { 2 } + m _ { 1 } x + m _ { 0 } ) \times ( n _ { 3 } x ^ { 3 } + n _ { 2 } x ^ { 2 } + n _ { 1 } x + n _ { 0 } ) } \ { = ( m _ { 3 } n _ { 3 } ) x ^ { 6 } + [ ( m _ { 3 } n _ { 2 } ) \oplus ( m _ { 2 } n _ { 3 } ) ] x ^ { 5 } + [ ( m _ { 3 } n _ { 1 } ) \oplus ( m _ { 2 } n _ { 2 } ) \oplus ( m _ { 1 } n _ { 3 } ) ] x ^ { 4 } } \ { + [ ( m _ { 3 } n _ { 0 } ) \oplus ( m _ { 2 } n _ { 1 } ) \oplus ( m _ { 1 } n _ { 2 } ) \oplus ( m _ { 0 } n _ { 3 } ) ] x ^ { 3 } } \ { + [ ( m _ { 2 } n _ { 0 } ) \oplus ( m _ { 1 } n _ { 1 } ) \oplus ( m _ { 0 } n _ { 2 } ) ] x ^ { 2 } + [ ( m _ { 1 } n _ { 0 } ) \oplus ( m _ { 0 } n _ { 1 } ) ] x ^ { 1 } + ( m _ { 0 } n _ { 0 } ) x ^ { 0 } } \end{array} $$

第二步:将 $x ^ { 6 }$ 对本原多项式 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ 求模, 得 $x ^ { 3 } + x ^ { 2 } + x + 1$ 并填放进表 2 多项式乘法运算分解表中的“幂” $x ^ { 6 }$ 对应的行、“等效幂”列的交点对应的方格,如表 2 所示。

第三步:同理,依次对 $x ^ { 5 }$ 、 $x ^ { 4 }$ 进行如上运算,并将求模所得多项式分别填放在表 2中相应的位置。

第四步:因为在行 $x ^ { 4 }$ 对应的“等效幂”列中,多项式为 $x ^ { 3 } + 1$ ,所以将 $m _ { 3 } n _ { 1 } . ~ m _ { 2 } n _ { 2 } . ~ m _ { 1 } n _ { 3 }$ 这 3 项分别放入行 $x ^ { 3 }$ 、行 $x ^ { 0 }$ 对应的“附加的项”列中,如表 2 所示。

第五步:同理,依次对行 $x ^ { 5 }$ 、行 $x ^ { 6 }$ 进行如上操作。

第六步:依据表 2,得到乘积多项式 $P$ , $P = p _ { 3 } x ^ { 3 } + p _ { 2 } x ^ { 2 } + p _ { 1 } x ^ { 1 } + p _ { 0 } x ^ { 0 }$ 其中,

$$ p _ { 0 } = ( m _ { 0 } n _ { 0 } ) \oplus ( m _ { 1 } n _ { 3 } ) \oplus ( m _ { 2 } n _ { 2 } ) \oplus ( m _ { 3 } n _ { 1 } ) \oplus ( m _ { 2 } n _ { 3 } ) \oplus ( m _ { 3 } n _ { 2 } ) \oplus ( m _ { 3 } n _ { 3 } ) $$

其它系数 $p _ { 1 } \cdot p _ { 2 } \cdot$ $p _ { 3 }$ 的表达式可以同样方法得到。

$$ p _ { 1 } = \left( m _ { 0 } n _ { 1 } \right) \oplus \left( m _ { 1 } n _ { 0 } \right) \oplus \left( m _ { 2 } n _ { 3 } \right) \oplus \left( m _ { 3 } n _ { 2 } \right) \oplus \left( m _ { 3 } n _ { 3 } \right) $$

$$ p _ { 2 } = ( m _ { 0 } n _ { 2 } ) \oplus ( m _ { 1 } n _ { 1 } ) \oplus ( m _ { 2 } n _ { 0 } ) \oplus ( m _ { 3 } n _ { 3 } ) $$

$$ p _ { 3 } = ( m _ { 0 } n _ { 3 } ) \oplus ( m _ { 1 } n _ { 2 } ) \oplus ( m _ { 2 } n _ { 1 } ) \oplus ( m _ { 3 } n _ { 0 } ) $$

$$ \begin{array} { r } { \bigoplus ( m _ { 1 } n _ { 3 } ) \bigoplus ( m _ { 2 } n _ { 2 } ) \bigoplus ( m _ { 3 } n _ { 1 } ) \bigoplus ( m _ { 2 } n _ { 3 } ) \bigoplus ( m _ { 3 } n _ { 2 } ) \bigoplus ( m _ { 3 } n _ { 3 } ) } \end{array} $$

表 2 多项式乘法运算分解表

| 幂 | 有贡献的乘积项 | 等效幂 | 附加的项 |

| x | mono | mn、m2n2、 mn;m2n、mn2;mn3 | |

| x | mon、mno | m2n、m3n2;mn3 | |

| x² | mn2、mn、m2no | m3n3 | |

| x | mon3、mn2、m2n、 mno | mn、 m2n2、mn;m2n、mn2;mn3 | |

| x4 | m,n3、 m2n2、 m3n | x+1 | |

| x | m2n3、m3n2 | x+x+1 | |

| x6 | mn3 | x+x²+x+1 |

根据上述分析,用 VHDL 描述有限域乘法运算:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL; entity mult4bit is

Port ( a : in STD_LOGIC_VECTOR (3 downto 0); b : in STD_LOGIC_VECTOR (3 downto 0); c : out STD_LOGIC_VECTOR (3 downto 0));

end mult4bit;

architecture Behavioral of mult4bit is signal ly : STD_LOGIC_VECTOR (6 downto 0); signal lym $:$ STD_LOGIC_VECTOR (3 downto 0);

begin

$\mathrm { l y } ( 6 ) \mathrm { < } = \mathsf { a } ( 3 )$ and b(3) ; $\mathrm { l y } ( 5 ) { < } = ( \mathrm { a } ( 3 )$ and b(2)) xor (a(2) and b(3)) ; $\mathrm { l y } ( 4 ) \mathrm { < } =$ (a(1) and b(3)) xor (a(2) and b(2))xor (a(3) and b(1)); $\mathrm { l y } ( 3 ) < =$ (a(3) and ${ \mathsf b } ( 0 ) _ { + }$ ) xor (a(2) and b(1))xor (a(1) and b(2)) xor (a(0) and b(3)); $\mathrm { l y } ( 2 ) { < } = ( \mathrm { a } ( 2 )$ and ${ \mathsf b } ( 0 ) _ { + }$ ) xor $\mathtt { a } ( 1 )$ and b(1))xor (a(0) and b(2)); $\mathrm { l y } ( 1 ) { \ < } =$ (a(1) and b(0)) xor (a(0) and b(1)); ly(0)<= (a(0) and b(0)) ; $\mathrm { l y m } ( 3 ) { \ < } = \mathrm { l y } ( 3 )$ xor ly(4) xor ly(5) xor ly(6); $\mathrm { l y m } ( 2 ) { < } = \mathrm { l y } ( 2 )$ xor ly(6) ; $\mathrm { l y m } ( 1 ) { < } = \mathrm { l y } ( 1 )$ xor ly(5) xor ly(6); $\mathrm { l y m } ( 0 ) { < } = \mathrm { l y } ( 0 )$ xor ly(4) xor ly(5) xor ly(6) ; $\mathsf { c } { \mathsf { < } } { \mathsf { = } } \mathsf { l y m }$ ; end Behavioral;

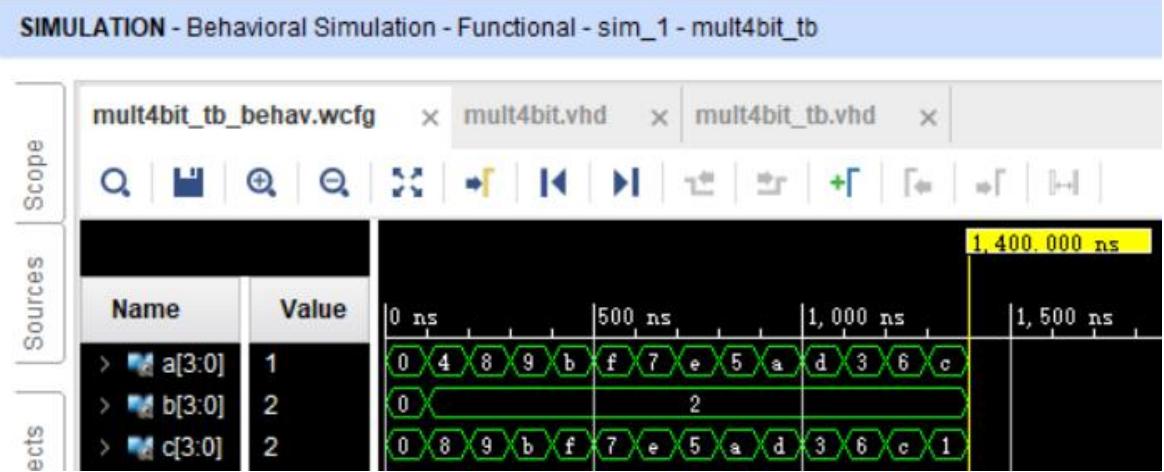

在 VIVADO 软件环境下仿真验证。仿真波形如图 12 所示。给定被乘数 $0 0 1 0 ~ ( 2 \mathrm { { _ { H } } ) }$ 、 乘数 0010( $( 2 \mathrm { _ H } )$ ),得乘积为 0100( $4 _ { \mathrm { H } } )$ )。给定被乘数 1000( $8 _ { \mathrm { H } } .$ )、 乘数 0010( $2 _ { \mathrm { H } } )$ ),得乘积为 1001( $. 9 \mathrm { { H } }$ )。给定被乘数 1100(cH)、 乘数 0010( $\angle 2 \mathrm { _ H } ,$ ),得乘积为 0001( $1 _ { \mathrm { H } } )$ ),与理论计算结果一致。

图 12 仿真波形

6.2 设计由本原多项式 $f ( x ) = x ^ { 8 } + x ^ { 7 } + x ^ { 2 } + x + 1$ 定义的有限域 $\mathrm { G F } ( 2 ^ { 8 } )$ 内乘 法运 算电路

若元素数目为一素数的幂,则由此有限个元素与相应定义的加法运算、乘法运算组成的域称为有限域,记为 $\mathrm { G F } ( \mathfrak { p } ^ { \mathrm { m } } )$ 。

考虑 $\mathtt { p } { = } 2$ 的情况,对于 $\mathrm { m } { = } 8$ ,本原多项式为 $f ( x ) = x ^ { 8 } + x ^ { 7 } + x ^ { 2 } + x + 1$ 的 ${ \mathrm { G F } } ( 2 ^ { 8 } )$ 域 的 各 种 表示形式的元素列表如表 3 所示。

表 3 $\mathrm { G F } ( 2 ^ { 8 } )$ 域的各种表示形式的元素列表

| power | evaluation | decimal value | binary value |

| a1 | x | 2 | 00000010 |

| a² | x | 4 | 00000100 |

| 8 | x | 8 | 00001000 |

| a4 | x4 | 16 | 00010000 |

| α | x | 32 | 0010000 |

| α6 | 小 | 64 | 01000000 |

| α7 | x7 | 128 | 10000000 |

| 8 | x7+x²+x+1 | 135 | 10000111 |

| 89 | x+x²+1 | 137 | 10001001 |

| 810 | x7+x4+x²+1 | 139 | 10010101 |

| αl | x+x+x³+x²+1 | 173 | 10101101 |

| α12 | x7+x+x4+x³+x²+1 | 221 | 11011101 |

| α13 | x²+x4+x²+x²+1 | 61 | 00111101 |

| α14 | x+x²+x4+x²+x¹ | 122 | 01111010 |

| : | : | : | … |

| α255 | 1 | 1 | 00000001 |

给定 $\mathrm { G F } ( 2 ^ { 8 } )$ 域本原多项式 $f ( x ) = x ^ { 8 } + x ^ { 7 } + x ^ { 2 } + x + 1$ ,域中的任意两个元素 $M _ { 1 }$ 和 $N _ { 1 }$ 。$M _ { 1 }$ 和 $N _ { 1 }$ 的二进制表示形式分别为:

$$ \begin{array} { c } { M _ { 1 } = m _ { 7 } m _ { 6 } m _ { 5 } m _ { 4 } m _ { 3 } m _ { 2 } m _ { 1 } m _ { 0 } } \ { { { } } } \ { N _ { 1 } = n _ { 7 } n _ { 6 } n _ { 5 } n _ { 4 } n _ { 3 } n _ { 2 } n _ { 1 } n _ { 0 } } \end{array} $$

$M _ { 1 }$ 对应的多项式为: $M = m _ { 7 } x ^ { 7 } + m _ { 6 } x ^ { 6 } + m _ { 5 } x ^ { 5 } + m _ { 4 } x ^ { 4 } + m _ { 3 } x ^ { 3 } + m _ { 2 } x ^ { 2 } + m _ { 1 } x + m _ { 0 }$

$N _ { 1 }$ 对应的多项式为: $N = n _ { 7 } x ^ { 7 } + n _ { 6 } x ^ { 6 } + n _ { 5 } x ^ { 5 } + n _ { 4 } x ^ { 4 } + n _ { 3 } x ^ { 3 } + n _ { 2 } x ^ { 2 } + n _ { 1 } x + n _ { 0 }$

实现 $\mathrm { G F } ( 2 ^ { 8 } )$ 域上乘法运算 $P = M \times N$ 的具体算法如下:

第

$$ \begin{array} { r l } & { - | \mathcal { S } | | \mathcal { S } | | \displaystyle { \mathrm { ~ \hat { \psi } ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ \psi ~ } } } \ & \mathcal { T } | \mathcal { S } | | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } | \mathcal { H } \mathcal { H } | \mathcal { H } | \mathcal { H } \mathcal { H } | \mathcal { H } \mathcal { H } | \mathcal { H } \mathcal { H } | \mathcal \mathcal { H } | \mathcal { H } \mathcal { H } | \mathcal \mathcal { H } \mathcal { H } | \mathcal \mathcal { H } \mathcal { H } | \mathcal \mathcal { H } \mathcal { H } \mathcal | \mathcal { H } \mathcal \mathcal { H } | \mathcal \mathcal { H } \mathcal { H } \mathcal | \mathcal \mathcal { H } \mathcal { H } \mathcal | \mathcal \mathcal { H } \mathcal { H } \mathcal \mathcal { H } \mathcal | \mathcal \mathcal { H } \mathcal { H } \mathcal \mathcal { H } \mathcal | \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal \mathcal { H } \mathcal { H } \mathcal \mathcal { H } \mathcal { H } \mathcal { H } \mathcal { H } \mathcal { H } \mathcal { H } \mathcal { H } \mathcal { H } \mathcal { H } \mathcal { H } \end{array} $$

第二步:将 $x ^ { 1 4 }$ 对本原多项式 $f ( x ) = x ^ { 8 } + x ^ { 7 } + x ^ { 2 } + x + 1$ 求模, 得 $x ^ { 6 } + x ^ { 7 } + x ^ { 4 } + x ^ { 3 } + x$ 并填放进表 4 多项式乘法运算分解表中的“幂” $x ^ { 1 4 }$ 对应的行、“等效幂”列的交点对应的方格,如表 4所示。

第三步:同理,依次对 $x ^ { 1 3 }$ 、 $x ^ { 1 2 }$ 、 $x ^ { 1 1 }$ 、 $x ^ { 1 0 }$ 、 $x ^ { 9 }$ 、 $x ^ { 8 }$ 进 行 如 上运 算 , 并 将 求 模所 得 多 项 式 分别填放在表 4 中相应的位置。

第 四 步 : 因 为 在 行 $x ^ { 8 }$ 对 应 的 “ 等 效 幂 ”列 中 , 多 项 式 为 $x ^ { 7 } + x ^ { 2 } + x ^ { 1 } + 1$ , 所 以 将$m _ { 7 } n _ { 1 ^ { \circ } } m _ { 6 } n _ { 2 ^ { \circ } } m _ { 5 } n _ { 3 ^ { \circ } } m _ { 4 } n _ { 4 ^ { \circ } } m _ { 3 } n _ { 5 ^ { \circ } } m _ { 2 } n _ { 6 ^ { \circ } } m _ { 1 } n _ { 7 } \tilde { E }$ 这 7 项分别放入行 $x ^ { 7 }$ 、行 $x ^ { 2 }$ 、行 $x ^ { 1 }$ 、行 $x ^ { 0 }$ 对应的“附加的项”列中,如表 4 所示。

第五步:同理,依次对行 $x ^ { 9 }$ 、行 $x ^ { 1 0 }$ 、行 $x ^ { 1 1 }$ 、行 $x ^ { 1 2 }$ 、行 $x ^ { 1 3 }$ 、行 $x ^ { 1 4 }$ 进行 如上 操作 。

第六步:依据表 4,得到乘积多项式 $P$ 。

$P = p _ { 7 } x ^ { 7 } + p _ { 6 } x ^ { 6 } + p _ { 5 } x ^ { 5 } + p _ { 4 } x ^ { 4 } + p _ { 3 } x ^ { 3 } + p _ { 2 } x ^ { 2 } + p _ { 1 } x ^ { 1 } + p _ { 0 } x ^ { 0 }$ 其中,

$$ \begin{array} { r l } & { p _ { 0 } = ( m _ { 0 } n _ { 0 } ) \oplus } \ & { ( m _ { 1 } n _ { 7 } ) \oplus ( m _ { 2 } n _ { 6 } ) \oplus ( m _ { 3 } n _ { 5 } ) \oplus ( m _ { 4 } n _ { 4 } ) \oplus ( m _ { 5 } n _ { 3 } ) \oplus ( m _ { 6 } n _ { 2 } ) \oplus ( m _ { 7 } n _ { 1 } ) } \ & { \oplus ( m _ { 2 } n _ { 7 } ) \oplus ( m _ { 3 } n _ { 6 } ) \oplus ( m _ { 4 } n _ { 5 } ) \oplus ( m _ { 5 } n _ { 4 } ) \oplus ( m _ { 6 } n _ { 3 } ) \oplus ( m _ { 7 } n _ { 2 } ) } \ & { \oplus ( m _ { 3 } n _ { 7 } ) \oplus ( m _ { 4 } n _ { 6 } ) \oplus ( m _ { 5 } n _ { 5 } ) \oplus ( m _ { 6 } n _ { 4 } ) \oplus ( m _ { 7 } n _ { 3 } ) } \ & { \oplus ( m _ { 4 } n _ { 7 } ) \oplus ( m _ { 5 } n _ { 6 } ) \oplus ( m _ { 6 } n _ { 5 } ) \oplus ( m _ { 7 } n _ { 4 } ) } \ & { \oplus ( m _ { 5 } n _ { 7 } ) \oplus ( m _ { 6 } n _ { 6 } ) \oplus ( m _ { 7 } n _ { 5 } ) } \ & { \oplus ( m _ { 5 } n _ { 7 } ) \oplus ( m _ { 6 } n _ { 6 } ) \oplus ( m _ { 7 } n _ { 5 } ) } \ & { \oplus ( m _ { 6 } n _ { 7 } ) \oplus ( m _ { 7 } n _ { 6 } ) } \end{array} $$

其它系数 $p _ { 1 } \circ \circ p _ { 2 } \circ p _ { 3 } \circ p _ { 4 } \circ p _ { 5 } \circ p _ { 6 } \circ p _ { 7 }$ 的表达式可以同样方法得到。 ( ) ( )p m n m n 1 7 2 6 3 5 4 4 5 3 6 2 7 1( ) ( ) ( ) ( ) ( ) ( ) ( )m n m n m n m n m n m n m n $\begin{array} { r l } & \begin{array} { r l } & { \Phi ( \mathbf { x } , \mathbf { y } ) } \ & { \mathbf { x } ^ { \prime } \bullet \mathbf { y } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime } } \ & { \mathbf { x } ^ { \prime \prime } } \ & { \mathbf { y } ^ { \prime \prime } } \end{array} \end{array}$ ) ( )( )( )( )( )( )5 0 5 1 4 2 3 3 2 4 1 5 0p m n m n m n m n m n m n ( )( )( )( )4 7 5 6 6 5 7 4m n m n m n m n ( )( )6 7 7 6m n m n ( )7 7m n ( )( )( )( )( )( )( )6 0 6 1 5 2 4 3 3 4 2 5 1 6 0p m n m n m n m n m n m n m n ( )( )( )5 7 6 6 7 5m n m n m n ( )7 7m n

$$ \begin{array} { r l } & { p _ { 7 } = ( m _ { 0 } n _ { 7 } ) \bigoplus ( m _ { 1 } n _ { 6 } ) \bigoplus ( m _ { 2 } n _ { 5 } ) \bigoplus ( m _ { 3 } n _ { 4 } ) \bigoplus ( m _ { 4 } n _ { 3 } ) \bigoplus ( m _ { 5 } n _ { 2 } ) \bigoplus ( m _ { 6 } n _ { 1 } ) \bigoplus ( m _ { 7 } n _ { 0 } ) \bigoplus } \ & { \left( m _ { 1 } n _ { 7 } \right) \bigoplus ( m _ { 2 } n _ { 6 } ) \bigoplus ( m _ { 3 } n _ { 5 } ) \bigoplus ( m _ { 4 } n _ { 4 } ) \bigoplus ( m _ { 5 } n _ { 3 } ) \bigoplus ( m _ { 6 } n _ { 2 } ) \bigoplus ( m _ { 7 } n _ { 1 } ) } \ & { \bigoplus ( m _ { 2 } n _ { 7 } ) \bigoplus ( m _ { 3 } n _ { 6 } ) \bigoplus ( m _ { 4 } n _ { 5 } ) \bigoplus ( m _ { 5 } n _ { 4 } ) \bigoplus ( m _ { 6 } n _ { 3 } ) \bigoplus ( m _ { 7 } n _ { 2 } ) } \ & { \bigoplus ( m _ { 3 } n _ { 7 } ) \bigoplus ( m _ { 4 } n _ { 6 } ) \bigoplus ( m _ { 5 } n _ { 5 } ) \bigoplus ( m _ { 6 } n _ { 4 } ) \bigoplus ( m _ { 7 } n _ { 3 } ) } \ & { \bigoplus ( m _ { 4 } n _ { 7 } ) \bigoplus ( m _ { 5 } n _ { 6 } ) \bigoplus ( m _ { 6 } n _ { 5 } ) \bigoplus ( m _ { 7 } n _ { 4 } ) } \ & { \bigoplus ( m _ { 5 } n _ { 7 } ) \bigoplus ( m _ { 6 } n _ { 6 } ) \bigoplus ( m _ { 7 } n _ { 5 } ) } \end{array} $$

表 4 多项式乘法运算分解表

| 幂 | 有贡献的乘积项 | 等效幂 | 附加的项 |

| x | mno | m,n7、m2n6、 m3n5、m4N4、 m5n3、 m6n2、m,n1; m2n7、 m3n6、 m4n5、m5N4、 m6N、m,n2;m3n7、m4n6、m5n5、m6n4、 m,n;m4n7、 m5n6、 m6n5、 m,n4;m5n7、 m6n6、 m-n;mn、mn; | |

| x | mon、mno | mn、m2n6、m3n5、m4n4、 m5n、m6n2、 m,n1;mn | |

| x² | mon2、mn、m2no | mn、m2n6、 m3n5、m4n4、 m5n3、m6n2、 m-n1; m3n7、 m4n6、 m5n5、 m6n4、 m-n3;m4n7、 m5n6、 m6n5、 m,n4;m5n7、m6n6、 m-n5;mn、mn6; | |

| x | mon3、mn2、 m2n)mn0 | m2n7、m3n6、m4n5、m5n4、m6n3、m,N2;m4n7、 m5n6、m6n5、 m,n4; m;n、 mn、 m,n; mn、 mn6: m,n | |

| 小 | mon4、 mn3、 m2n2mn、m4no | m3n、m4n6、m5n5、m6n4、 m,n3; m5n7、 m6n6、 m-n; m6n、 m-n6; m,n7 | |

| x | mon5、mn4、 m2n3mn2、 m4n、 m5n0 | m4n7、m5n6、m6n5、m,n4;m6n7、 m-n6; m-n7 | |

| x6 | mon6、 mn5、 m2n4m3n、m4n2、m5n)mn | m5n7、 m6n6、 m-n5; m-n7 | |

| x7 | mon7、 mn6、 m2n5 m3n4、 m4n、 m5N2mn、m,no | mn7、m2N6、 m3N5、m4N4、 m5N3、m6n2、 m-n1; m2n7、mn6、 m4n5、 m5n4、 m6n3、 m,n2; m3n7、m4n6、 m5n5、m6N4、 m,n3;m4n7、m5n6、 m6n5、 m,n4;m5n7、 m6n6、 m-n5; | |

| 小 | m,n、 m2n6、m3n5 m4n4、 m5n3、 m6n2mn | x+x²+x¹+1 | |

| 3 | m2n7、 m3N6、 m4N5mn4、 mn、m-n | x7+x²+1 | |

| 小 | m2n7、 m4n6 m5n5)m6n4、m,n3 | x²+x4+x²+1 | |

| x11 | m4n7、m5n6 m6n5、mn4 | x+x+x³+x²+1 | |

| x12 | m5n7、m6n6、m,n5 | x²+x+x4+x³+x²+1 | |

| x13 | m6n7、m,n6 | x+x4+x²+x²+1 | |

| x14 | mn | x+x²+x4+x²+x¹ |

根据上述分析,用 VHDL 描述有限域乘法运算:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mult8bit is

Port ( a : in STD_LOGIC_VECTOR (7 downto 0); b : in STD_LOGIC_VECTOR (7 downto 0); c : out STD_LOGIC_VECTOR (7 downto 0));

end mult8bit;

architecture Behavioral of mult8bit is signal ly : STD_LOGIC_VECTOR (14 downto 0); signal lym $:$ STD_LOGIC_VECTOR (7 downto 0); begin $y ( 1 4 ) { < } = \mathsf { a } ( 7 )$ and ${ \sf b } ( 7 )$ ; $\mathrm { l y } ( 1 3 ) \mathrm { < } =$ (a(7) and b(6)) xor (a(6) and b(7)) ; $\mathrm { l y } ( 1 2 ) \mathrm { < } =$ (a(7) and b(5)) xor (a(6) and b(6))xor (a(5) and b(7)); $\mathrm { l y } ( 1 1 ) \mathrm { < } =$ (a(7) and b(4)) xor (a(6) and b(5))xor (a(5) and b(6)) xor (a(4) and b(7)); ly $( 1 0 ) { < } =$ (a(7) and b(3)) xor (a(6) and b(4))xor (a(5) and b(5)) xor (a(4) and b(6))xor (a(3) and b(7)); $\mathrm { { l y } } ( 9 ) { < } = ( \mathrm { { a } } ( 7 )$ and b(2)) xor (a(6) and b(3))xor (a(5) and b(4)) xor (a(4) and b(5))xor (a(3) and b(6)) xor

(a(2) and b(7)); $\mathrm { { l y } } ( 8 ) { < } = ( \mathrm { { a } } ( 7 )$ and b(1)) xor (a(6) and b(2))xor (a(5) and b(3)) xor (a(4) and b(4))xor (a(3) and b(5)) xor

(a(2) and b(6))xor (a(1) and b(7)); ly $( 7 ) < =$ (a(7) and b(0)) xor (a(6) and b(1))xor (a(5) and b(2)) xor (a(4) and b(3))xor (a(3) and b(4)) xor

(a(2) and b(5))xor (a(1) and b(6)) xor (a(0) and b(7)); ly $( 6 ) \textlessgtr =$ (a(6) and b(0)) xor (a(5) and b(1))xor (a(4) and b(2)) xor (a(3) and b(3))xor (a(2) and b(4)) xor

(a(1) and b(5))xor (a(0) and b(6)); ly $( 5 ) { < } =$ (a(5) and b(0)) xor (a(4) and b(1))xor (a(3) and b(2)) xor (a(2) and b(3))xor (a(1) and b(4)) xor

(a(0) and b(5)); ly $4 ) < =$ (a(4) and b(0)) xor (a(3) and b(1))xor (a(2) and b(2)) xor (a(1) and b(3))xor (a(0) and b(4)); $\mathrm { l y } ( 3 ) { \mathrel { \mathop { < } } } = ( \mathrm { a } ( 3 )$ and b(0)) xor (a(2) and b(1))xor (a(1) and b(2)) xor (a(0) and b(3)); ly $( 2 ) { < } =$ (a(2) and b(0)) xor (a(1) and b(1))xor (a(0) and b(2)); $\mathrm { l y } ( 1 ) { \ < } =$ (a(1) and b(0)) xor (a(0) and b(1)); $\mathrm { { l y } ( 0 ) \mathrm { { < = } } } ( \mathrm { { a } ( 0 ) }$ and ${ \bf b } ( 0 ) \mathrm { \Sigma }$ ) ; $\mathrm { { l y m } } ( 7 ) { < } = \mathrm { { l y } } ( 7 )$ xor ly(8) xor ly(9) xor ly(10) xor ly(11) xor ly(12);

$\mathrm { l y m } ( 6 ) { < } = \mathrm { l y } ( 6 )$ xor ly(12) xor ly(14); $\mathrm { l y m } ( 5 ) { < } = \mathrm { l y } ( 5 )$ xor ly(11) xor ly(13) xor ly(14); $\mathrm { l y m } ( 4 ) { < } = \mathrm { l y } ( 4 )$ xor ly(10) xor ly(12) xor ly(13) xor ly(14); $\mathrm { l y m } ( 3 ) { \ < } = \mathrm { l y } ( 3 )$ xor ly(9) xor ly(11) xor ly(12) xor ly(13) xor ly(14); $\mathrm { l y m } ( 2 ) { < } = \mathrm { l y } ( 2 )$ xor ly(8) xor ly(10) xor ly(11) xor ly(12) xor ly(13); $\mathrm { l y m } ( 1 ) { < } = \mathrm { l y } ( 1 )$ xor ly(8) xor ly(14); $\mathrm { l y m } ( 0 ) { < } = \mathrm { l y } ( 0 )$ xor ly(8) xor ly(9) xor ly(10) xor ly(11) xor ly(12) xor ly(13); $\mathsf { c } { \mathsf { < } } { \mathsf { = } } \mathsf { l y m }$ ; end Behavioral;

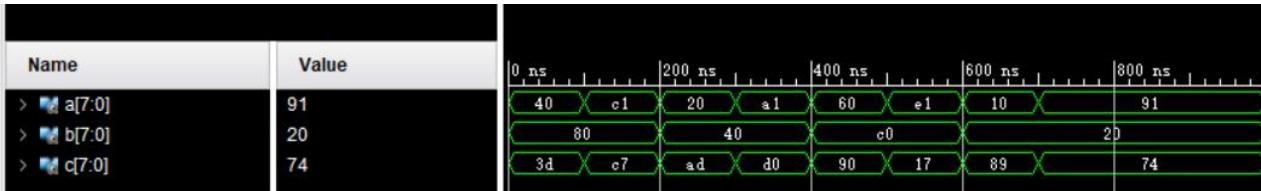

在 VIVADO 软件环境下仿真验证。仿真波形如图 13 所示。给定被乘数 01000000( $4 0 _ { \mathrm { H } }$ )、乘数10000000( $8 0 _ { \mathrm { H } }$ ),得乘积为 00111101( $3 \mathrm { d } _ { \mathrm { H } }$ ),与理论计算结果一致。给定被乘数 10010001( $\mathrm { \bf ~ 9 1 _ { H } }$ )、乘数 00100000( $2 0 _ { \mathrm { H } } \mathrm { . }$ ),得乘积为 01110100( $7 4 _ { \mathrm { H } } ,$ ),与理论计算结果一致。

图 13 仿真波形

6.3 设计由 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ 定义的有限域 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 内 Reed-Solomon 编码器

6.3.1 加法、除法、乘法运算

(1)加法运算

做加法运算时用二进制形式表示有限域中的元素便于运算的实现,对应位做异或运算即可。

$$ \begin{array} { l } { { \alpha ^ { 5 } + \alpha ^ { 6 } = ( 1 0 1 1 ) \oplus ( 1 1 1 1 ) = 0 1 0 0 = \alpha ^ { 2 } } } \ { { { } } } \ { { \alpha ^ { 2 } + \alpha ^ { 7 } = ( 0 1 0 0 ) \oplus ( 0 1 1 1 ) = 0 0 1 1 = \alpha ^ { 1 2 } } } \end{array} $$

(2)除法运算

$$ { \frac { \alpha ^ { 4 } } { { \alpha } ^ { 2 } } } = \alpha ^ { 2 } $$

$$ \frac { \alpha ^ { 2 } } { \alpha ^ { 4 } } = \frac { \alpha ^ { 2 } \alpha ^ { 1 5 } } { \alpha ^ { 4 } } = \alpha ^ { 1 3 } $$

(3)乘法运算

用软件编程方法实现有限域乘法运算时,用幂形式表示元素便于运算的实现,对幂做加法运算即可。

$$ \begin{array} { l } { { \alpha ^ { 2 } \times \alpha ^ { 4 } = \alpha ^ { 6 } } } \ { { { } } } \ { { \alpha ^ { 8 } \times \alpha ^ { 9 } = \alpha ^ { 1 7 } = \alpha ^ { 1 5 } \times \alpha ^ { 2 } = \alpha ^ { 2 } } } \end{array} $$

在 6.1 中已经实现了任意两个域元素的相乘运算,为方便实现 Reed-Solomon 编码,下面再给出用二进制形式表示的任意域元素与某个固定域元素相乘的硬件电路。

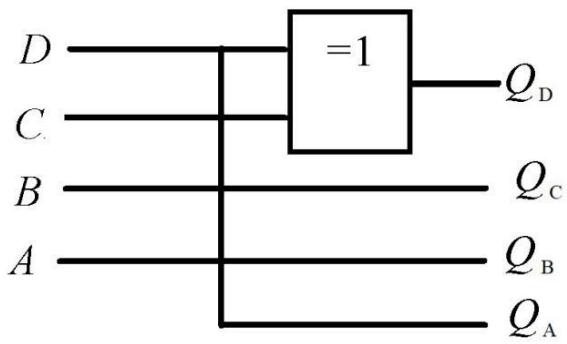

DCBA 表示某个域元素的二进制形式, $Q _ { \mathrm { D } } Q _ { \mathrm { C } } Q _ { \mathrm { B } } Q _ { \mathrm { A } }$ 表示域元素 $D C B A$ 乘以域元素 $\alpha$ 后的乘积的二进制形式,电路如图 14 所示。

图 14 域元素 $D$ 、 $C$ 、 $B$ 、 $A$ 乘 $\alpha$ 运算的电路

实现某个域元素 $D$ 、 $C$ 、 $B$ 、 $A$ 乘 $\alpha ^ { 2 }$ 的运算,可用两级图 14 所示的电路相联结,同理, $\mathbf { n }$ 级电路相联结可实现某个域元素 $D$ 、 $C$ 、 $B$ 、 $A$ 乘以 $\alpha ^ { \mathfrak { n } }$ $\mathbf { \tilde { n } } = 1$ ,2,3,……,15)的运算,但是这种方法占用的电路面积大,运算速度慢。可考虑用一级电路实现域元素 $D$ 、 $C$ 、 $B$ 、 $A$ 乘以 $\alpha ^ { \mathfrak { n } }$ 的运算,方法如表 5 所示。 $Q _ { \mathrm { D } }$ 、 $\mathcal { Q } _ { \mathrm { C } }$ 、 $Q _ { \mathrm { B } }$ 、 $Q _ { \mathrm { { A } } }$ 是乘法运算的结果。 $\textcircled{+}$ 表示异或运算符号。

表5 域元素 $D$ 、 $C$ 、 $B$ 、 $A$ 乘 $\alpha ^ { \mathfrak { n } }$ 运算的电路结构示意

| a | α² | a | a4 | q5 | |

| QD | COD | BOCOD | A田B④C④D | A田B④C | A田BOD |

| Qc | B | A | D | CD | BOCOD |

| QB | A | D | COD | BOCOD | A田BC④D |

| QA | D | COD | BOCOD | A田BC④D | ABC |

| q6 | a7 | q8 Q | Q | α10 | |

| QD | AC | BD | AOCOD | BC | AB |

| Qc | ABOCOD | A田BOC | ABOD | AC | BD |

| QB | A田BC | ABD | AC | BD | AC④D |

| QA | ABOD | AC | BD | ACOD | BC |

| a11 | α12 | a13 | α14 | α15 | |

| QD | AD | C | B | A | D |

| Qc | ACOD | BOC | AB | AD | C |

| QB | BOC | AB | AOD | C | B |

| QA | AB | AD | C | B | A |

6.3.2 RS 编码器

一个 RS 码的码字是一组有限域的符号,其中每一个符号都是伽罗华域的元素,RS(n,k)编码器的参数如下:

m:每个符号比特数;

n : 码长 $\mathrm { n } = 2 ^ { \mathrm { m } } - 1$ ;

t :纠错符号个数;

d :码距 ${ \mathrm { d } } = 2 \mathrm { t } + 1$ ;

$\mathrm { k \Omega }$ :信息符号个数;

所设计的 RS(15,13)编码器的技术指标如下:

$$ \mathrm { m } = 4 \ ; \qquad \mathrm { n } = 1 5 = 2 ^ { 4 } - 1 \ ; \qquad \mathrm { t } = 1 \ ; \qquad \mathrm { d } = 3 \ ; \qquad \mathrm { k } = 1 3 $$

(1)校验符号的计算原理

所设计的 RS (15,13) 编码器可以纠正一个符号内的任意数目的位错误。当一个符号错误出现时,有两个未知量:码字内产生错误的符号的位置和错误的图样。要想求解两个未知量,必须列出两个联立方程。

记 RS(15,13)码的一个码字为:

d1 d2 d3 d4 d5 d6 d7 d8 d9 d10 d11 d12 d13 R S其中:

d1 d2 d3 d4 d5 d6 d7 d8 d9 $d _ { 1 0 }$ $d _ { 1 1 }$ $d _ { 1 2 }$ $d _ { 1 3 }$ 为信息符号, $R$ 、 $S$ 为校验符号。

列出联立方程如下:

$\left{ \begin{array} { l l } { ( \displaystyle \sum _ { \mathrm { i } = 1 } ^ { 1 3 } d _ { \mathrm { i } } ) + R + S = 0 } \ { \qquad } \ { ( \displaystyle \sum _ { \mathrm { i } = 1 } ^ { 1 3 } d _ { \mathrm { i } } \alpha ^ { \mathrm { i } } ) ^ { + } \alpha ^ { ^ { 1 4 } R + } \alpha ^ { ^ { 1 5 } S = 0 } } \end{array} \right.$ 记 $( \sum _ { \mathrm { i = 1 } } ^ { 1 3 } d _ { \mathrm { i } } )$ 为 $S _ { 0 }$ 记 $( \sum _ { \mathrm { i = 1 } } ^ { 1 3 } d _ { \mathrm { i } } \alpha ^ { \mathrm { i } } )$ 为 $S _ { 1 }$

则上面两个方程变为

$$ \left{ \begin{array} { l } { { \displaystyle { \cal S } _ { 0 } + { \cal R } + { \cal S } = 0 } } \ { { \displaystyle { \cal S } _ { 1 } + { \cal Q } ^ { 1 4 } { \cal R } + { \cal Q } ^ { 1 5 } { \cal S } = 0 } } \end{array} \right. $$

再变形为

$$ \left{ \begin{array} { l l } { { R + S = S _ { 0 } } } \ { { } } \ { { \alpha ^ { 1 4 } R + \alpha ^ { 1 5 } S = \alpha ^ { 1 4 } R + S = S _ { 1 } } } \end{array} \right. $$

由式(1)得 $S = S _ { 0 } + R$ ,再代入式(2)得

$$ \alpha ^ { ^ { 1 4 } } R + S _ { 0 } + R = S _ { 1 } $$

整理得: 0 114( 1)R S S

$$ R = \frac { S _ { 0 } + S _ { 1 } } { \alpha ^ { 1 4 } + 1 } = \frac { S _ { 0 } + S _ { 1 } } { \alpha ^ { 1 1 } } = ( S _ { 0 } + S _ { 1 } ) \alpha ^ { 4 } $$

式(3)即为校验符号 $R$ 的计算公式。

将式(3)代入 $S = S _ { 0 } + R$ ,整理得

$$ S = S _ { 0 } + R = S _ { 0 } + ( S _ { 0 } + S _ { 1 } ) \alpha ^ { 4 } $$

式(4)即为校验符号 $S$ 的计算公式。

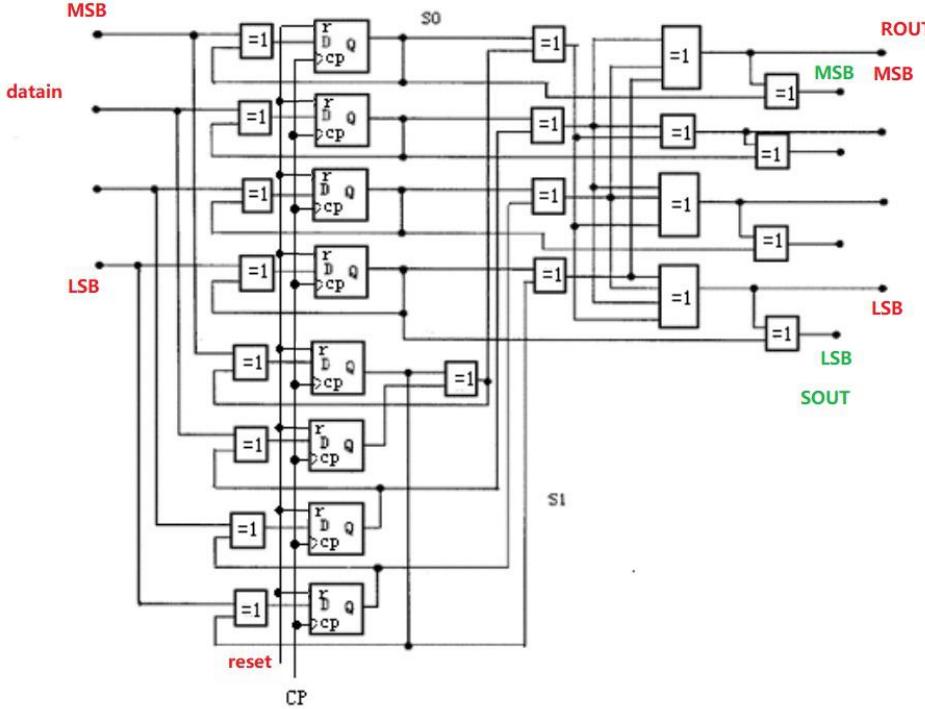

按式(3)和式(4)设计的计算校验符号 $R$ 、 $S$ 的电路如图 15 所示。

图 15 计算校验符号 $R$ 、 $S$ 的电路

(2)电路工作原理

首先,电路初始化。 reset 输入端送高电平,所有触发器被清零。

然后,信息符号 $d _ { 1 3 }$ 送入输入端 datain, $d _ { 1 3 } \oplus 0 = d _ { 1 3 }$ ,在时钟脉冲 CP的第一个上升沿, $d _ { 1 3 }$ 打入触发器输出端,接着信息符号 $d _ { 1 2 }$ 送入输入端 datain, $d _ { 1 3 } \oplus d _ { 1 2 }$ 做异或运算的结果送入触发器的输入端 D,在时钟脉冲 CP 的第二个上升沿,将其打入触发器输出端。

同上, $d _ { 1 2 }$ 、 $d _ { 1 1 }$ 、d10、d9、d8、d7、d6、d5、d4、 $d _ { 3 }$ 、 $d _ { 2 }$ 、 $d _ { 1 }$ 每隔一个时钟周期依次从输入端 datain送入电路。

$$ \begin{array} { r l } & { S _ { 0 } = d _ { 1 3 } \oplus d _ { 1 2 } \oplus d _ { 1 1 } \oplus d _ { 1 0 } \oplus d _ { 9 } \oplus d _ { 8 } \oplus d _ { 7 } \oplus d _ { 6 } \oplus d _ { 5 } \oplus d _ { 4 } \oplus d _ { 3 } \oplus d _ { 2 } \oplus d _ { 1 } } \ & { S _ { 1 } = ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( d ( ( ( ( d ( 4 } 1 _ 3 a ) 4 ) ) \alpha 4 ) ) \alpha 4 ) ) \alpha \oplus d _ { 1 1 ) ) ) \alpha \oplus d _ { 1 0 } ) \alpha \oplus d _ { 9 } ) \alpha \oplus } \ & { d _ { 8 } ) \alpha \oplus d _ { 7 } ) \alpha \oplus d _ { 6 } ) \alpha \oplus d _ { 5 } ) \alpha \oplus d _ { 4 } ) \alpha \oplus d _ { 3 } ) \alpha \oplus d _ { 2 } ) \alpha \oplus d _ { 1 } ) \alpha = ( \sum _ { \mathrm { i = 1 } } ^ { 1 3 } d _ { \mathrm { i } } \alpha ^ { \mathrm { i } } ) } \end{array} $$

得到 $S _ { 0 }$ 和 $S _ { 1 }$ 后, $S _ { 0 }$ 和 $S _ { 1 }$ 做异或运算,再乘以 $\alpha ^ { 4 }$ ,得到校验符号 $R$ 。

校验符号 $R$ 和 $S _ { 0 }$ 做异或运算,得到校验符号 $S$ 。

在第 13 个时钟脉冲的上升沿后,输出端 ROUT、SOUT 可分别得到校验符号 $R$ 和校验符号 $S$ 。

VHDL 语言描述的编码器如下:

library IEEE;

use IEEE.std_logic_1164.all;

entity rs_encoder is Port ( datain $:$ in STD_LOGIC_VECTOR (3 downto 0); reset : in STD_LOGIC; cp $:$ in STD_LOGIC; rout : inout STD_LOGIC_VECTOR (3 downto 0); sout : out STD_LOGIC_VECTOR (3 downto 0));

end rs_encoder;

architecture Behavioral of rs_encoder is signal s0,s1:STD_LOGIC_VECTOR (3 downto 0); signal d:STD_LOGIC_VECTOR (7 downto 0); signal q:STD_LOGIC; signal lq:STD_LOGIC_VECTOR (3 downto 0); component xor2 is port (a,b:in STD_LOGIC;c:out STD_LOGIC ); end component; component dflipflop is port (cp,reset,d:in STD_LOGIC;q:out STD_LOGIC); end component;

begin u1:xor2 port map(datain(3),s0(3),d(7)); u2:xor2 port map(datain(2),s0(2),d(6));

u3:xor2 port map(datain(1),s0(1),d(5));

u4:xor2 port map(datain(0),s0(0),d(4));

u5:xor2 port map(datain(3),s1(3),d(3));

u6:xor2 port map(datain(2),s1(2),d(2));

u7:xor2 port map(datain(1),s1(1),d(1));

u8:xor2 port map(datain(0),s1(0),d(0));

u9 :dflipflop port map (cp,reset,d(7),s0(3));

u10:dflipflop port map (cp,reset,d(6),s0(2)); u11:dflipflop port map (cp,reset,d(5),s0(1)); u12:dflipflop port map (cp,reset,d(4),s0(0)); u13:dflipflop port map (cp,reset,d(3),s1(0)); u14:dflipflop port map (cp,reset,d(2),q); u15:dflipflop port map (cp,reset,d(1),s1(2)); u16:dflipflop port map (cp,reset,d(0),s1(1)); u17:xor2 port map (s1(0),q,s1(3)); $\scriptstyle 1 9 < = \mathbf { s } 0$ xor s1; rout( $3 ) { < } { = } \mathrm { l q } ( 2 )$ xor lq(1) xor lq(0); rout(2 $) { < } = \mathsf { l q } ( 3 )$ xor lq(2); rout $\scriptstyle ( 1 ) \leq = \ln q ( 3 )$ xor lq(2) xor lq(1); rou $( 0 ) { < } \mathrm { = } \mathrm { l q } ( 3 )$ xor lq(2) xor lq(1) xor lq(0); sout $< =$ rout xor s0;

nd Behavioral;

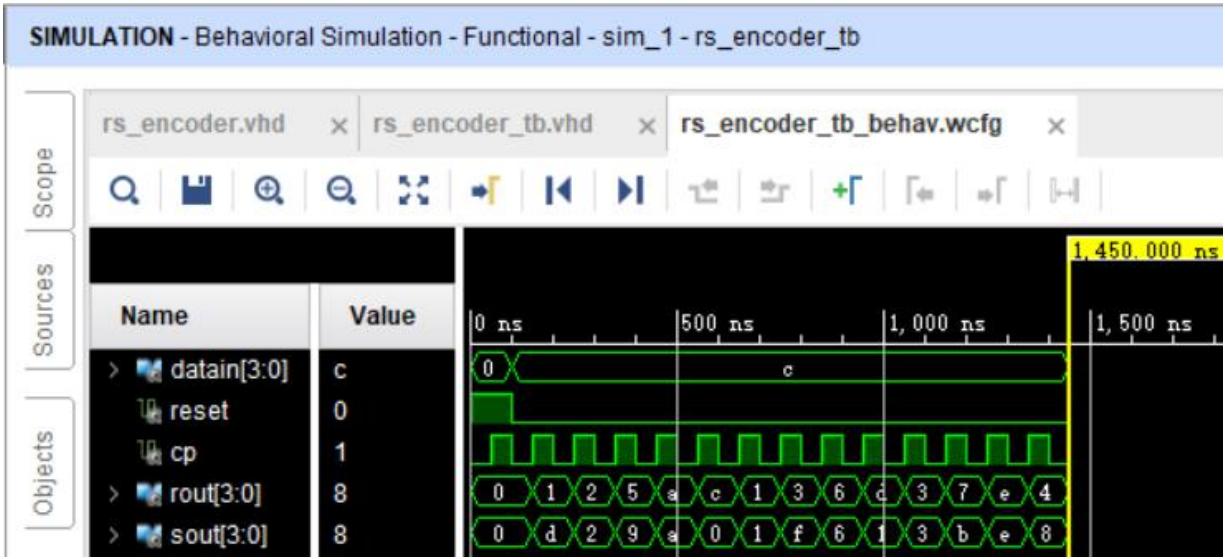

在 VIVADO 软件环境下仿真验证。仿真波形如图 16 所示。信息符号 $d _ { 1 3 }$ 、d12、d11、d10、d9、d8、d7、d6、d5、d4、d3、d2、 $d _ { 1 }$ 均给定 1100,依次从输入端 datain 输入电路,经过 13个时钟脉冲后,在电路的输出端 ROUT 得到校验符号 $R { = } 0 1 0 0$ ,在电路的输出端 SOUT 得到校验符号 $S { = } 1 0 0 0$ 。与理论计算结果一致。

图 16 仿真波形

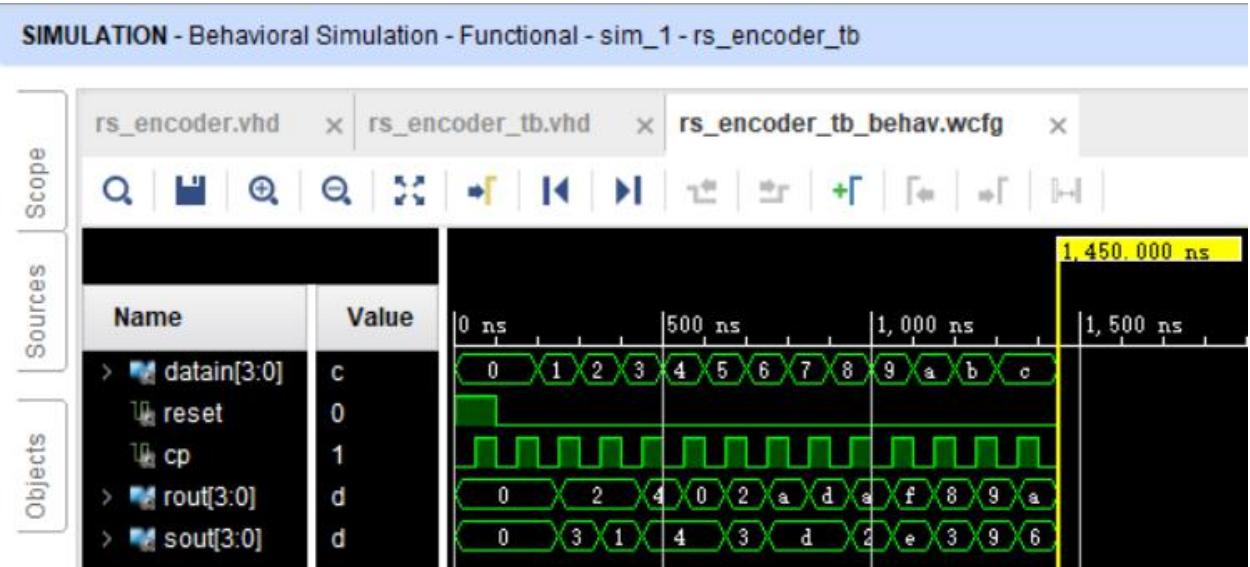

在 VIVADO 软件环境下仿真验证。仿真波形如图 17 所示。信息符号 $d _ { 1 3 }$ 、d12、d11、d10、d9、d8、d7、d6、d5、d4、d3、 $d _ { 2 }$ 、 $d _ { 1 }$ 依次给定为 0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100,从输入端 datain 依次输入电路,经过 13 个时钟脉冲后,在电路的输出端ROUT 得到校验符号 $R { = } 1 0 1 0$ ,其十六进制数码的表示为 a,在电路的输出端 SOUT 得到校验符号$S { = } 0 1 1 0$ ,其十六进制数码的表示为 6。与理论计算结果一致。

图 17 仿真波形

6.4 设计1 位数码管显示电路,显示 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 的域元素

设计一个七段显示译码器,要求与共阴数码管配套,显示一位十六进制数的类似手写形状,其中的几个字型要求如下:1、6、9、A、B、C、D、E、F 必须显示为如图 18所示的形状:

图18 显示的形状

(1)用门电路实现。

解:约定:

4 位二进制数输入信号分别用 A(3)、A(2)、A(1)、A(0)表示;7 个输出信号分别用 Y(6)、Y(5)、Y(4)、Y(3)、Y(2)、Y(1)、Y(0)表示,分别对应 a、b、c、d、e、f、g 段。真值表如表 6 所示。

表 6 真值表

| A(3) | A(2) | A(1) | A(0) | Y(6)、 Y(5)、) a b | Y(4)、Y(3)、Y(2)、Y(1)、Y(0) C d | e | f g |

| 0 | 0 | 0 | 0 | 1 1 | 1 1 | 1 1 | 0 |

| 0 | 0 | 0 | 1 | 0 1 | 1 0 | 0 0 | 0 |

| 0 | 0 | 1 | 0 | 1 1 | 0 1 | 1 | 0 1 |

| 0 | 0 | 1 | 1 | 1 1 | 1 1 | 0 0 | 1 |

| 0 | 1 | 0 | 0 | 0 1 | 1 0 | 0 | 1 1 |

| 0 | 1 | 0 | 1 | 1 0 | 1 1 | 0 | 1 1 |

| 0 | 1 | 1 | 0 | 1 0 | 1 1 | 1 | 1 1 |

| 0 | 1 | 1 | 1 | 1 1 | 1 0 | 0 | 0 0 |

| 1 | 0 | 0 | 0 | 1 1 | 1 1 | 1 1 | 1 |

| 1 | 0 | 0 | 1 | 1 1 | 1 1 | 0 | 1 1 |

| 1 | 0 | 1 | 0 | 1 1 | 1 0 | 1 | 1 1 |

| 1 | 0 | 1 | 1 | 0 0 | 1 1 | 1 | 1 1 |

| 1 | 1 | 0 | 0 | 1 0 | 0 1 | 1 | 1 0 |

| 1 | 1 | 0 | 1 | 0 1 | 1 1 | 1 | 0 1 |

| 1 | 1 | 1 | 0 | 1 0 | 0 1 | 1 | 1 1 |

| 1 | 1 | 1 | 1 | 1 0 | 0 0 | 1 | 1 1 |

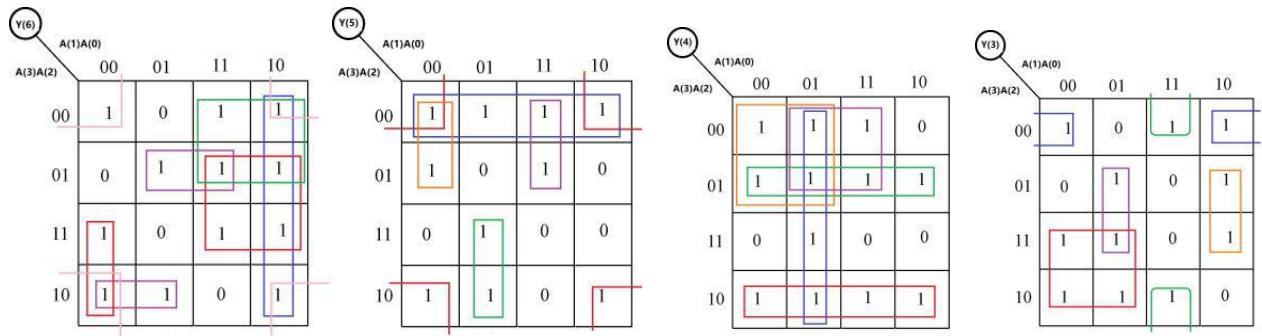

卡诺图法化简如图 19 所示,得到最简与或式。

图 19 卡诺图法化简

$$ \begin{array} { r l } & { Y ( 6 ) = A ( 1 ) \dot { A } ( 0 ) + A ( 2 ) \dot { A } ( 1 ) + \dot { A } ( 2 ) \dot { A } ( 0 ) + \dot { A } ( 3 ) \dot { A } ( 1 ) + \dot { A } ( 3 ) \dot { A } ( 2 ) \dot { A } ( 0 ) + A ( 3 ) \dot { A } ( 1 ) \dot { A } ( 0 ) } \ & { Y ( 5 ) = \dot { A } ( 2 ) \dot { A } ( 0 ) + \dot { A } ( 3 ) \dot { A } ( 2 ) + \dot { A } ( 3 ) \dot { A } ( 0 ) + A ( 3 ) \dot { A } ( 1 ) \dot { A } ( 0 ) + \dot { A } ( 3 ) \dot { A } ( 1 ) \dot { A } ( 0 ) } \ & { Y ( 4 ) = \overline { { { A } ( 3 ) } } \dot { A } ( 1 ) + \dot { A } ( 3 ) \dot { A } ( 0 ) + \overline { { { A } ( 3 ) } } \dot { A } ( 2 ) + \overline { { { A } ( 1 ) } } ( 4 ) + \dot { A } ( 3 ) + \dot { A } ( 3 ) \dot { A } ( 2 ) } \ & { Y ( 5 ) = A ( 3 ) \overline { { { A } ( 1 ) } } + \overline { { { A } ( 3 ) } } \dot { A } ( 2 ) \dot { A } ( 0 ) + A ( 2 ) \overline { { { A } ( 1 ) } } \dot { A } ( 0 ) + \overline { { { A } ( 2 ) } } \dot { A } ( 1 ) \dot { A } ( 0 ) + A ( 2 ) \dot { A } ( 1 ) \overline { { A } ( 0 ) } } \ & { Y ( 2 ) = \overline { { { A } ( 2 ) } } \dot { A } ( 0 ) + A ( 3 ) \dot { A } ( 2 ) + A ( 3 ) \dot { A } ( 1 ) + \dot { A } ( 0 ) + \overline { { { A } ( 2 ) } } \dot { A } ( 1 ) \dot { A } ( 0 ) + \dot { A } ( 2 ) \dot { A } ( 1 ) \dot { A } ( 0 ) } \ & { Y ( 2 ) = \overline { { { A } ( 2 ) } } \dot { A } ( 0 ) + A ( 3 ) \dot { A } ( 2 ) + A ( 3 ) \dot { A } ( 1 ) + \dot { A } ( 0 ) } \ & { Y ( 1 ) = \overline { { { A } ( 1 ) } } \dot { A } ( 0 ) + A ( 3 ) \dot { A } ( 3 ) \dot { A } ( 2 ) + \dot { A } ( 3 ) \dot { A } ( 2 ) \overline { { 4 ( 1 ) } } + A ( 2 ) \dot { A } ( 1 ) \overline { { 4 ( 0 ) } } } \ & \end{array} $$

根据上述最简与或式,画出逻辑电路图,用 Multisim12 仿真验证正确性。

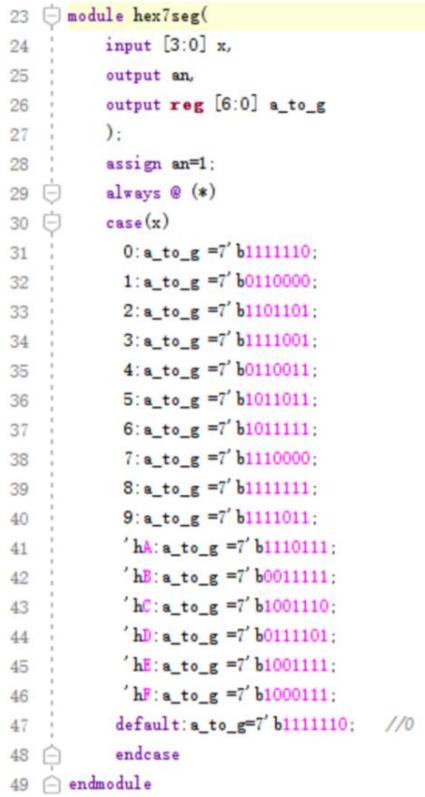

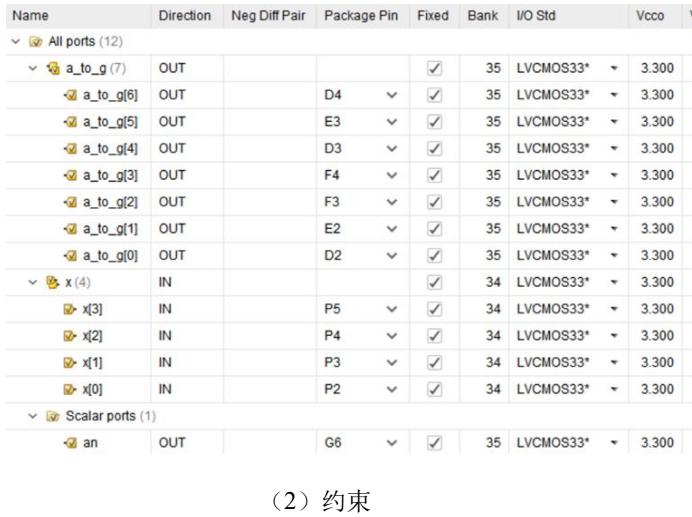

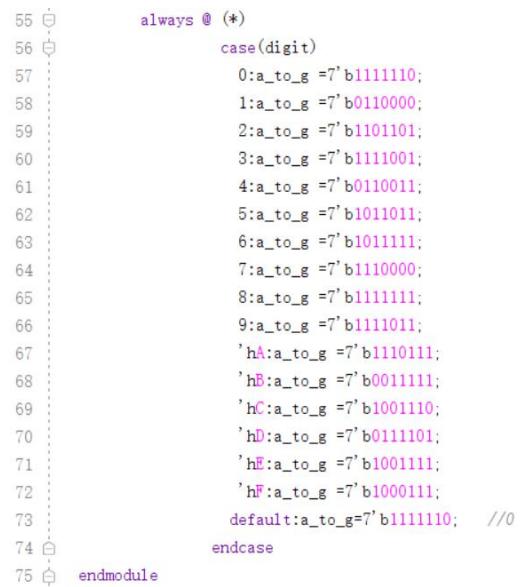

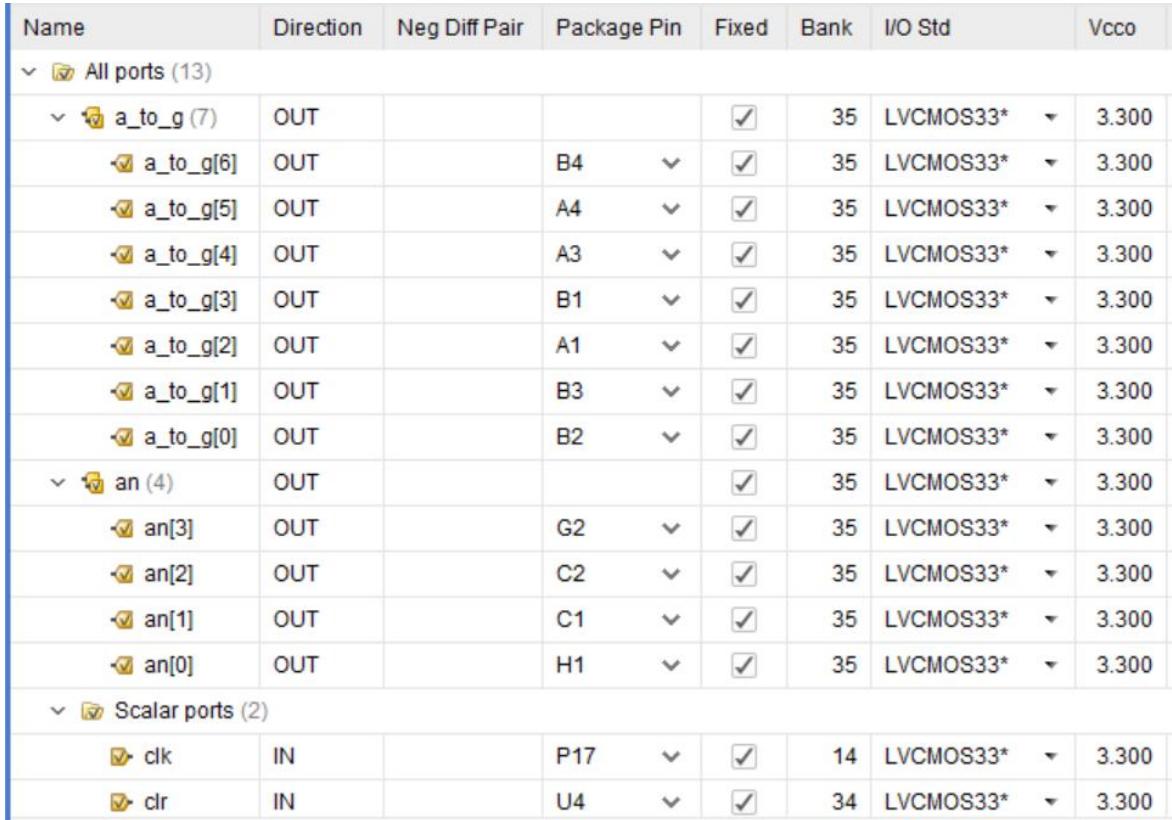

(2)编写 Verilog-HDL 程序,使用 EGO1 口袋实验板上 FPGA 芯片 XC7A35TCSG324-1 实现。在最右侧的数码管上显示。

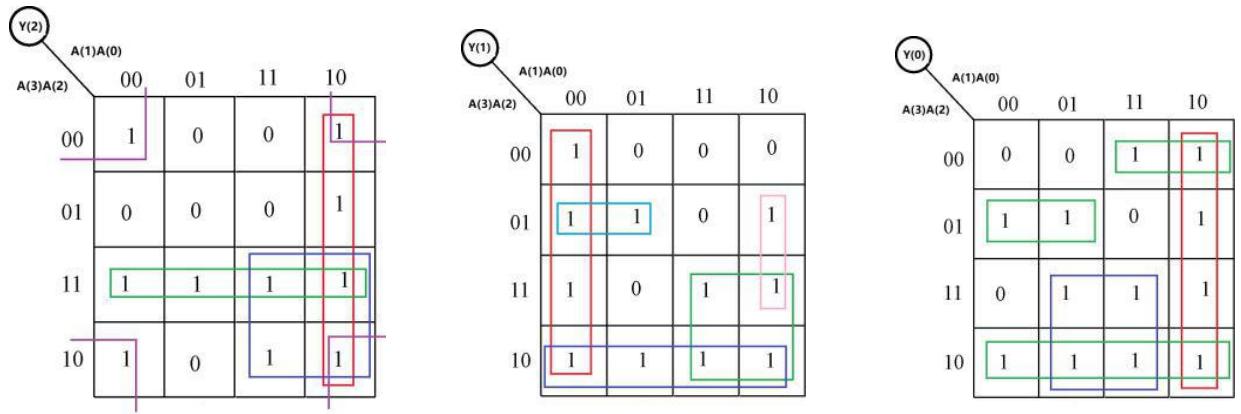

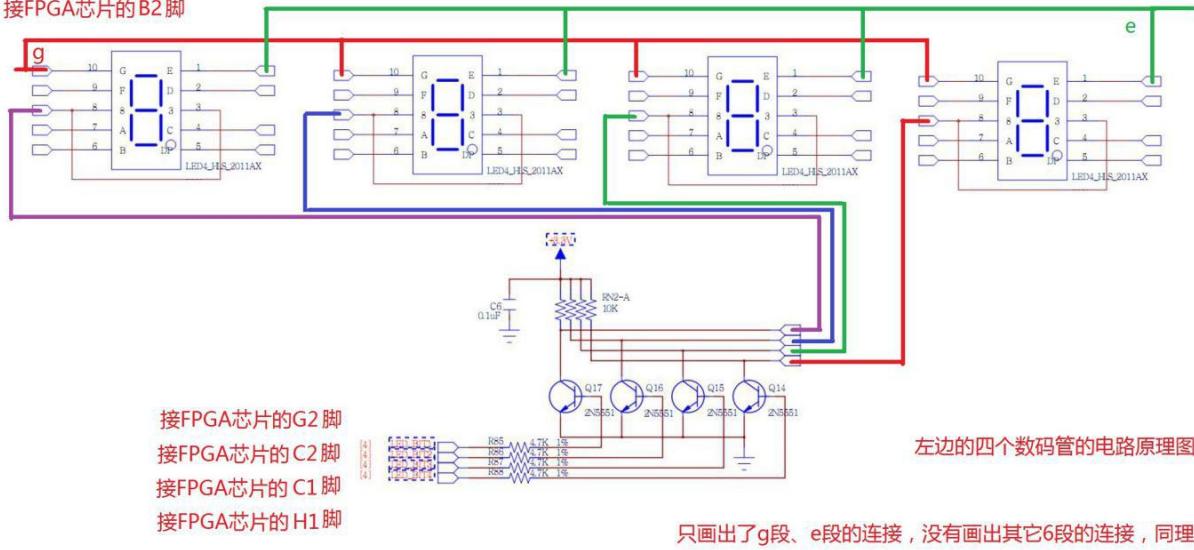

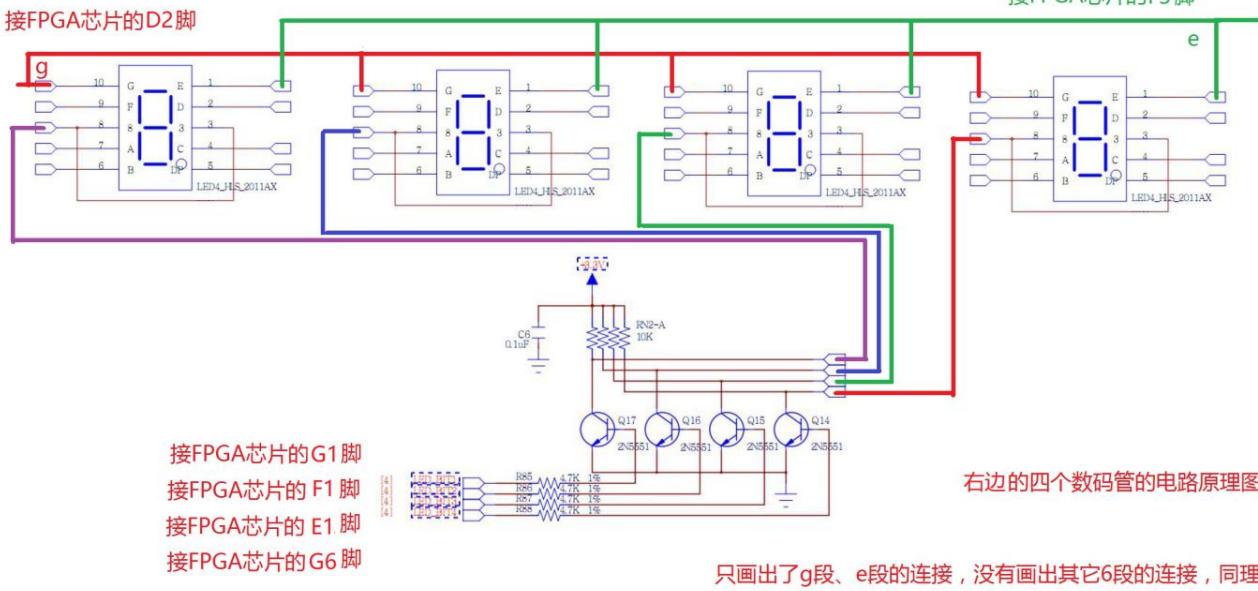

解:EGO1 口袋实验板有 8 个数码管,分为两组。左边 4 个为一组,右边 4 个为一组。左边一组的 4 个数码管的 a 段接在一起,同理,其它段 b、c、d、e、f、g 段也分别连接在一起,左边一组的 4 个数码管的公共端分别由不同的 FPGA 引脚控制,电路原理图如图 20所示。

图 20 左边一组4 个数码管的电路原理图

右边一组的 4 个数码管的 a 段接在一起,同理,其它段 b、c、d、e、f、g 段也分别连接在一起,右边一组的这 4 个数码管的公共端分别由不同的 FPGA 引脚控制,电路原理图如图 21 所示。

图 21 右边一组 4个数码管的电路原理图

Verilog-HDL 源程序及约束如图 22 所示。 在最右侧数码管的位置,显示 $f ( x ) = x ^ { 4 } + x ^ { 3 } + 1$ 定义的有限域 ${ \mathrm { G F } } ( 2 ^ { 4 } )$ 域元素,如图 23所示。

(1)源程序

图 22 Verilog-HDL 源程序及约束

图 23 域元素 $\alpha ^ { 1 3 }$ 的 EGO1 口袋实验板的显示

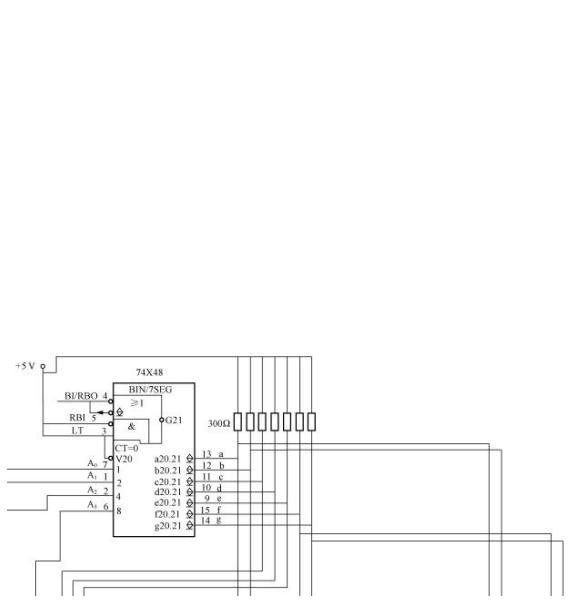

6.5 设计2 位数码管静态、动态显示电路

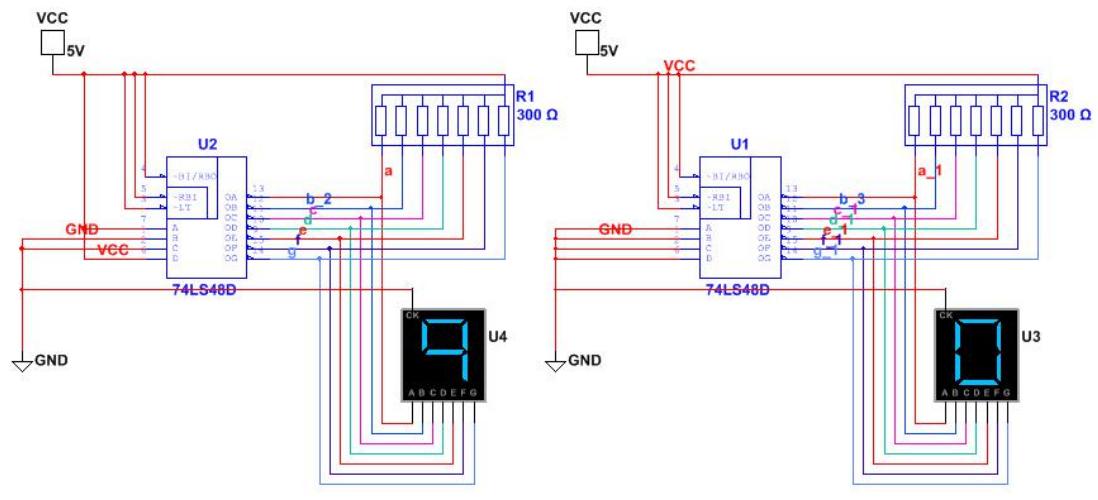

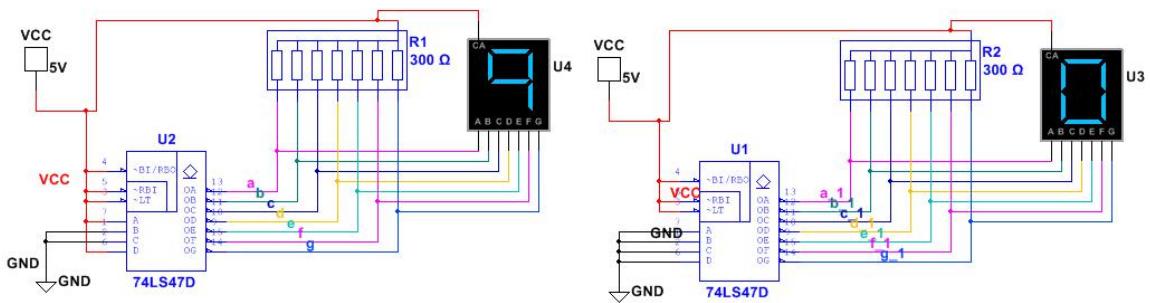

(1)设计 2 位共阴数码管静态显示电路,显示两个域元素 9、0。使用 2 个七段显示译码器 74LS48、2 个共阴数码管,在 Multisim12 软件环境下搭接电路,验证设计。

解:所谓静态显示,就是每个数码管的输入信号来自自己对应的那个七段显示译码器芯片的输出。即一个数码管对应一个七段显示译码器。电路原理图如图 24 所示。Multisim12 软件仿真如图 25所示。

图 24 静态显示域元素 9、0 (共阴数码管)

图 25 静态显示域元素 9、0 (共阴数码管) ( Multisim12软件仿真)

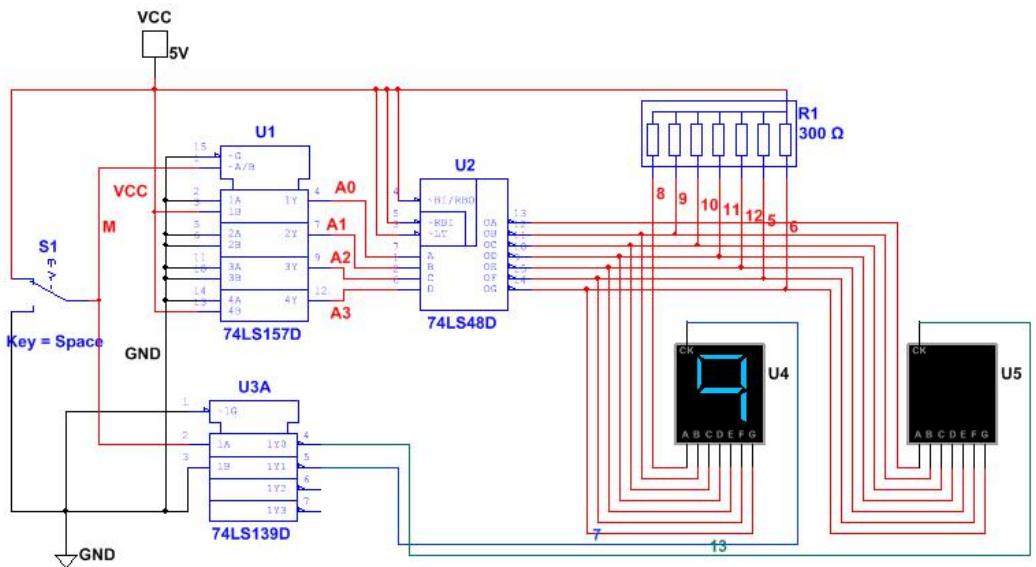

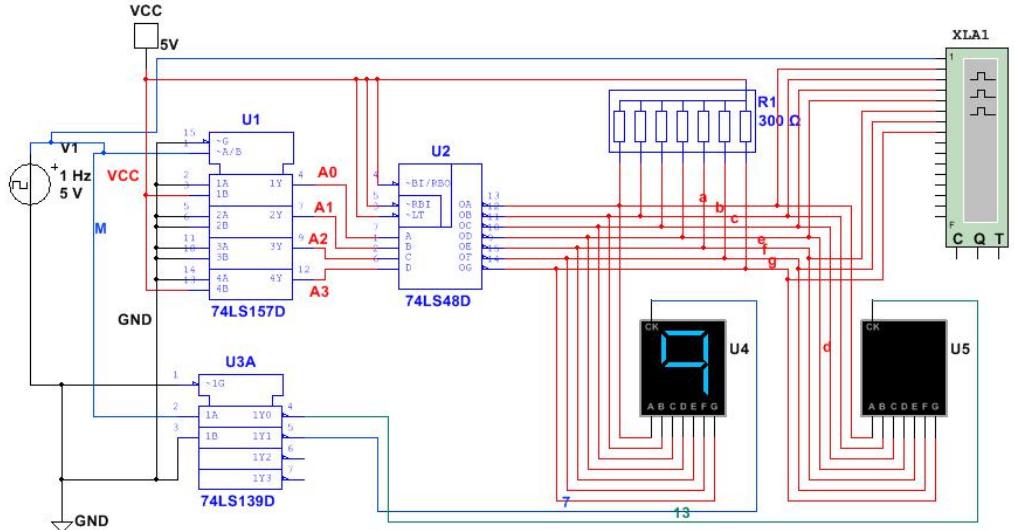

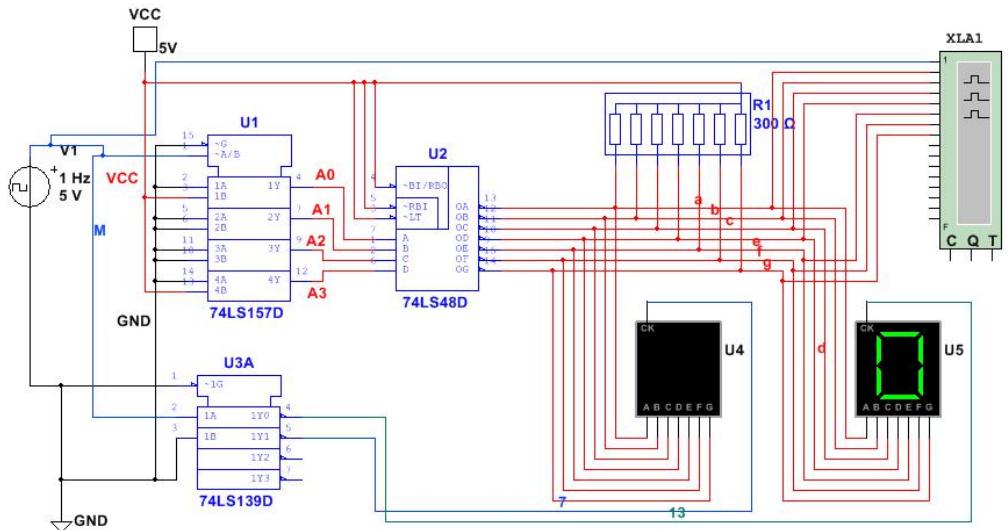

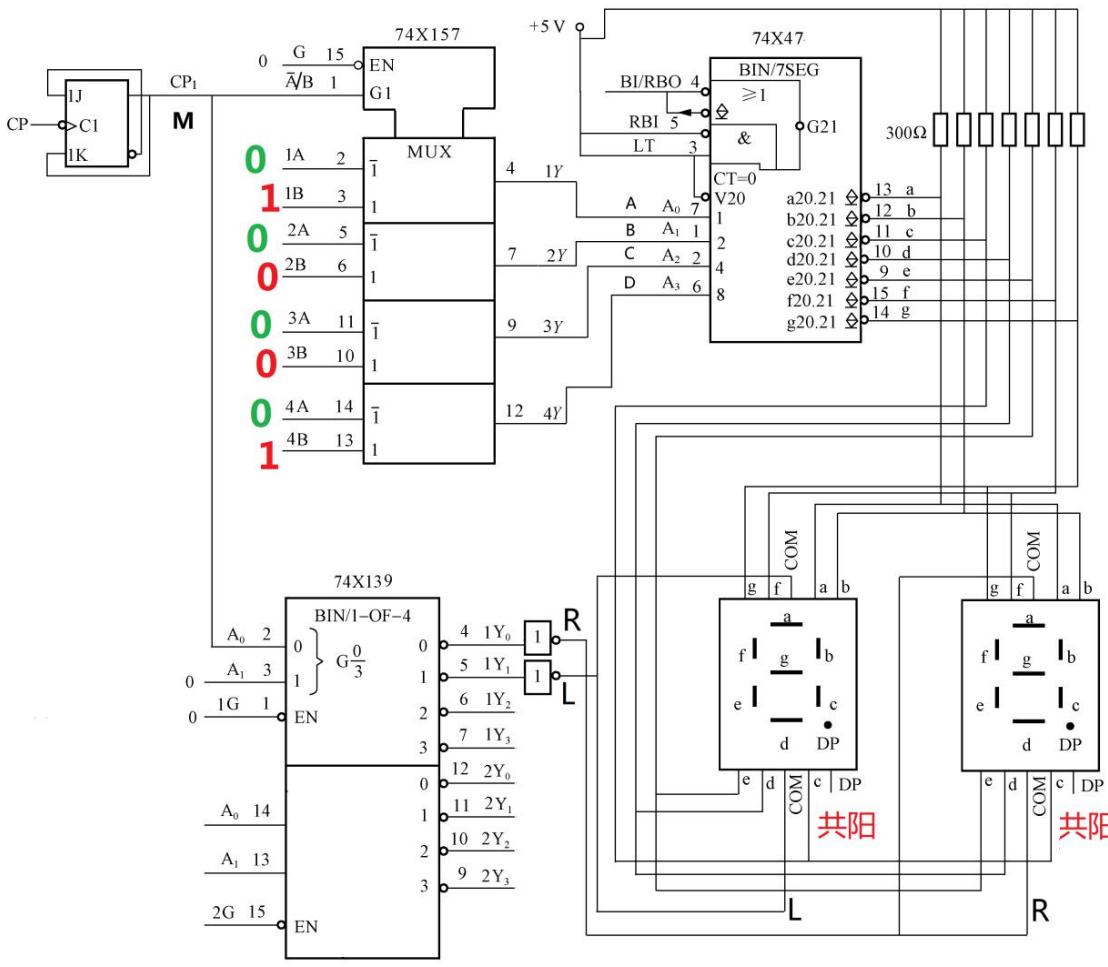

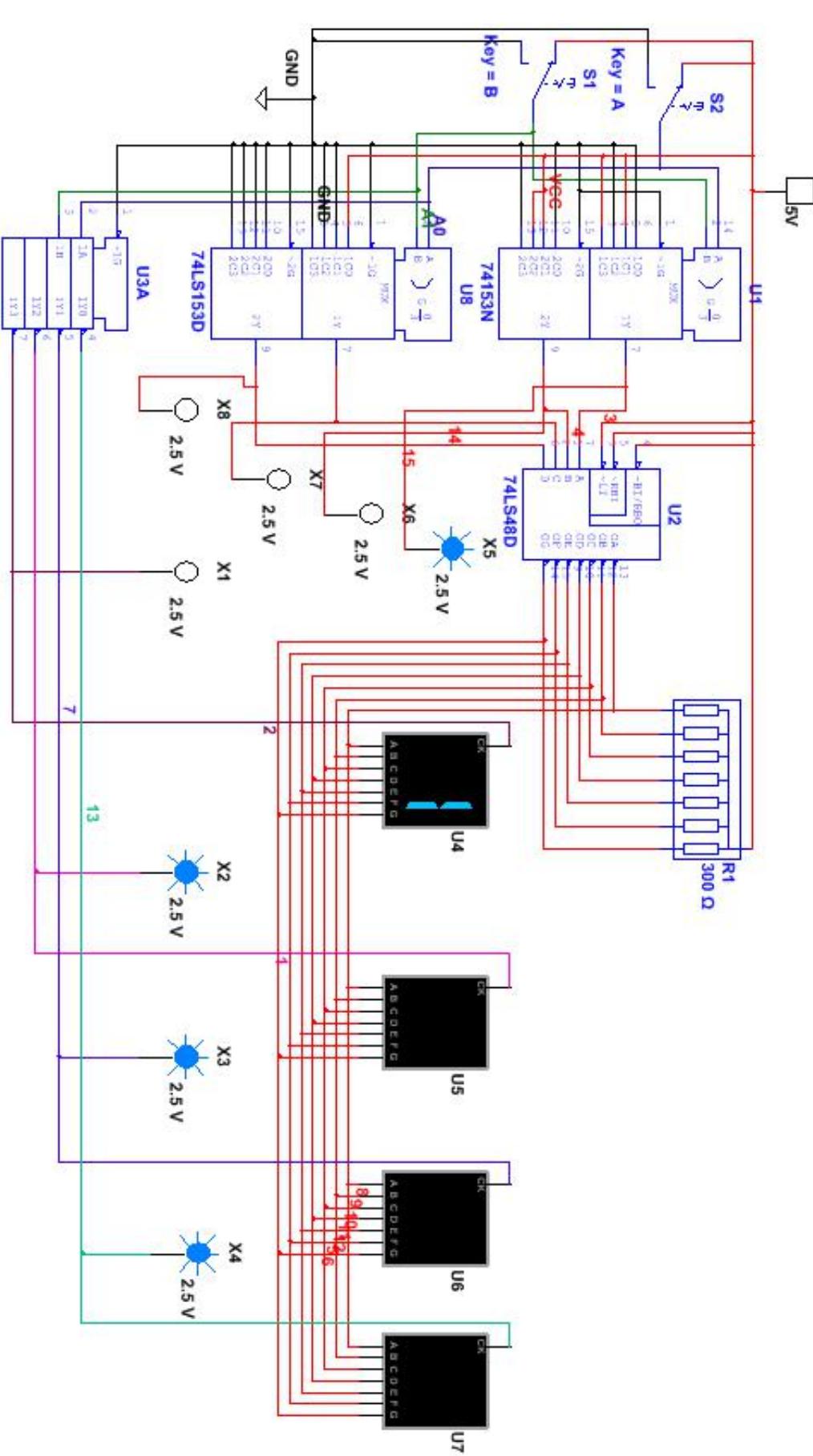

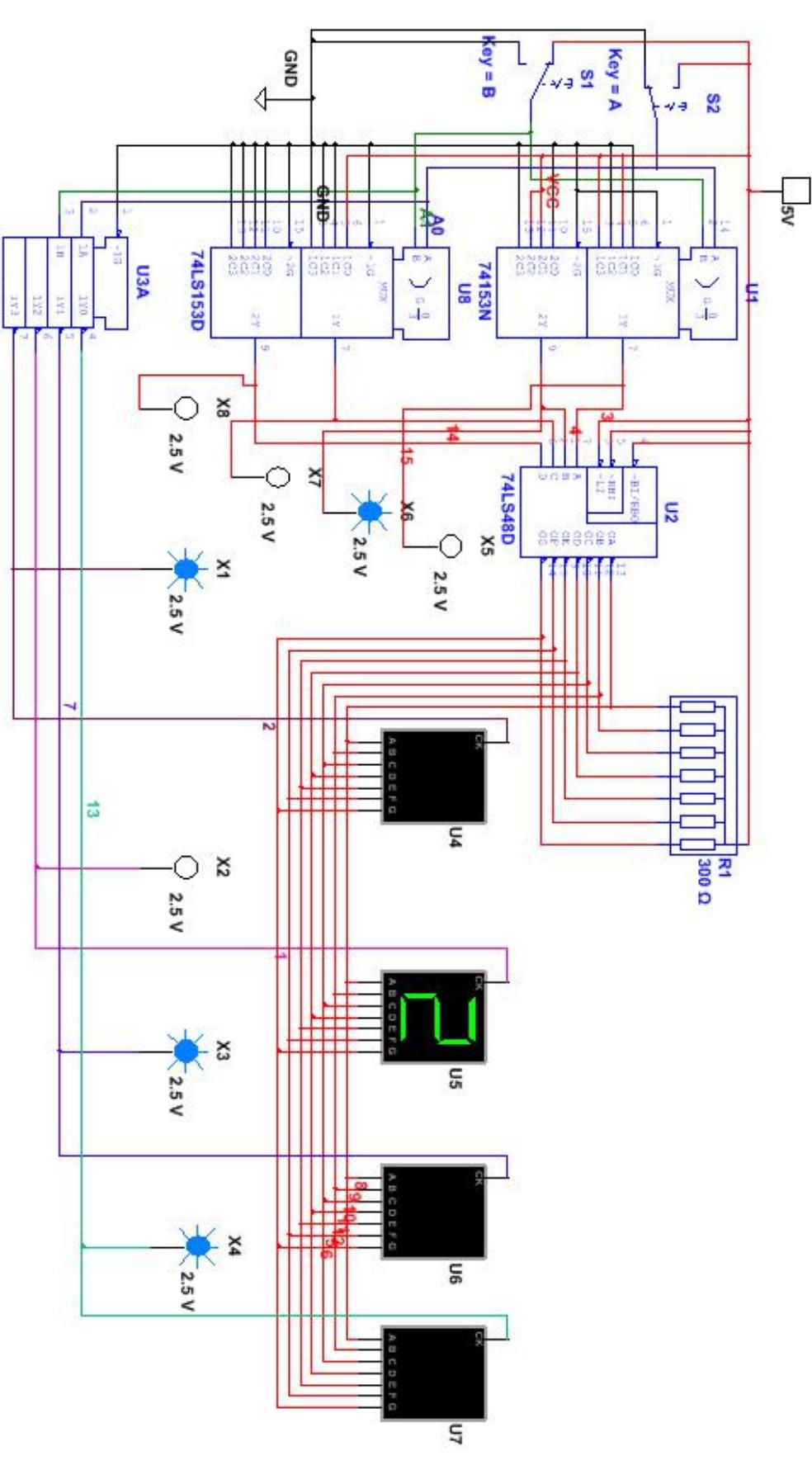

(2)设计 2 位共阴数码管动态显示电路,显示两个域元素 9、0。使用数据选择器 MUX、二进制译码器、1 个七段显示译码器 74LS48、2 个共阴数码管,在 Multisim12 软件环境下搭接电路,验证设计。

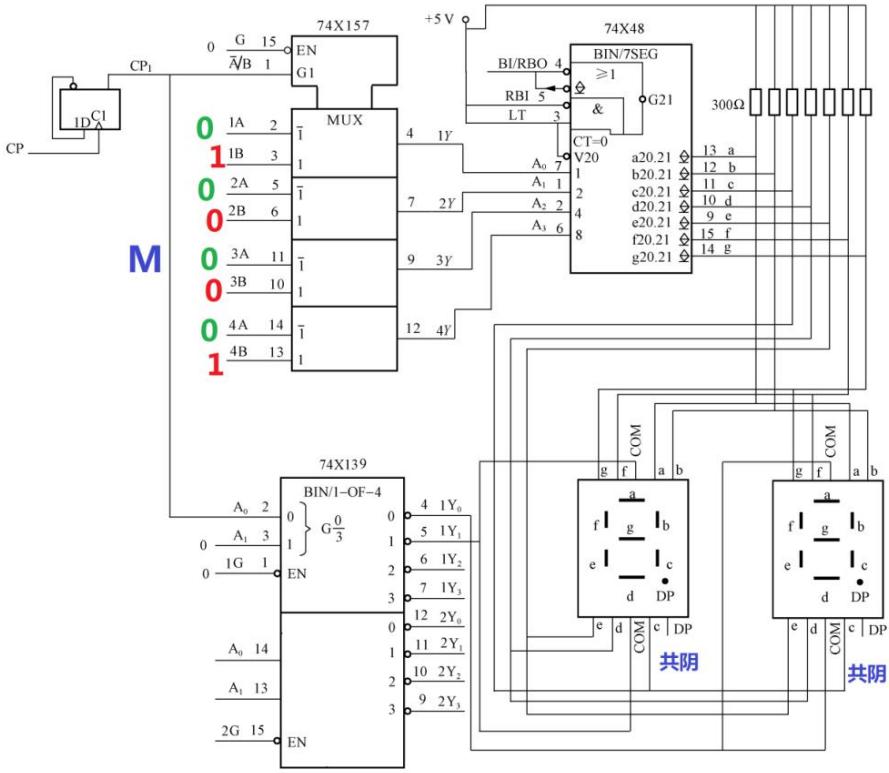

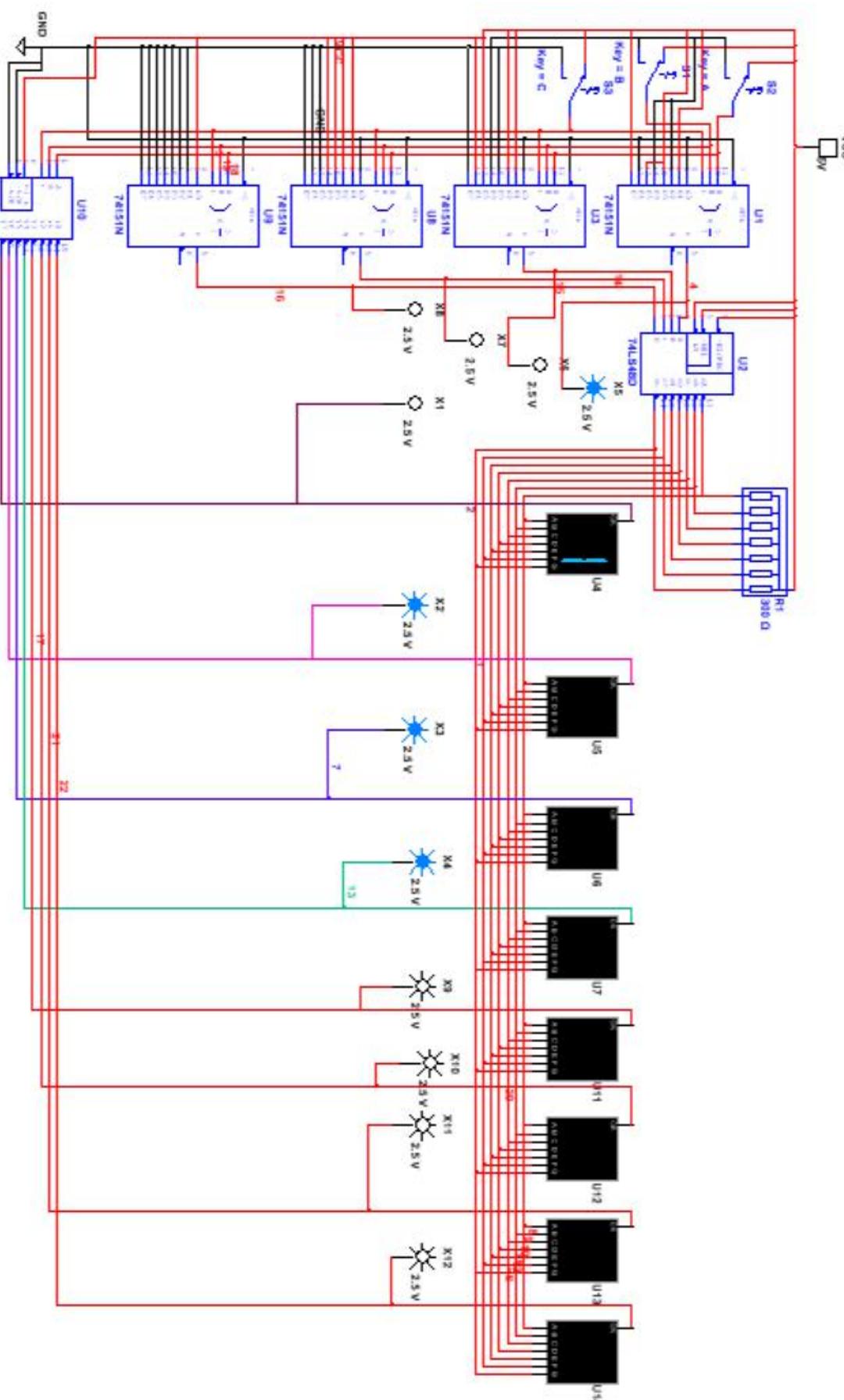

解:所谓动态显示,就是所有的数码管的输入信号全部来自一个七段显示译码器芯片的输出。电路如图 26 所示。包括 1 位二进制计数器(产生 CP1 信号)、二选一数据选择器(通道数为 4 位)、1线-2 线二进制译码器、七段显示译码器、数码管。Multisim12 软件仿真如图 27、图 28、图 29、图30所示。

图 26 动态显示域元素 9、0(共阴数码管)

图 27 $\scriptstyle \mathbf { M } = 0$ 时右边数码管显示域元素 0( Multisim12软件仿真)

图 28 $\mathbf { M } { = } 1$ 时左边数码管显示域元素 9( Multisim12软件仿真)

图 29 M信号的值 0、1 不断变化(Multisim12软件无法仿真视觉暂留的效果)

图 30 M信号的值 0、1 不断变化(Multisim12软件无法仿真视觉暂留的效果)

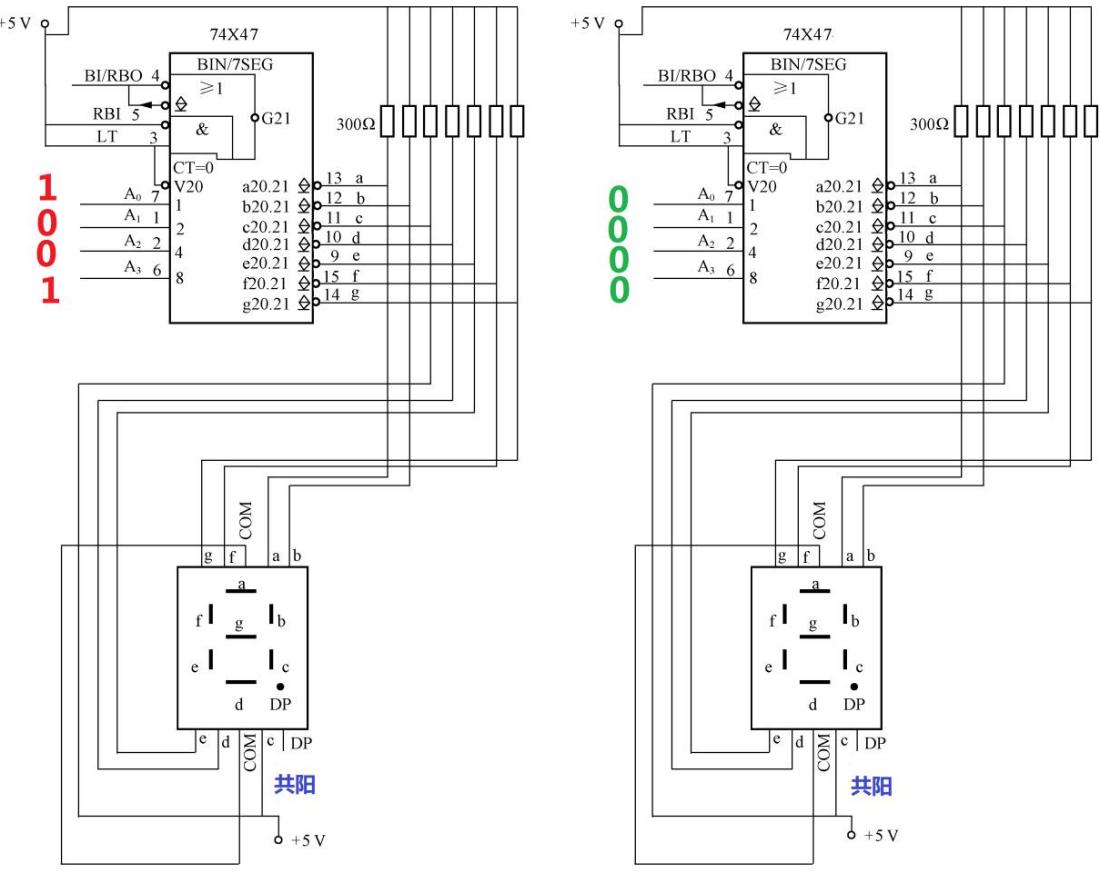

(3)设计 2 位共阳数码管静态显示电路,显示两个域元素 9、0。使用 2 个七段显示译码器 74LS47、2 个共阳数码管,在 Multisim12 软件环境下搭接电路,验证设计。

解:所谓静态显示,就是每个数码管的输入信号来自自己对应的那个七段显示译码器芯片的输出。

即一个数码管对应一个七段显示译码器,电路如图 31 所示。Multisim12 软件仿真如图 32所示。

图 31 静态显示域元素 9、0 (共阳数码管)

图 32 静态显示域元素 9、0 (共阳数码管) ( Multisim12软件仿真)

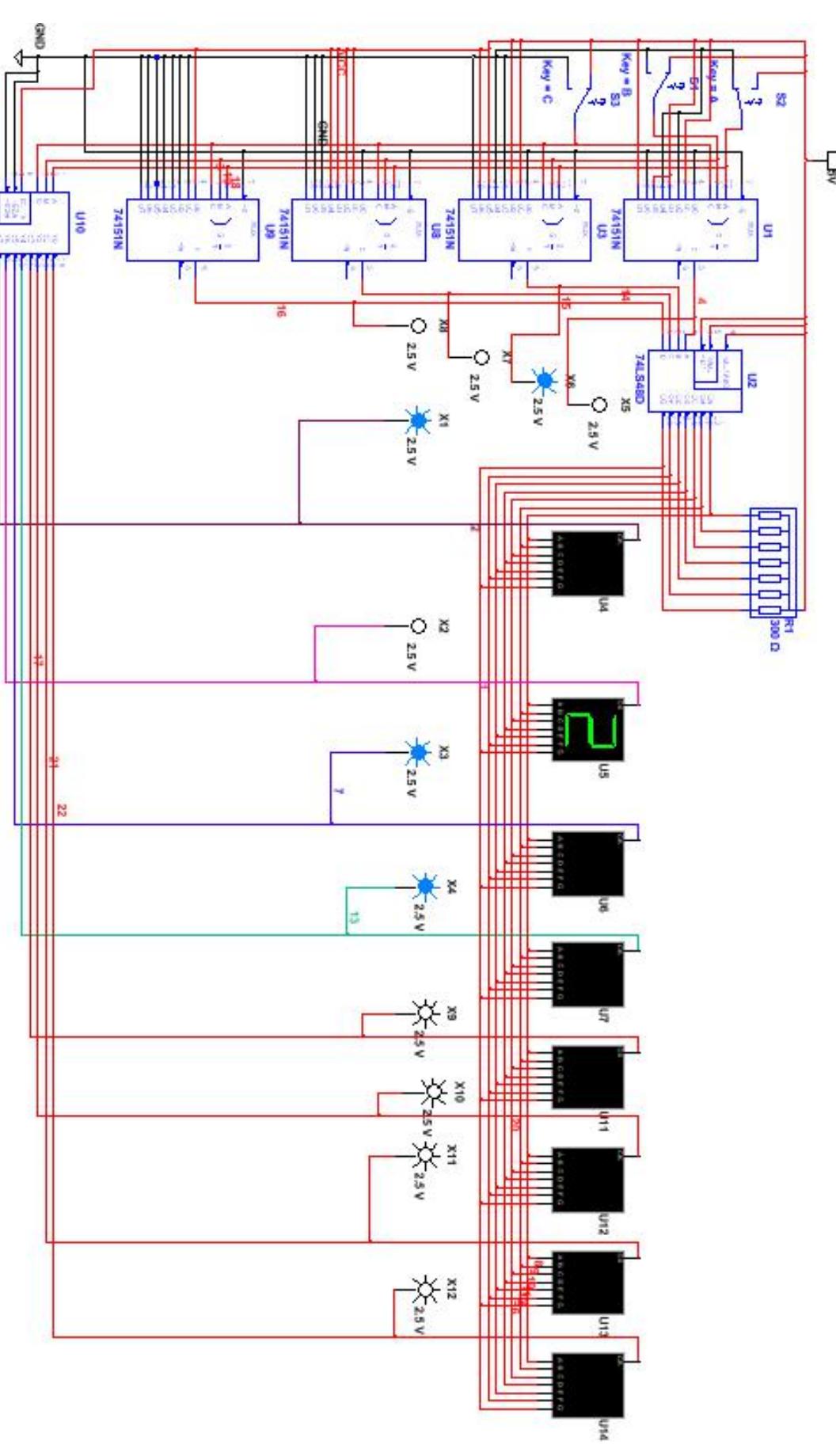

(4)设计 2 位共阳数码管动态显示电路,显示两个域元素 9、0。使用数据选择器 MUX、二进制译码器、1 个七段显示译码器 74LS47、2 个共阳数码管,在 Multisim12 软件环境下搭接电路,验证设计。

解:所谓动态显示,就是所有的数码管的输入信号全部来自一个七段显示译码器芯片的输出。电路如图 33 所示。Multisim12 软件仿真如图 34、图 35 所示。

图 33 动态显示域元素 9、0 (共阳数码管)

图 34 $\scriptstyle \mathbf { M } = 0$ 时右边数码管显示域元素 0( Multisim12软件仿真)

图 35 $\mathbf { M } { = } 1$ 时左边数码管显示域元素9( Multisim12软件仿真)

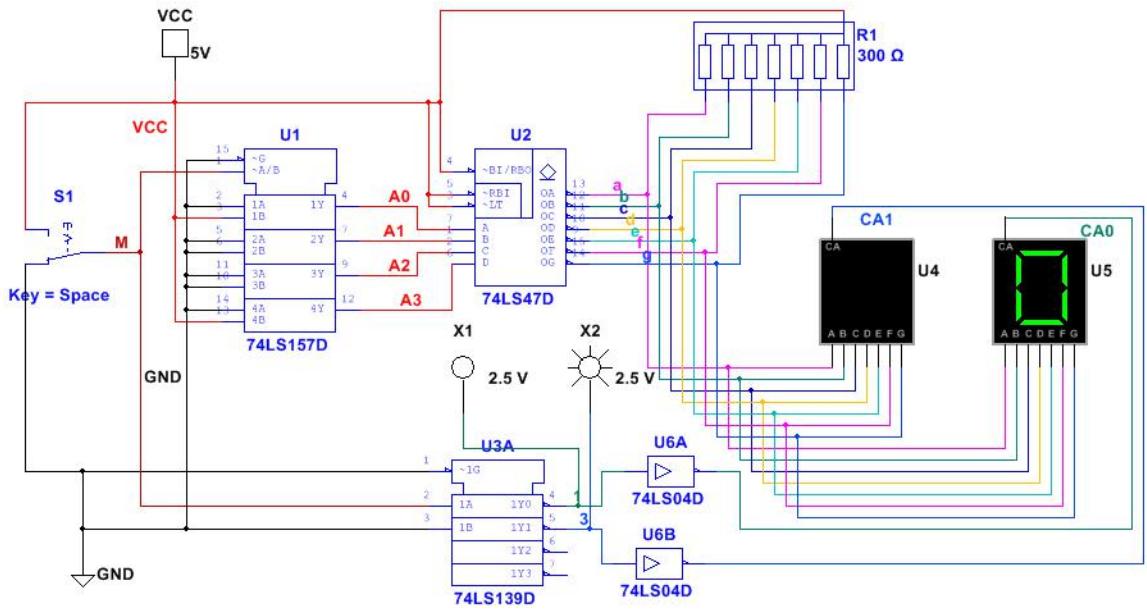

(5) 在 EGO1 口袋实验板上设计 2 位共阴数码管动态显示电路,显示两个域元素 9、0。在 VIVADO环境下输入 Verilog-HDL 程序,经过仿真、综合、实现、编写约束文件,下载到 EGO1 口袋实验板的 FPGA 芯片 XC7A35TCSG324-1 中,验证正确性。要求使用 EGO1 口袋实验板的最左侧的 2 个数码管。

解:源程序如下:

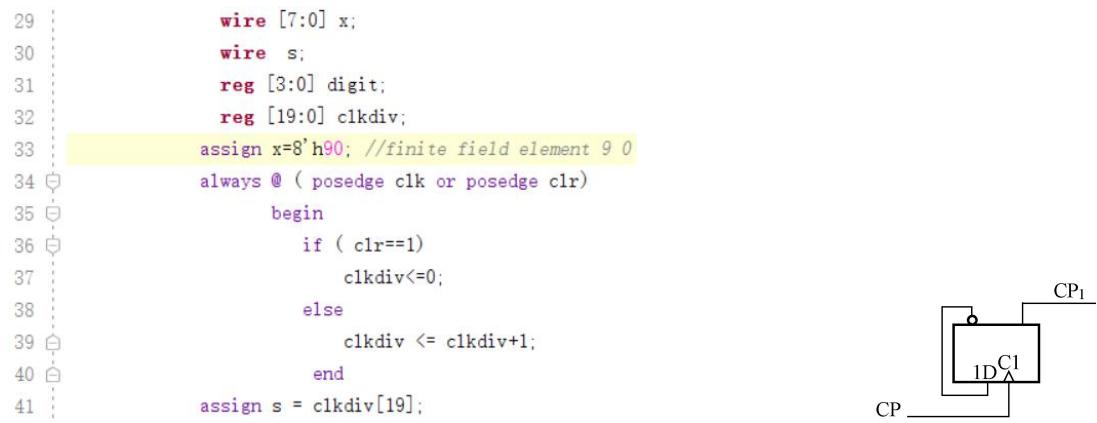

module x7seg12( input clk, input clr, output reg [6:0] a_to_g, output reg [1:0] an ); wire [7:0] x; wire s; reg [3:0] digit; reg [19:0] clkdiv; assign $\scriptstyle \mathbf { x } = 8 ^ { \prime } \mathbf { h } 9 0$ ; //finite field element 9 0 always $@$ ( posedge clk or posedge clr) begin if $\mathrm { \Phi _ { c l r = - 1 } }$ ) clkdiv ${ < } { = } 0$ ; else clkdiv $< = { \mathrm { c l k d i v } } + 1$ ; end assign ${ \bf s } =$ clkdiv[19]; always $\textcircled { a } \left( ^ { * } \right)$ begin $\mathtt { a n } = 2 ^ { \rVert } \mathtt { b } 0 0 ;$ $\mathrm { { a n } [ s ] = 1 }$ ; end; always $\textcircled { a } \left( ^ { * } \right)$ case(s) 0:digit $\mathbf { \partial } = \mathbf { x } [ 3 { : } 0 ]$ ; 1:digi $\mathbf { t } = \mathbf { x } [ 7 { : } 4 ]$ ;

default:digit $\mathbf { \partial } = \mathbf { x } [ 3 { : } 0 ]$ ; endcase always $\textcircled { a } \left( ^ { * } \right)$ case(digit) 0:a_to_g =7'b1111110; 1:a_to_ $\mathbf { g } = 7 \mathbf { \ " b } 0 1 1 0 0 0 0$ ; 2:a_to_ $\mathbf { g } = 7 \mathbf { b } 1 1 0 1 1 0 1$ ; 3:a_to_ $\mathbf { g } = 7 \mathbf { \hat { b } } 1 1 1 0 0 1$ ; 4:a_to_ $\mathbf { g } = 7 \mathbf { \ " b } 0 1 1 0 0 1 1$ ; 5:a_to_g $=$ 7'b1011011; 6:a_to_g $=$ 7'b1011111; 7:a_to_g $=$ 7'b1110000; 8:a_to_g $=$ 7'b1111111; 9:a_to_g $=$ 7'b1111011; 'hA:a_to_g $=$ 7'b1110111; 'hB:a_to_g $=$ 7'b0011111; 'hC:a_to_g $=$ 7'b1001110; 'hD:a_to_g $=$ 7'b0111101; 'hE:a_to_g $=$ 7'b1001111; 'hF:a_to_g $=$ 7'b1000111; default:a_to_ $\mathbf { g } =$ 7'b1111110; //0 endcase

endmodule

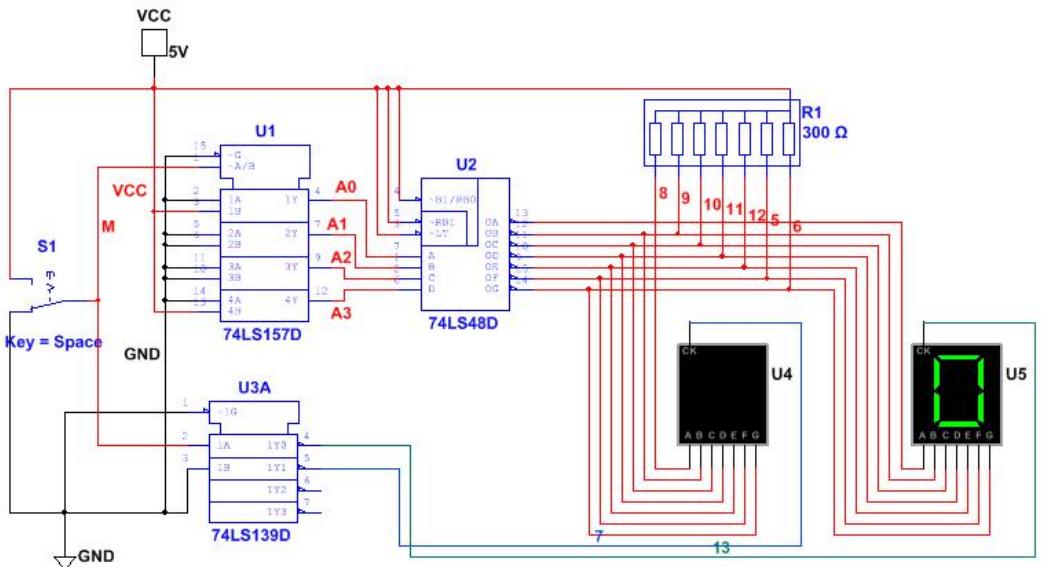

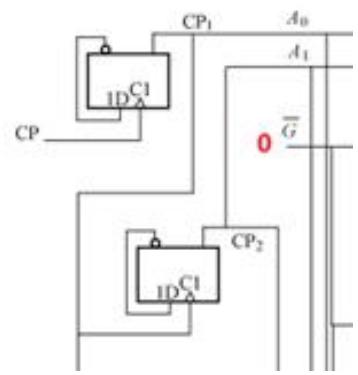

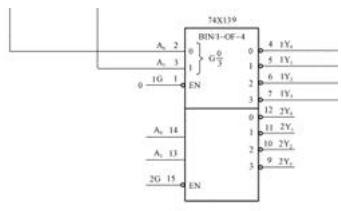

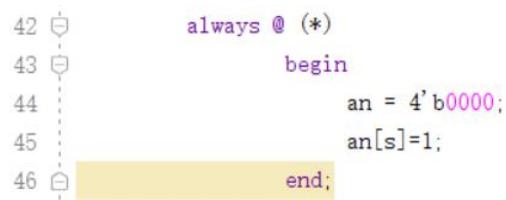

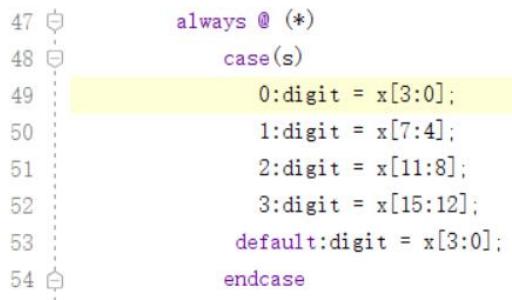

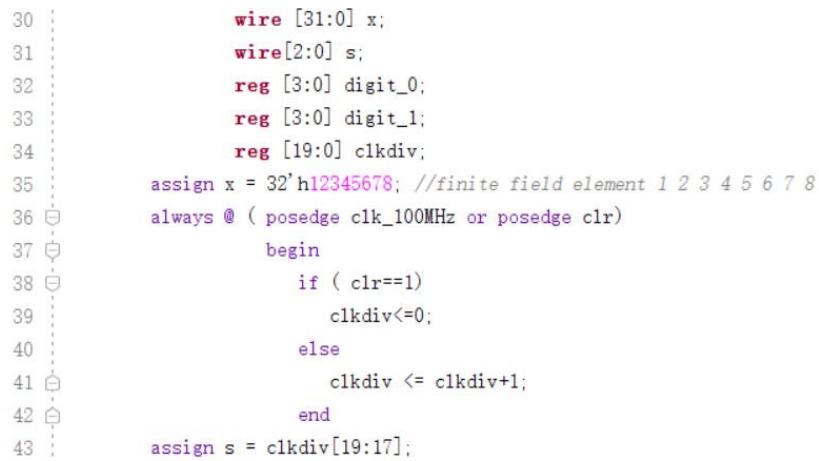

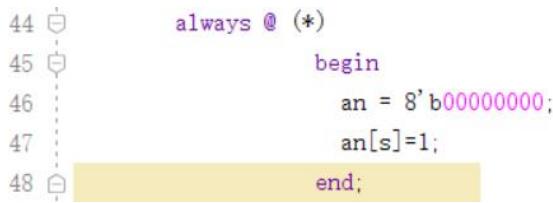

在 VIVADO 环境下 Verilog-HDL 程序的截图如图 36、图 37、图 38、图 39、图 40 所示。为了便于理解程序,同时表明了与图 26 所示原理图的对应关系。

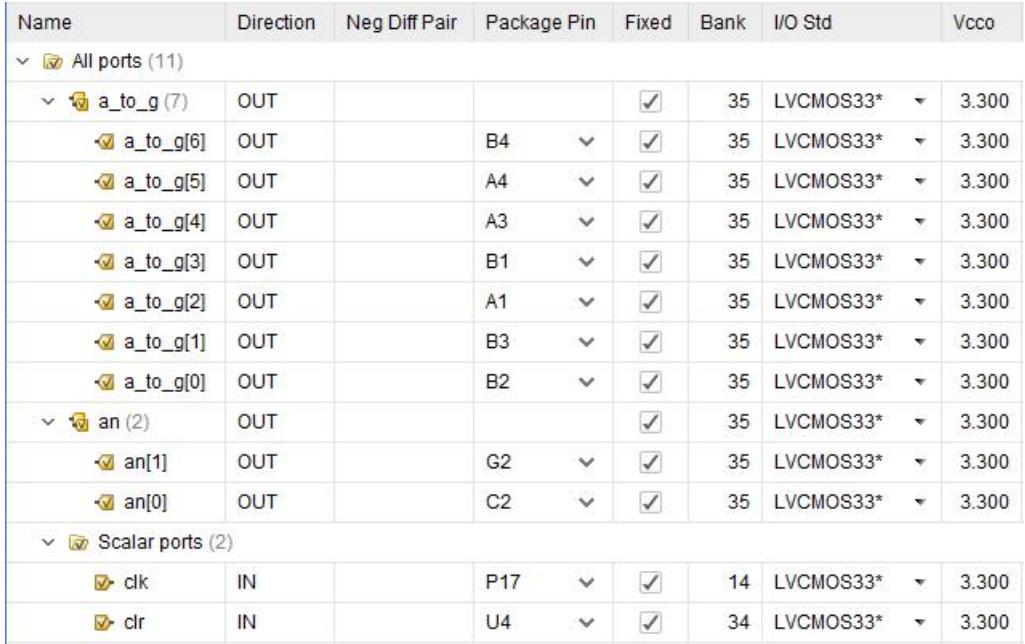

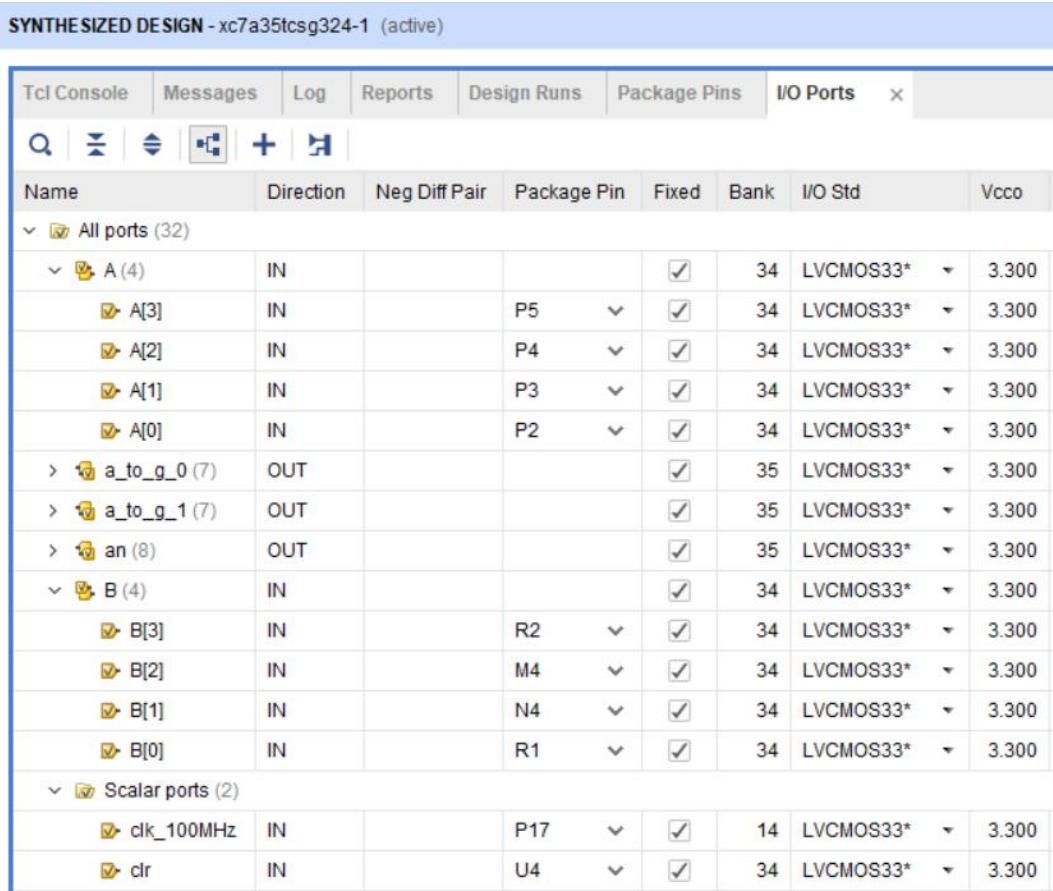

input clk,output reg[6:0]a_to_goutput reg [1:0]an约束如图 41 所示:

图 36 端口信号

图 37 计数器(产生 $\mathrm { C P _ { 1 } }$ 信号)(与图 26对应)

图38 1 线-2 线二进制译码器(74X139 芯片)(与图 26 对应),输出高电平有效

图 39 二选一数据选择器(通道数为 4 根线)(74X157 芯片)(与图 26对应)

图 40 显示译码器(74X48 芯片)(与图 26对应)

图 41 约束

下载验证如图 42 所示:

图 42 2 位数码管动态显示域元素 9、0

6.6 设计4 位数码管静态、动态显示电路

(1)设计 4位共阴数码管静态显示电路,显示四个域元素 1、2、3、4。使用 4 个七段显示译码器74LS48、4 个共阴数码管,在 Multisim12 软件环境下搭接电路,验证设计。

解:所谓静态显示,就是每个数码管的输入信号来自自己对应的那个七段显示译码器芯片的输出。

即一个数码管对应一个七段显示译码器。电路如图 43 所示。

图 43 静态显示域元素1、2、3、4 (共阴数码管)

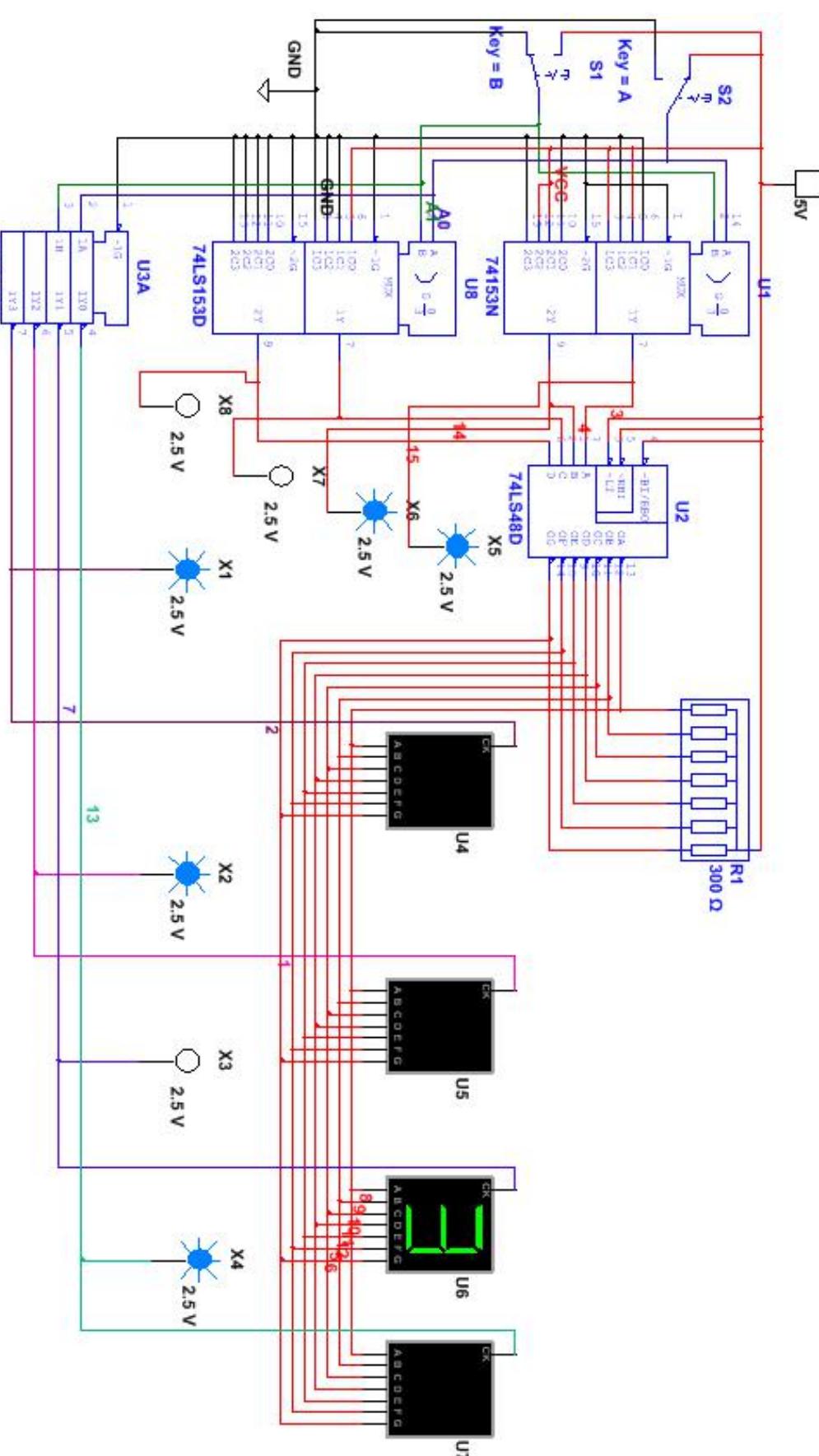

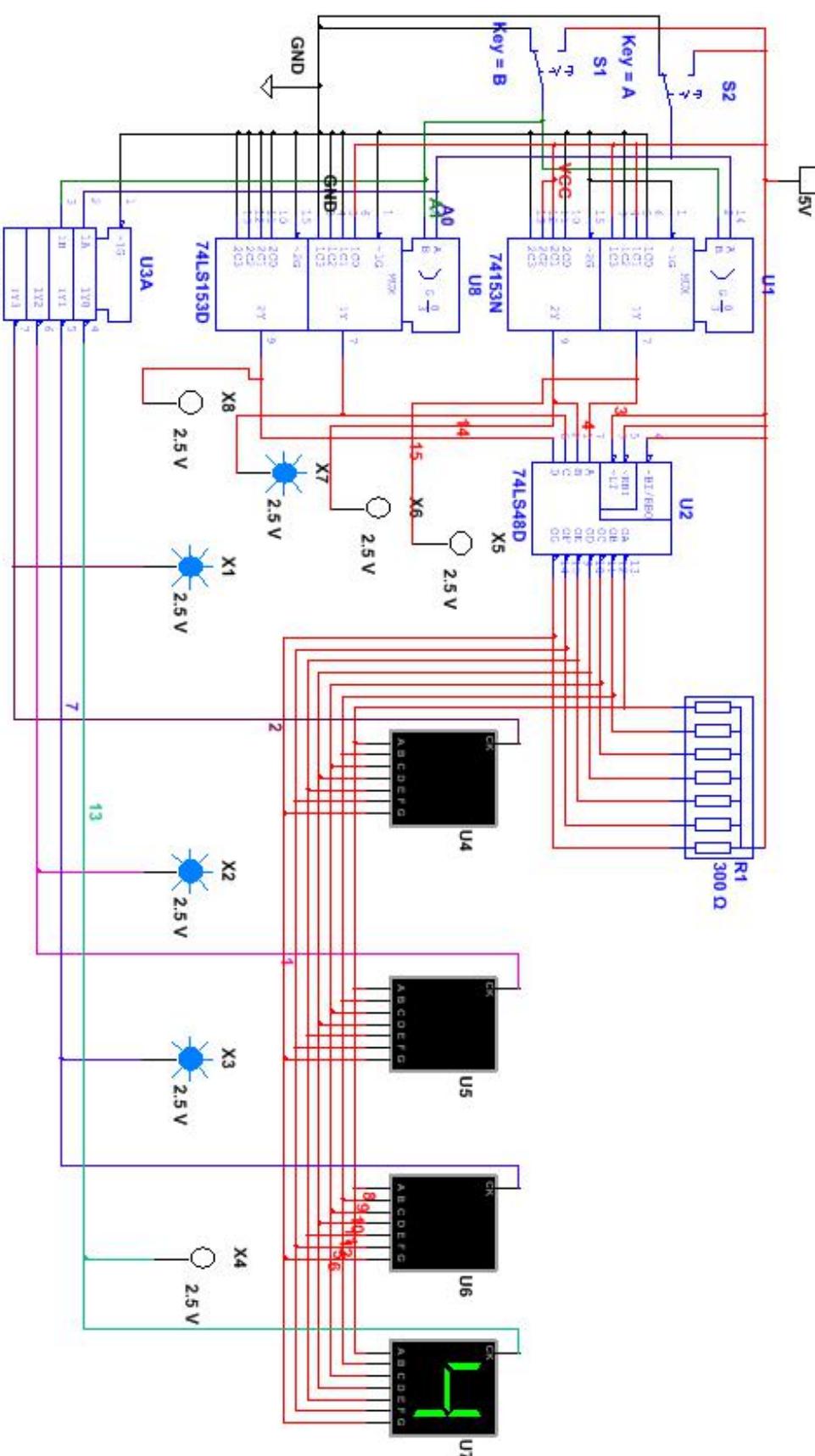

(2)设计 4 位共阴数码管动态显示电路,显示四个域元素 1、2、3、4。使用数据选择器 MUX、二进制译码器、1 个七段显示译码器 74LS48、4 个共阴数码管,在 Multisim12 软件环境下搭接电路,验证设计。

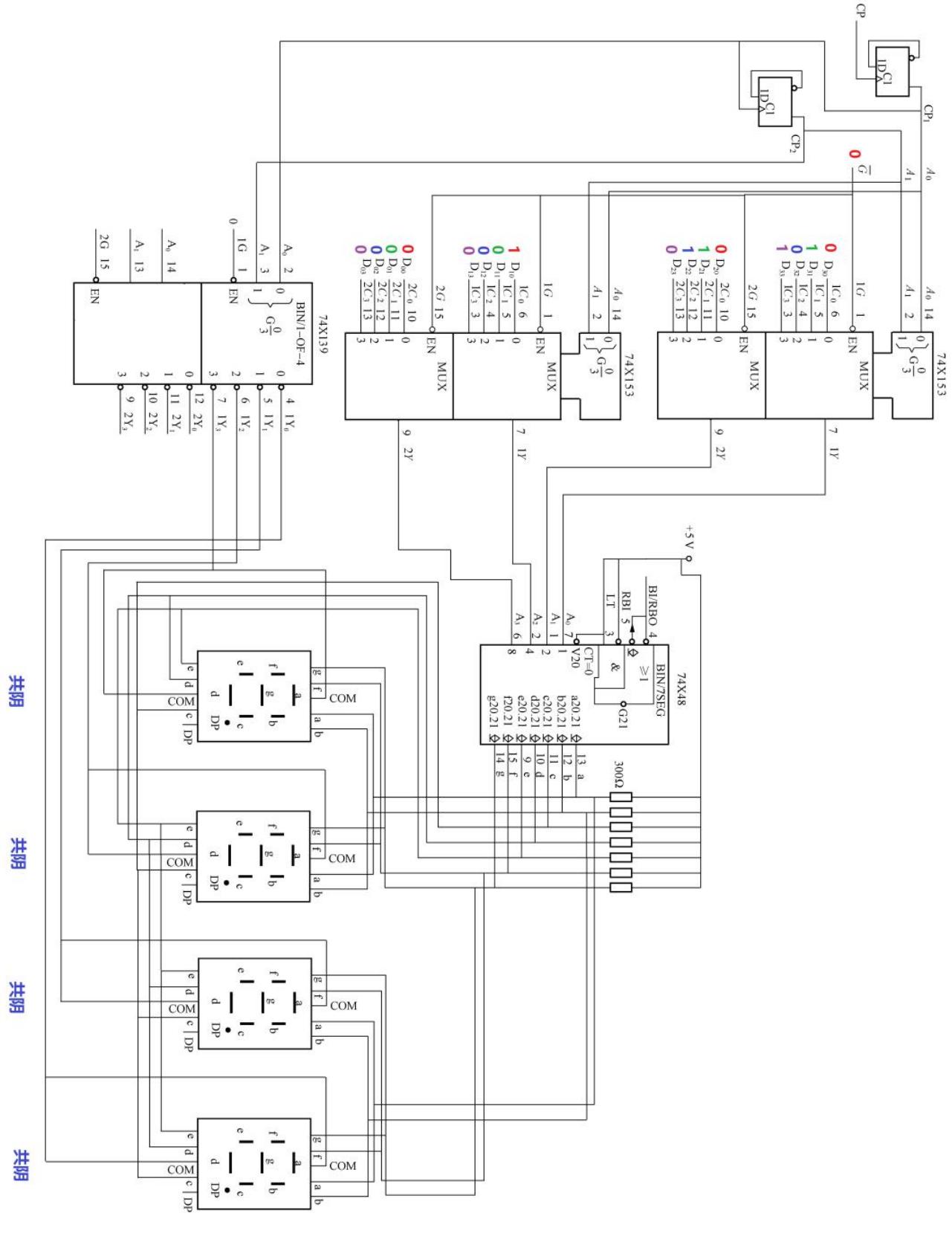

解:所谓动态显示,就是所有的数码管的输入信号全部来自一个七段显示译码器芯片的输出。数据选择器 MUX 要使用四选一数据选择器,通道数为 4 根线,扩展电路如图 44所示。4位共阴数码管动态显示的原理图电路如图 45 所示。Multisim12 软件仿真4 位共阴数码管动态显示电路如图46、图 47、图 48、图 49 所示。

图 44 四选一数据选择器,通道数为4 根线

图 45 动态显示域元素1、2、3、4 (共阴数码管)

图 46 左侧第一个数码管显示域元素 1(共阴数码管)( Multisim12软件仿真)

图 47 左侧第二个数码管显示域元素2(共阴数码管)( Multisim12 软件仿真)

图 48 左侧第三个数码管显示域元素 3(共阴数码管)( Multisim12软件仿真)

图 49 左侧第四个数码管显示域元素 4(共阴数码管)( Multisim12软件仿真)

(3)在 EGO1 口袋实验板上设计 4 位共阴数码管动态显示电路,显示四个域元素 1、2、3、4。在VIVADO 环境下输入 Verilog-HDL 程序,经过仿真、综合、实现、编写约束文件,下载到 EGO1口袋实验板的 FPGA 芯片 XC7A35TCSG324-1 中,验证正确性。要求使用 EGO1 口袋实验板的最左侧的 4 个数码管。

解:源程序如下:

7seg1234(

t clk,

t clr,

ut reg [6:0] a_to_g,

ut reg [3:0] an wire [15:0] x; wire[1:0] s; reg [3:0] digit; reg [19:0] clkdiv;

assign x=16'h1234;//finite field element 1 2 3 4

always $@$ ( posedge clk or posedge clr) begin if ( $\mathrm { \Phi _ { c l r = - 1 } }$ ) clkdiv ${ < } { = } 0$ ; else clkdiv $< =$ clkdiv+1; end

assign ${ \bf s } =$ clkdiv[19:18];

always $\textcircled { a } \left( ^ { * } \right)$ begin $\mathrm { a n } = 4 \mathrm { b } 0 0 0 0 \mathrm { ; }$ ; $\mathrm { { a n } [ s ] = 1 }$ ; end;

always $\textcircled { a } \left( ^ { * } \right)$ case(s) 0:digit $\mathbf { \partial } = \mathbf { x } [ 3 { : } 0 ]$ ; 1:digit $\mathbf { \tau } = \mathbf { x } [ 7 : 4 ]$ ; 2:digit $= \mathbf { x } [ 1 1 { : } 8 ]$ ; 3: $\mathrm { { i i g i t } } = \mathbf { x } [ 1 5 { : } 1 2 ]$ ; default:digit $\mathbf { \partial } = \mathbf { x } [ 3 { : } 0 ]$ ; endcase

always $\textcircled { a } \left( ^ { * } \right)$ case(digit) 0:a_to_ ${ \bf g } =$ 7'b1111110; 1:a_to_ $\mathbf { g } = 7 \mathbf { b } 0 1 1 0 0 0 0$ ; 2:a_to_ $\mathbf { g } = 7 \mathbf { b } 1 1 0 1 1 0 1$ ; 3:a_to $\scriptstyle \mathbf { g } = 7 \mathbf { b } 1 1 1 1 0 0 1$ ; 4:a_to_g $=$ 7'b0110011; 5:a_to_ $\mathbf { g } = 7 \mathbf { b } 1 0 1 1 0 1 1$ ; 6:a_to_g $=$ 7'b1011111; 7:a_to_g $=$ 7'b1110000; 8:a_to_g $=$ 7'b1111111; 9:a_to_g $=$ 7'b1111011; 'hA:a_to_g $=$ 7'b1110111; 'hB:a_to_g $=$ 7'b0011111; 'hC:a_to_ $\mathbf { g } = 7 \mathbf { b } 1 0 0 1 1 1 0$ ; 'hD:a_to_g $=$ 7'b0111101; 'hE:a_to_g $=$ 7'b1001111; 'hF:a_to_ $\mathbf { g } = 7 \mathbf { b } 1 0 0 0 1 1 1$ ; default:a_to_ $\mathbf { g } =$ 7'b1111110; //0 endcase

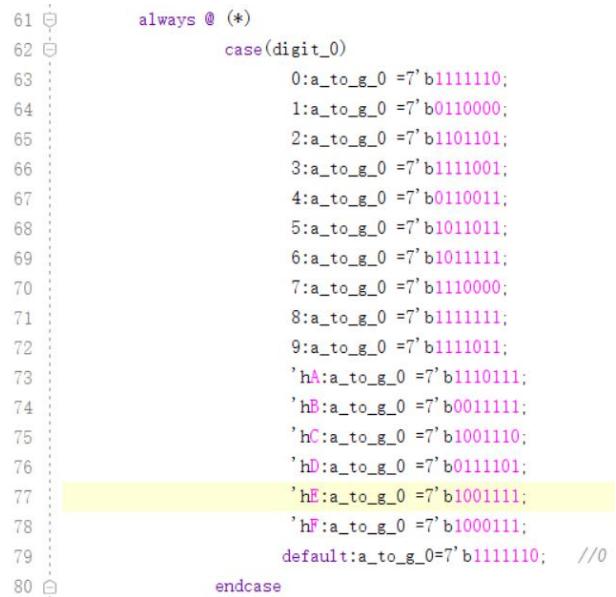

在 VIVADO 环境下 Verilog-HDL 程序的截图如图 50、图 51、图 52、图 53、图 54 所示。为了便于理解程序,同时表明了与图 45 所示原理图的对应关系。

reg[3:0]digit;reg[19:0]clkdiv;$\scriptstyle x = 1 6 ^ { \prime }$ $\mathsf { c l r } \mathsf { \Pi } ^ { \mathsf { c l } }$ clkdiv $\scriptstyle = 0$ clkdiv $\Leftarrow =$ clkdiv+1;assign s $=$ c1kdiv[19:18]:

图 50 端口信号

图51 计数器(产生 $\mathrm { C P } _ { 2 }$ 信号、 $\mathrm { C P _ { 1 } }$ 信号)(与图45对应)

图 52 2 线-4 线二进制译码器(74X139 芯片)(与图 45 对应),输出高电平有效

图 53 四选一数据选择器(通道数为 4 根线)(74X153 芯片)(与图 45对应)

图 54 显示译码器(74X48 芯片)(与图 45对应)

图 55 约束

下载验证如图 56 所示:

图 56 4 位数码管动态显示域元素 1、2、3、4

6.7 设计8 位数码管动态显示电路

(1)设计 8 位共阴数码管动态显示电路,显示八个域元素 1、2、3、4、5、6、7、8。使用数据选择器 MUX、二进制译码器、1 个七段显示译码器 74LS48、8 个共阴数码管,在 Multisim12 软件环境下搭接电路,验证设计。

解:所谓动态显示,就是所有的数码管的输入信号全部来自一个七段显示译码器芯片的输出。数据选择器 MUX 要使用八选一数据选择器,通道数为 4 根线,数据选择器 MUX 的扩展电路如图57 所示。Multisim12 软件仿真 8 位共阴数码管动态显示电路如图 58、图 59 所示。

图 57 八选一数据选择器,通道数为4 根线

图 58 左侧第一个数码管显示域元素1(共阴数码管)( Multisim12 软件仿真)

图 59 左侧第二个数码管显示域元素 2 (共阴数码管)( Multisim12软件仿真)

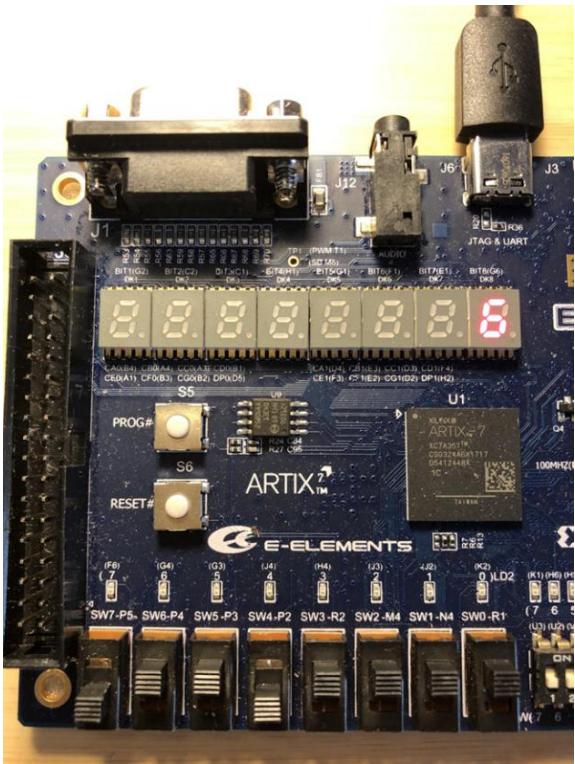

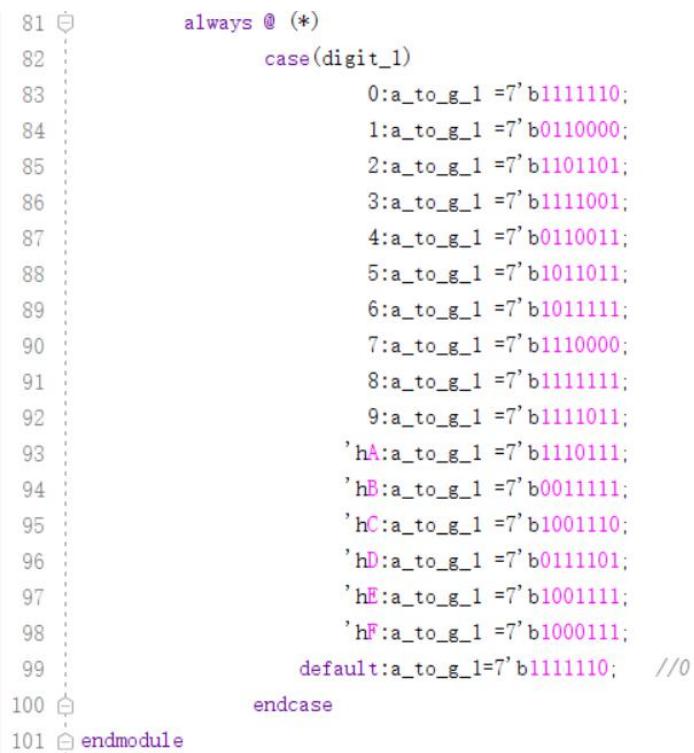

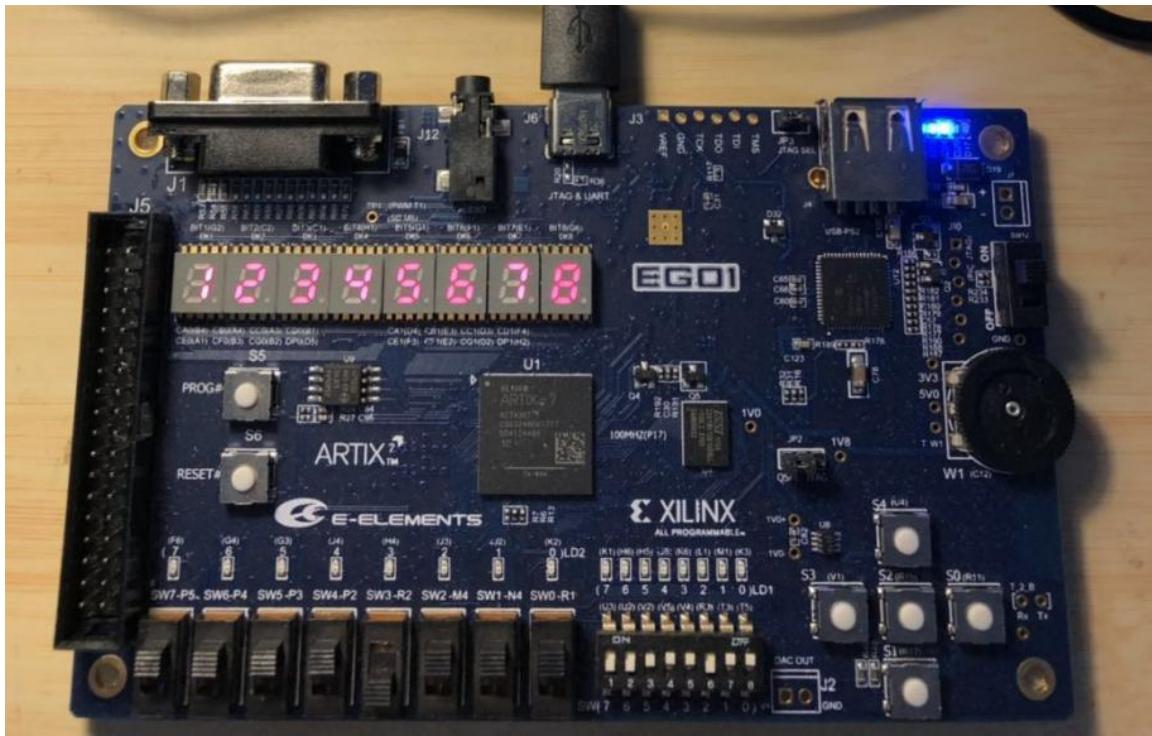

(2) 在 EGO1 口袋实验板上设计 8 位共阴数码管动态显示电路,显示八个域元素 1、2、3、4、5、6、7、8。在 VIVADO 环境下输入 Verilog-HDL 程序,经过仿真、综合、实现、编写约束文件,下载到 EGO1 口袋实验板的 FPGA 芯片 XC7A35TCSG324-1 中,验证正确性。

解:设计源文件:

x7seg12345678(

put clk_100MHz,

put clr,

tput reg [7:0] an,

tput reg [6:0] a_to_g_0,

tput reg [6:0] a_to_g_1 wire [31:0] x; wire[2:0] s; reg [3:0] digit_0; reg [3:0] digit_1; reg [19:0] clkdiv; assign $\mathbf { x } = 3 2 7 \mathrm { h } 1 2 3 4 5 6 7 8$ ; //finite field element 1 2 3 4 5 6 7 8 always $@$ ( posedge clk_100MHz or posedge clr) begin if ( $\mathrm { \Phi _ { c l r = - 1 } }$ ) clkdiv ${ < } = 0$ ; else clkdiv $< =$ clkdiv+1; end assign ${ \bf s } =$ clkdiv[19:17]; always $\textcircled { a } \left( ^ { * } \right)$ begin $\mathbf { a n } = 8 ^ { \prime } \mathbf { b } 0 0 0 0 0 0 0 0 0 0 \ ;$ ; $\mathbf { a n } [ \mathbf { s } ] { = } 1$ ; end; always $\textcircled { a } \left( ^ { * } \right)$ case(s) 0:digit_ $0 = \mathbf { x } [ 3 { : } 0 ]$ ; 1:digit_ $\mathbf { 0 } = \mathbf { x } [ 7 { : } 4 ]$ ; 2:digit_ $0 = \mathbf { x } [ 1 1 { : } 8 ]$ ; 3:digit_ $0 = \mathbf { x } [ 1 5 { : } 1 2 ]$ ; 4:digit_ $\mathbf { \tau } _ { 1 } = \mathbf { x } [ 1 9 { : } 1 6 ]$ ; 5:digit_ $\mathbf { \underline { { 1 } } } = \mathbf { x } [ 2 3 { : } 2 0 ]$ ; 6:digit_ $\mathbf { 1 } = \mathbf { x } [ 2 7 { : } 2 4 ]$ ; 7:digit_ $\mathbf { \varepsilon } _ { 1 } = \mathbf { x } [ 3 1 { : } 2 8 ]$ ; default:digit_ $0 = \mathbf { x } [ 3 { : } 0 ]$ ; endcase always $\textcircled { a } \left( ^ { * } \right)$ case(digit_0) 0:a_to_g_ $0 =$ 7'b1111110; 1:a_to_g $\mathrm { \Omega _ { 0 } } = 7 \mathrm { ‰ }$ ; 2:a_to_g_ $_ { 0 } { = } 7 \mathbf { b } 1 1 0 1 1 0 1$ ; 3:a_to_g_ $0 =$ 7'b1111001;

4:a_to_g_ $0 =$ 7'b0110011; 5:a_to_g_ $0 =$ 7'b1011011; 6:a_to_g_ $0 =$ 7'b1011111; 7:a_to_g_ $0 =$ 7'b1110000; 8:a_to_g_ $0 =$ 7'b1111111; 9:a_to_g_ $0 =$ 7'b1111011; 'hA:a_to_g_ $0 =$ 7'b1110111; 'hB:a_to_g $\scriptstyle 0 = 7 \mathrm { { b } } 0 0 1 1 1 1 1$ ; 'hC:a_to_g_ $\begin{array} { r } { 0 = 7 \mathrm { { b } } 1 0 0 1 1 1 0 } \end{array}$ ; 'hD:a_to_g $\scriptstyle 0 = 7 ^ { \prime } b 0 1 1 1 1 0 1$ ; 'hE:a_to_g $\scriptstyle \underline { { 0 } } = 7 ^ { \eta } 1 0 0 1 1 1 1$ ; 'hF:a_to_g_ $0 { = } 7 \mathrm { b } 1 0 0 0 1 1 1$ ; default:a_to_g_ $0 =$ 7'b1111110; //0 endcase always $@$ (*) case(digit_1) 0:a_to_g_ $1 =$ 7'b1111110; 1:a_to $\mathrm { g } _ 1 = 7 5 0 1 1 0 0 0 0$ ; 2:a_to_ $\mathrm { \underline { { ~ g ~ } } } 1 = 7 \mathrm { \overline { { b } } } 1 1 0 1 1 0 1$ ; 3:a_to $\mathrm { \underline { { ~ g ~ } } } _ { - } 1 = 7 \mathrm { b } 1 1 1 1 0 0 1$ ; 4:a_to_g_1 $=$ 7'b0110011; 5:a_to_g_1 $=$ 7'b1011011; 6:a_to_g_ $_ { , } =$ 7'b1011111; 7:a_to_g_1 $=$ 7'b1110000; 8:a_to_g_ $_ { , } =$ 7'b1111111; 9:a_to_g_1 $=$ 7'b1111011; 'hA:a_to_g_1 $=$ 7'b1110111; 'hB:a_to_g_1 $=$ 7'b0011111; 'hC:a_to_g_ $\mathbf { \tau } _ { 1 } = 7 \mathbf { \ ' } \mathbf { b } 1 0 0 1 1 1 0$ ; 'hD:a_to_ $\mathrm { \underline { { ~ \pi ~ } } } _ { - } 1 = 7 \mathrm { \cdot } 6 0 1 1 1 1 0 1$ ; 'hE:a_to_g_1 $=$ 7'b1001111; 'hF:a_to_ $\scriptstyle { \underline { { \mathbf { y } } } } _ { - } 1 = 7 ^ { \prime } { \overline { { \mathbf { b } } } } 1 0 0 0 1 1 1$ ; default:a_to_g_ $1 =$ 7'b1111110; //0 endcase

endmodule

在 VIVADO 环境下 Verilog-HDL 程序的截图如图 60、图 61、图 62、图 63、图 64、图 65 所示,同时表明了与某个逻辑模块的对应关系。

input c1k_100MHz,

图61 3 位二进制计数器(产生 $\mathrm { C P } _ { 3 }$ 信号、 $\mathrm { C P } _ { 2 }$ 信号、 $\mathrm { C P _ { 1 } }$ 信号)

图 62 3线-8线二进制译码器,输出高电平有效

图 63 八选一数据选择器(通道数为4 根线)

图 64 右边 4个数码管对应的显示译码器(与共阴数码管配套)

图 65 左边 4个数码管对应的显示译码器(与共阴数码管配套)

约束如图 66 所示:

图 66 约束

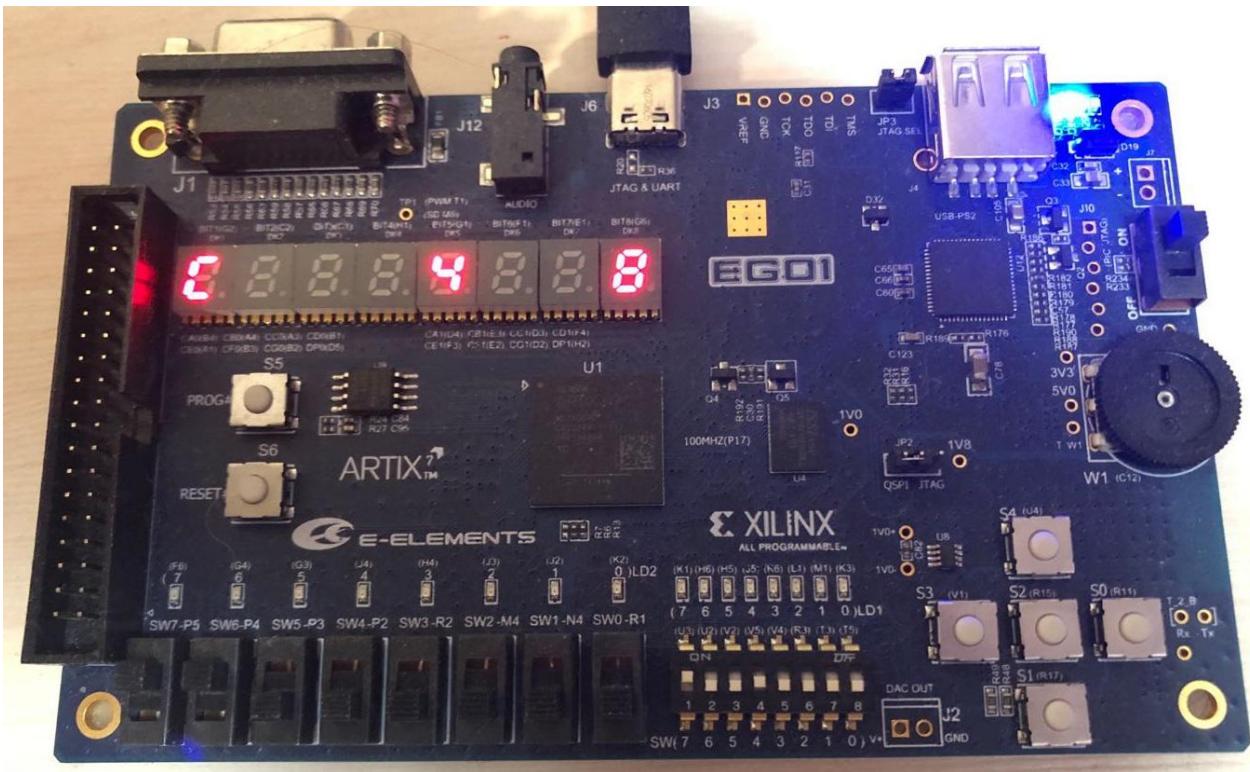

下载验证如图 67 所示:

图 67 8 位数码管动态显示域元素 1、2、3、4、5、6、7、8

6.8 在 EGO1 口袋实验板 8 位共阴数码管上显示 6.1 节4 位有限域乘法运算结果

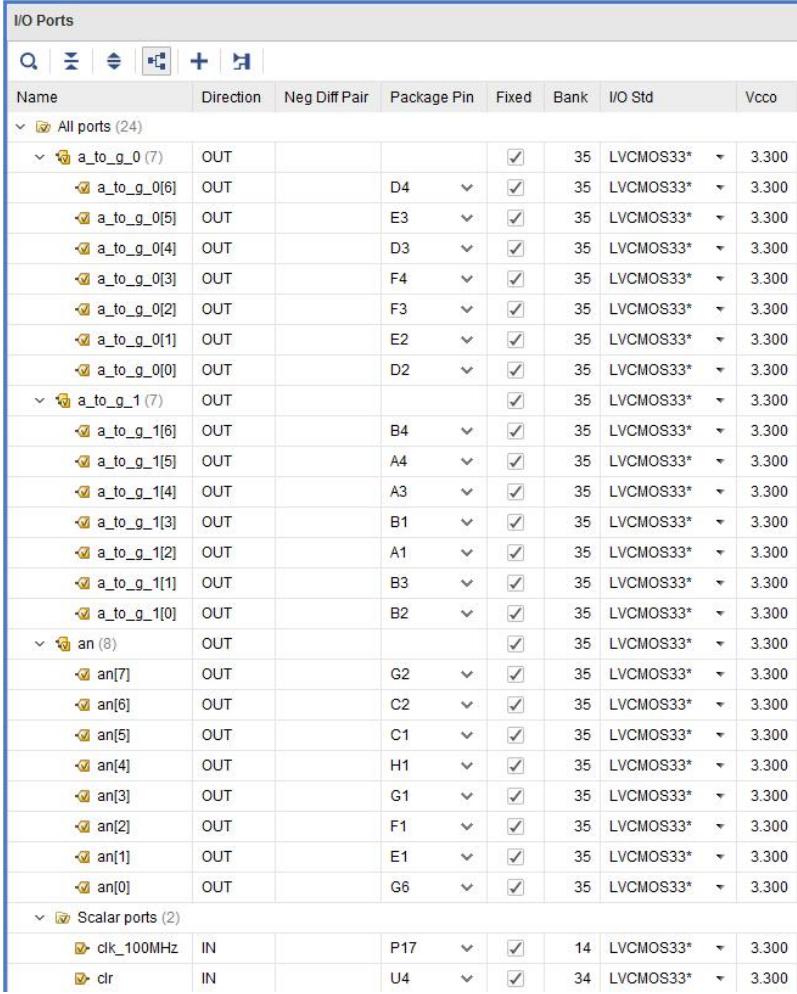

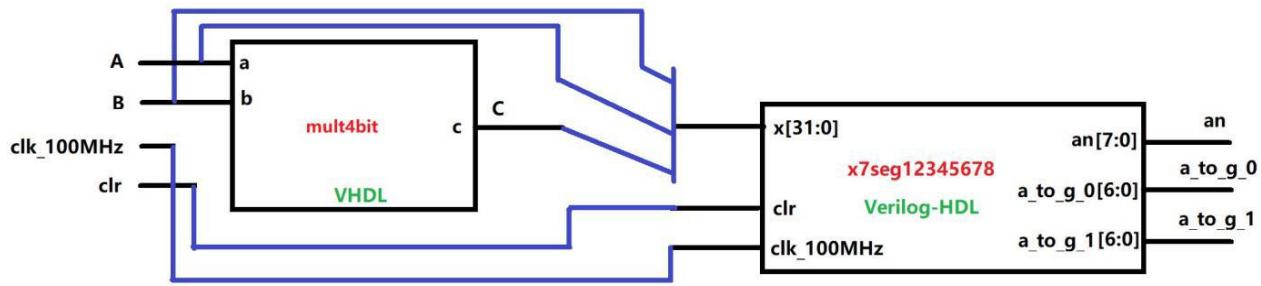

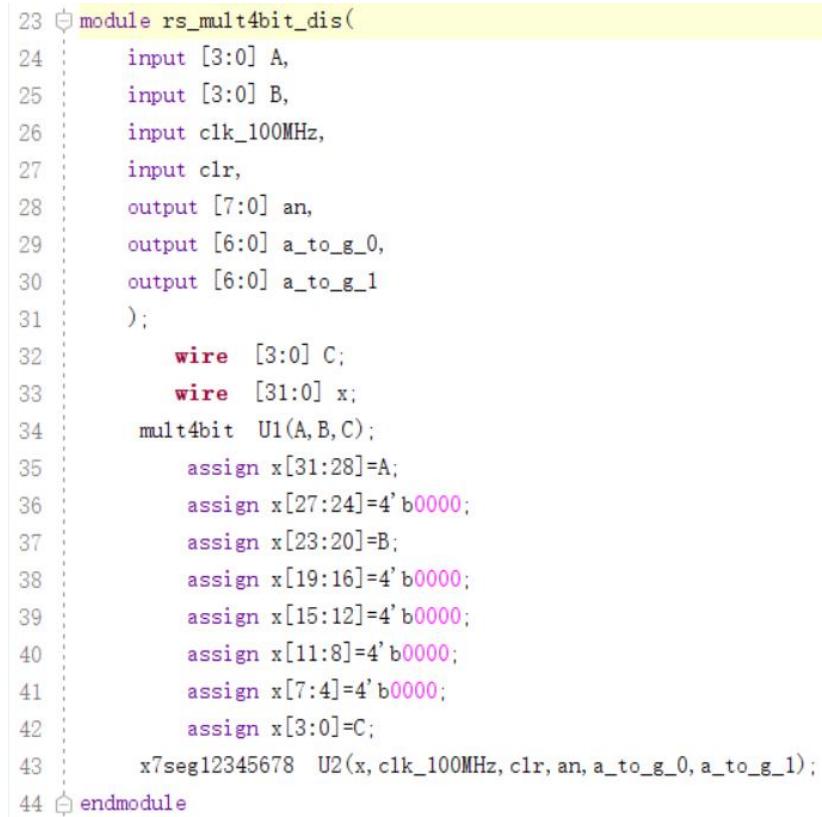

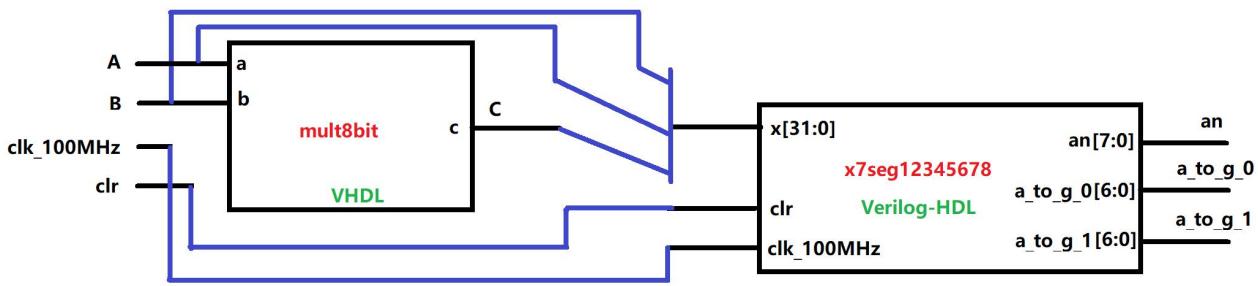

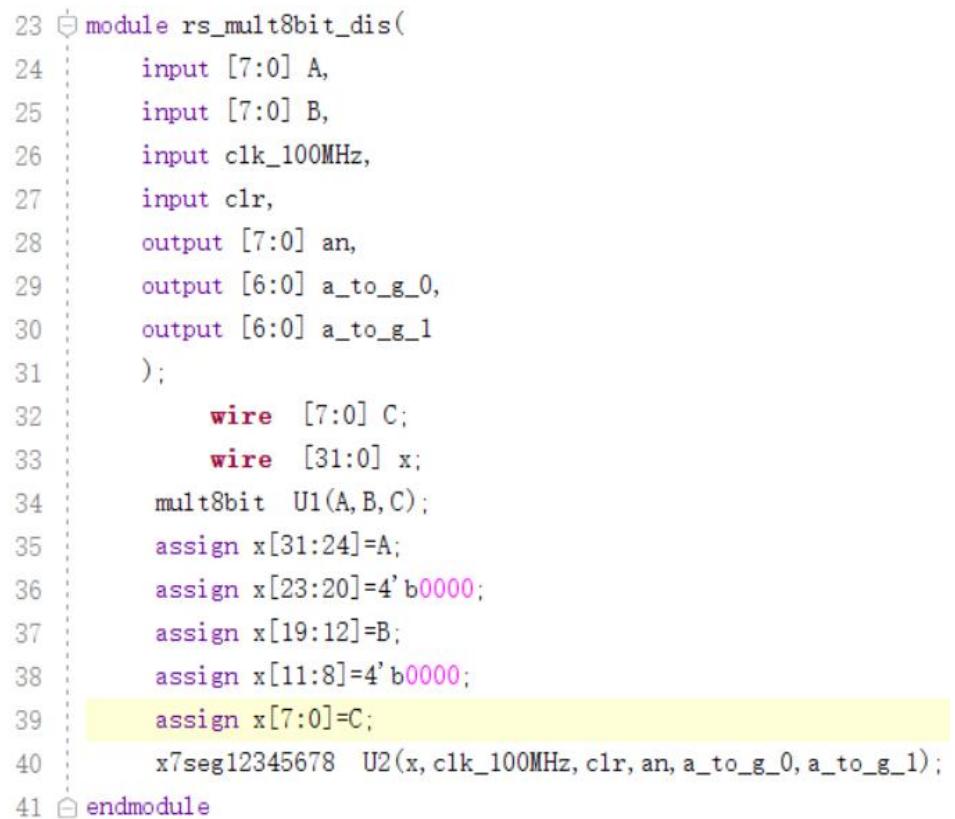

4 位乘法运算电路的对外输入、输出信号如图 68 所示,内部连接示意图如图 69 所示。顶层模块使用 Verilog-HDL 描述,其中例化了 mult4bit 和 x7seg12345678 两个元件,mult4bit 用 VHDL 描述,x7seg12345678 用 Verilog-HDL 描述。顶层源程序如图 70 所示。约束如图 71 所示。

图 68 输入信号、输出信号

图 69 4 位有限域乘法器和 8位数码管动态显示

图 70 与图 69 对应的顶层源程序(Verilog-HDL)

图 71 约束

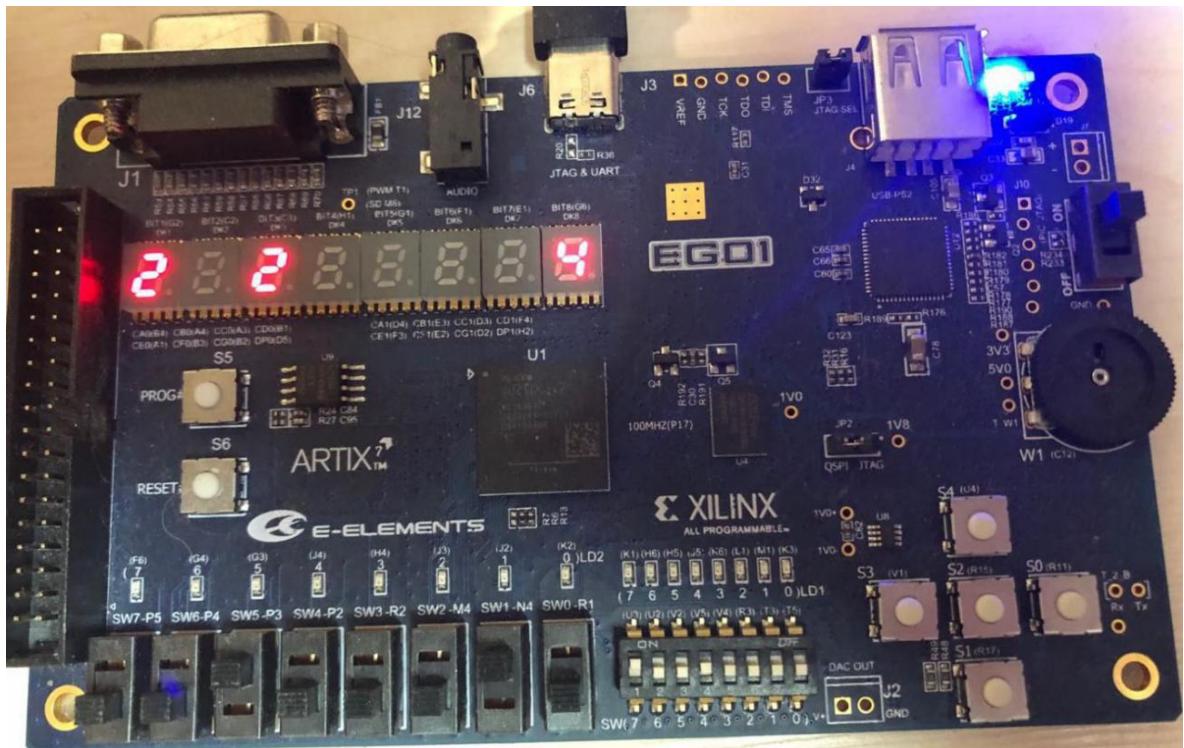

将 4 位乘法器下载到 EGO1 口袋实验板,左侧第一个数码管显示被乘数,左侧第三个数码管显示乘数,右侧第一个数码管显示乘积。给定被乘数 $0 0 1 0 \left( 2 _ { \mathrm { H } } \right)$ )、乘数 $0 0 1 0 \left( 2 _ { \mathrm { H } } \right)$ ),得乘积为 $0 1 0 0 ( 4 \mathrm { _ H } )$ ,

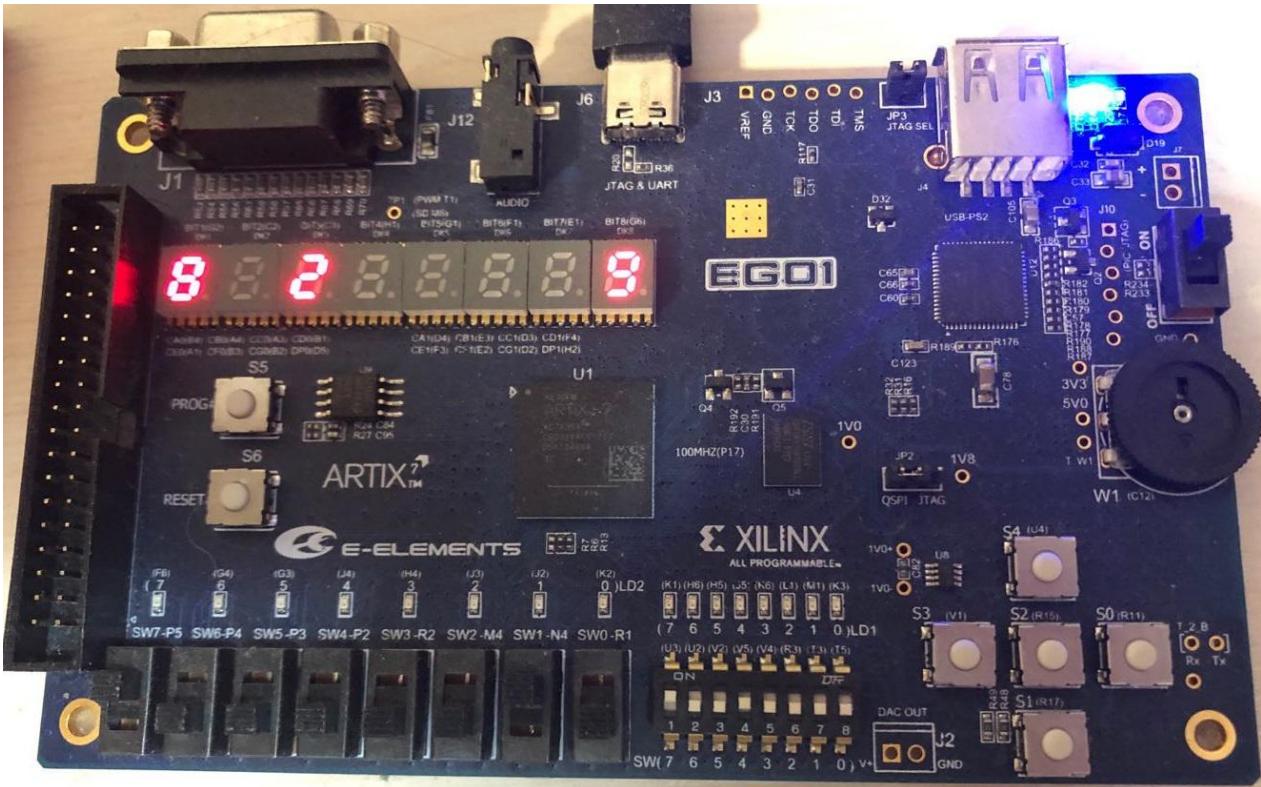

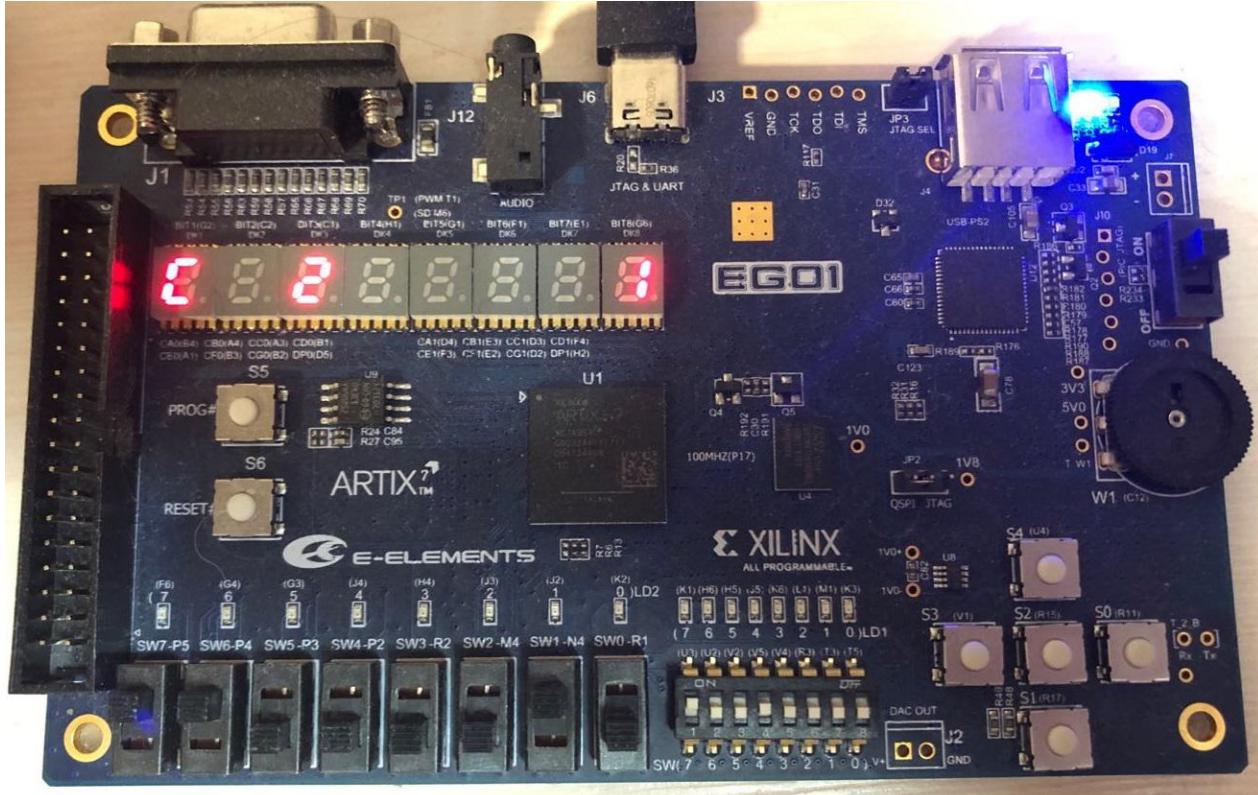

如图 72 所示。给定被乘数 1000( $8 _ { \mathrm { H } } .$ )、 乘数 0010( $2 _ { \mathrm { H } }$ ),得乘积为 1001( $\cdot 9 \mathrm { { H } , }$ ),如图 73 所示。给定被乘数 1100( $\cdot { \mathrm { c } } _ { \mathrm { H } } ,$ )、 乘数 0010( $\mathrm { . 2 _ { H } }$ ),得乘积为 0001( $1 \mathrm { _ H } \mathrm { } \mathrm { } \mathrm { } \cdot$ ),如图 74 所示。与理论计算、仿真结果一致。

图 72 被乘数 0010( $\cdot 2 \mathrm { _ H } \cdot$ )、 乘数 0010( $2 _ { \mathrm { H } } )$ ),得乘积为 0100( $\cdot 4 _ { \mathrm { H } } .$ )

图 73 被乘数 1000( $\smash { 8 _ { \mathrm { H } } } )$ )、 乘数 0010( $2 _ { \mathrm { H } } ,$ ),得乘积为 1001( $. 9 \mathrm { { H } }$ )

图 74 被乘数 1100( $\cdot \mathbf { c } _ { \mathrm { H } } ,$ )、 乘数 0010( $2 \mathrm { _ H } )$ ),得乘积为 0001( $1 _ { \mathrm { H } }$ )

6.9 在 EGO1 口袋实验板 8 位共阴数码管上显示 6.2 节的 8 位有限域运算乘法结果

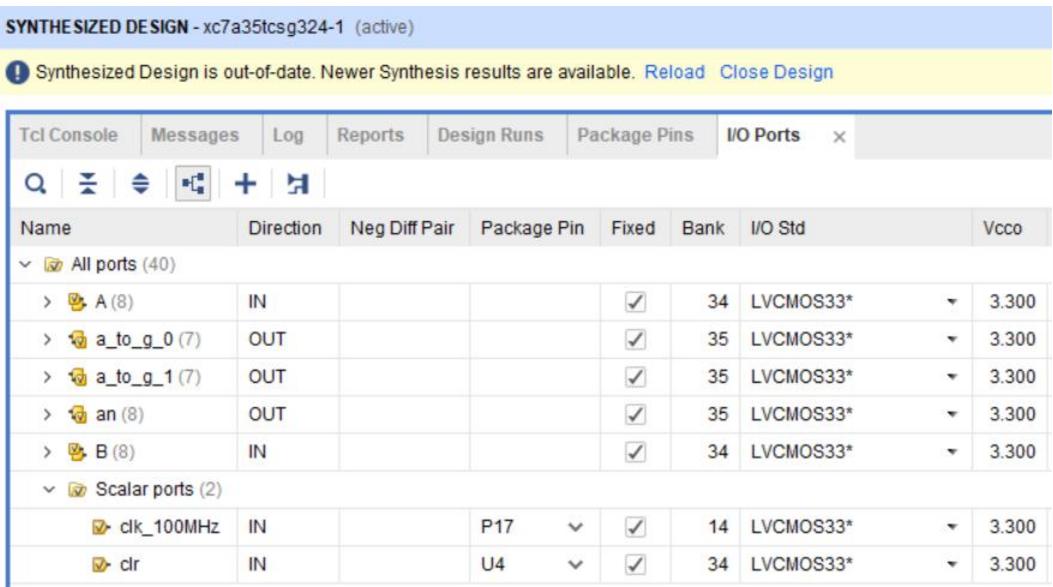

8 位乘法运算电路的对外输入、输出信号如图 75 所示,内部连接示意图如图 76 所示。顶层模块使用 Verilog-HDL 描述,其中例化了 mult8bit 和 x7seg12345678 两个元件,mult8bit 用 VHDL 描述,x7seg12345678 用 Verilog-HDL 描述。顶层源程序如图 77 所示。约束如图 78 所示。

图 75 输入信号、输出信号

图 76 8位有限域乘法器和 8位数码管动态显示电路

图 77 与图 76 对应的顶层源程序(Verilog-HDL)

图 78 约束

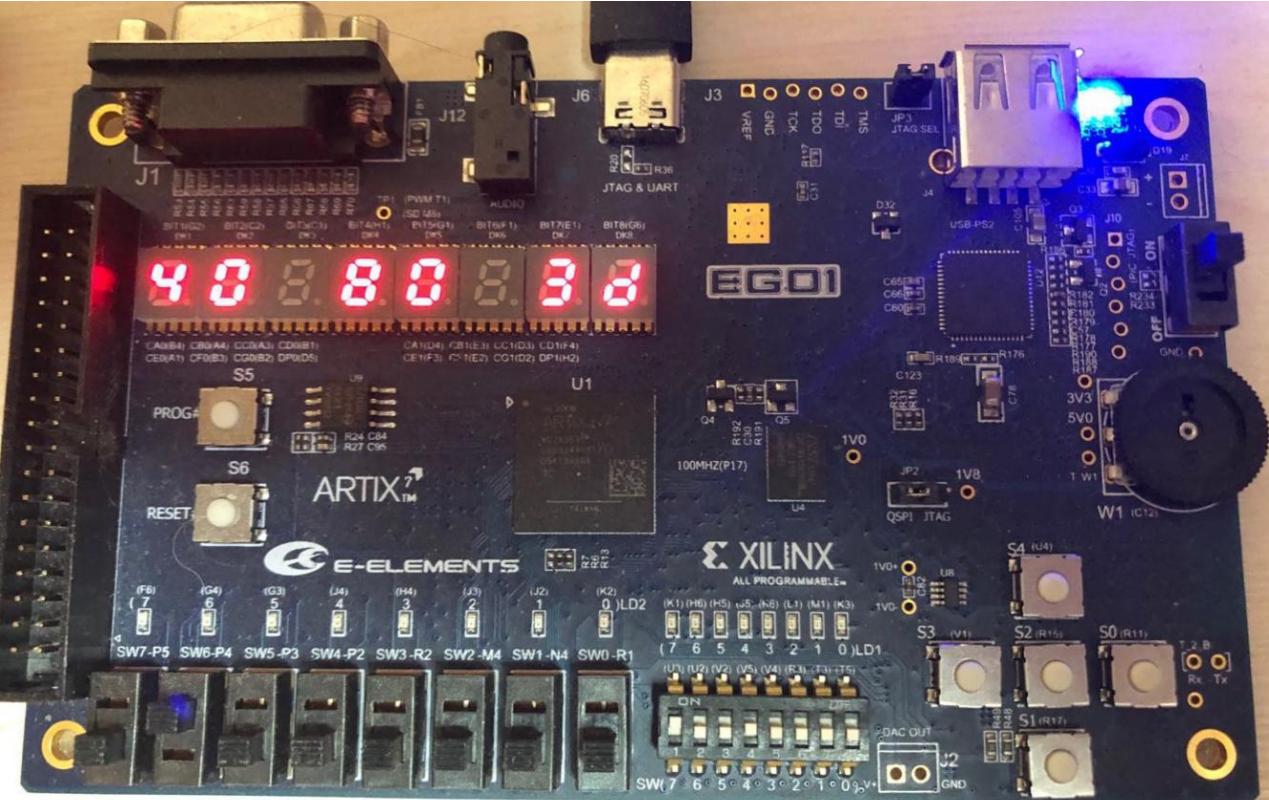

将 8 位乘法器下载到 EGO1 口袋实验板进行验证,左侧第一个、第二个数码管显示被乘数,左侧第四个、第五个数码管显示乘数,右侧第二个、第一个数码管显示乘积。给定被乘数 $0 1 0 0 0 0 0 0 0 ( 4 0 _ { \mathrm { H } } )$ 、乘数 10000000( $8 0 _ { \mathrm { H } }$ ),得乘积为 00111101( $3 \mathrm { d _ { H } }$ ),如图 79 所示,与理论计算、仿真结果一致。给定被乘数 10010001( $9 1 _ { \mathrm { H } } \mathrm { ~ , ~ }$ )、乘数 00100000( $2 0 _ { \mathrm { H } }$ ),得乘积为 01110100( $7 4 _ { \mathrm { H } } ,$ ),如图 80 所示,与理论计算、仿真结果一致。

图 79 被乘数 01000000( $4 0 _ { \mathrm { H } } \mathrm { , }$ )、乘数 10000000( $8 0 _ { \mathrm { H } } \mathrm { ~ . ~ }$ ),得乘积为 00111101( $3 \mathrm { d _ { H } }$ )

图 80 被乘数 10010001( $( 9 1 _ { \mathrm { H } }$ )、乘数 00100000( $2 0 _ { \mathrm { H } }$ ),得乘积为 01110100( $7 4 _ { \mathrm { H } }$ )

6.10 在 EGO1 口袋实验板 8 位共阴数码管上显示 6.3节的 RS编码

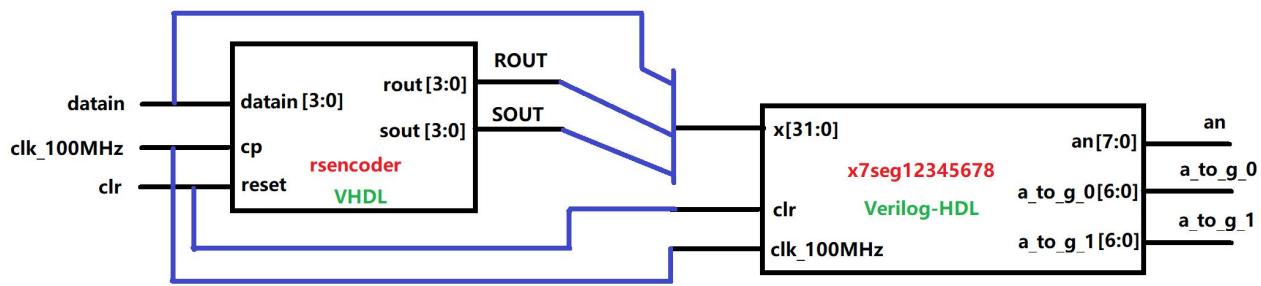

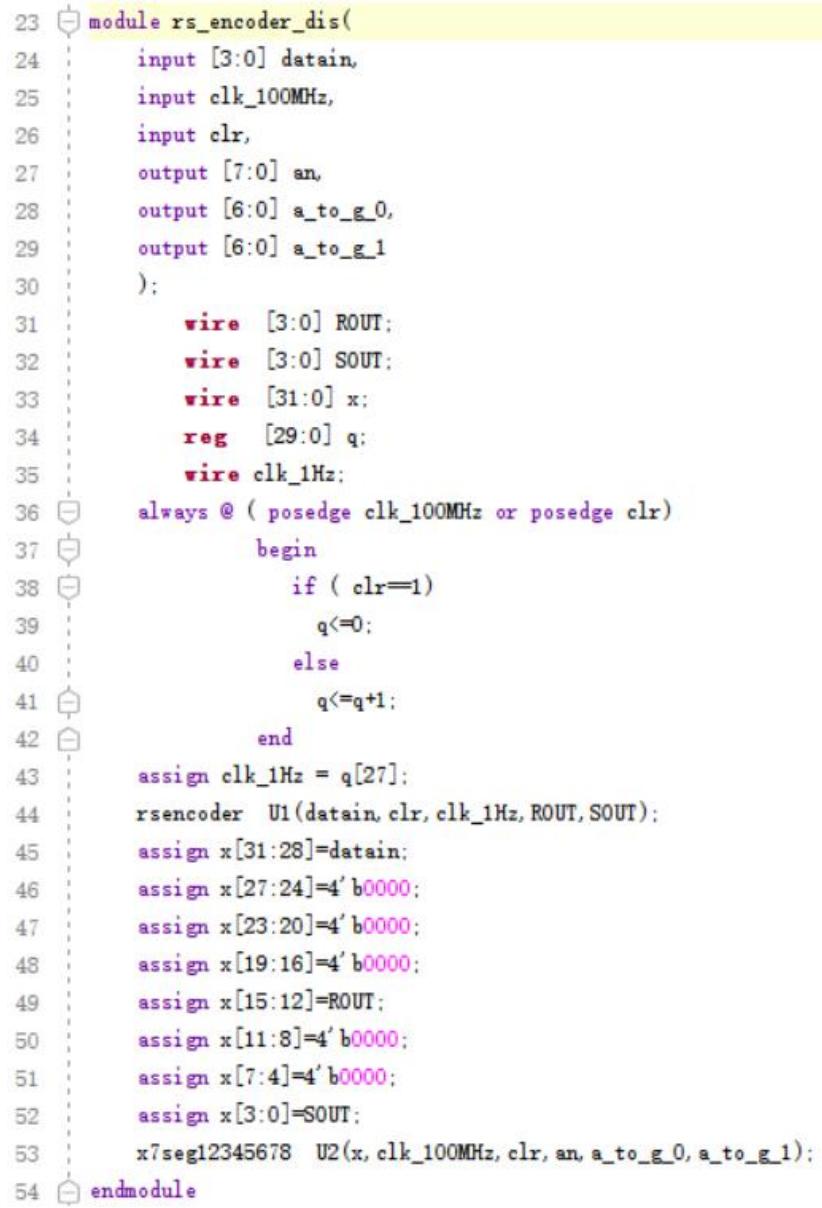

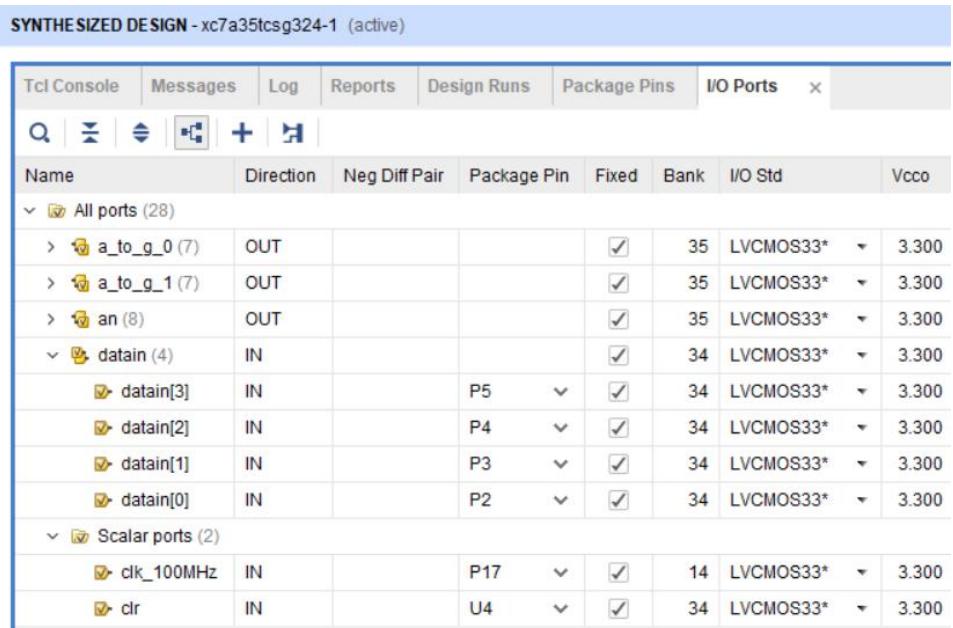

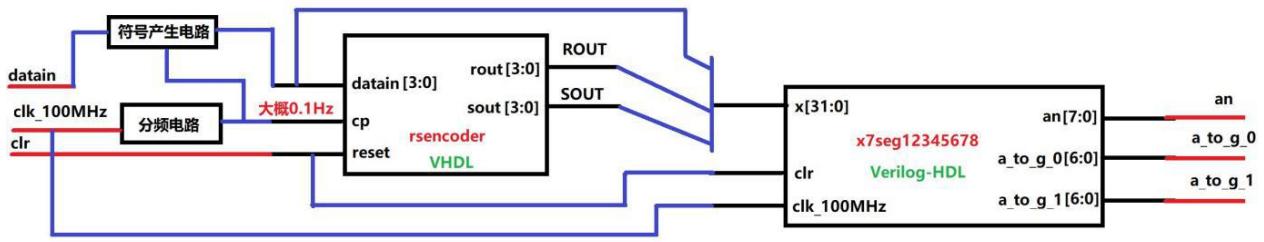

编码器的对外输入、输出信号如图 81 所示,内部连接示意图如图 82 所示。顶层模块使用Verilog-HDL 描述,其中例化了 rsencoder 和 x7seg12345678 两个元件,rsencoder 用 VHDL 描述,x7seg12345678 用 Verilog-HDL 描述。顶层源程序如图 83 所示。约束如图 84 所示。

图 81 输入信号、输出信号

图 82 内部连接示意图

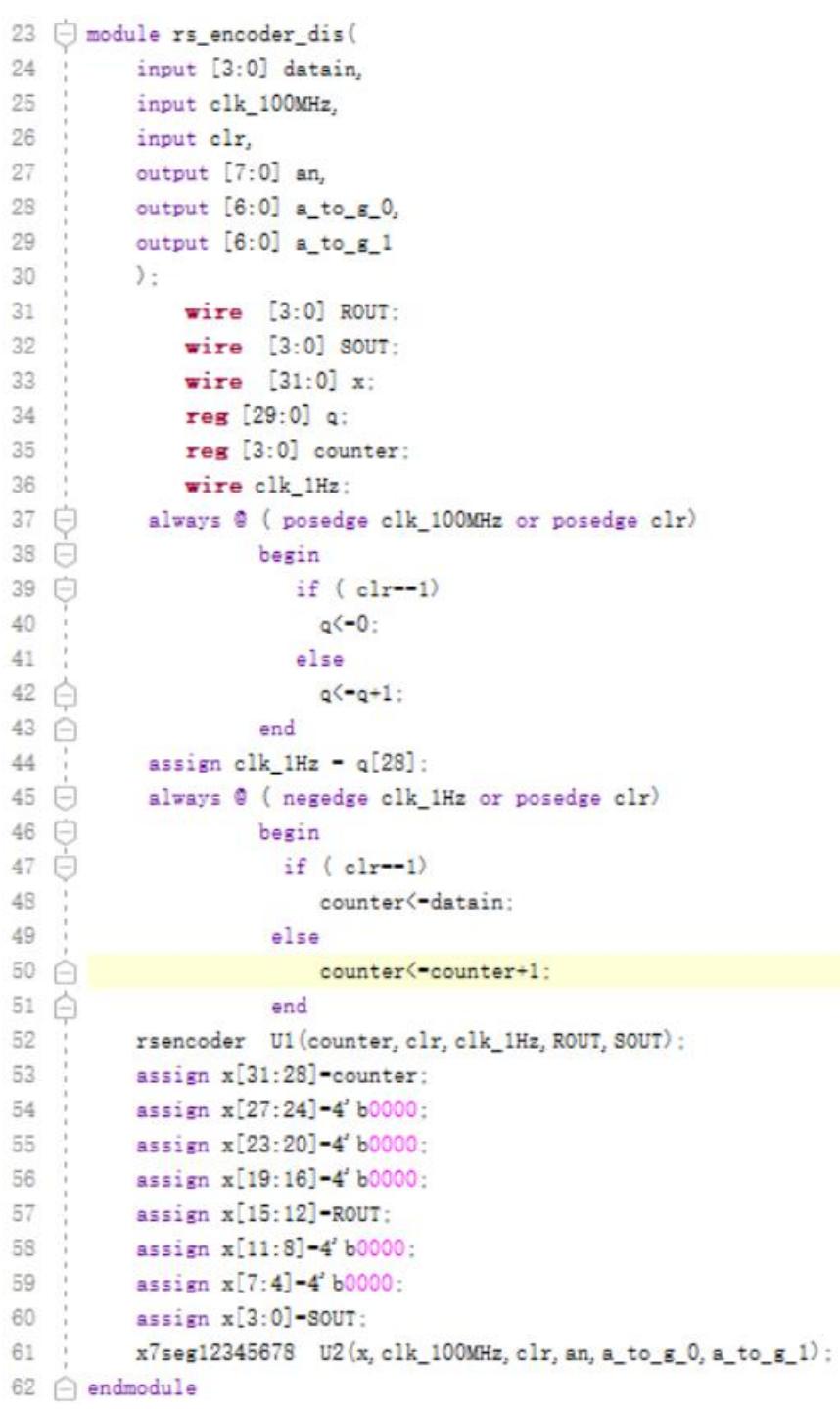

在图 83 所示的顶层源程序中,第 36 行到第 43 行描述了一个 30 位的二进制计数器,将 EGO1口袋实验板提供的 $1 0 0 \mathrm { M H z }$ 的时钟信号进行分频,在 q[27]得到频率比较低的近似为 $0 . 3 7 \mathrm { H z }$ (周期为2688 毫秒)的时钟信号,为模块 rsencoder 提供时钟信号,便于观察编码的结果。

图 83 与图 82 对应的顶层源程序(Verilog-HDL)

图 84 约束

将 RS 编码器下载到 EGO1 口袋实验板进行验证,如图 85所示,左侧第一个数码管连续显示信息符号,第 13 个时钟周期之后右侧第四个数码管显示校验符号 $R$ 、右侧第一个数码管显示校验符号S。信息符号由最左侧的 4 个大的拨码开关提供,拨码开关的位置在 13 个时钟周期内保持不变,输入十六进制数码 C,信息符号依次从输入端 datain 输入电路,最左侧的数码管显示每个时钟周期送入电路的信息符号(显示为十六进制数码),信息符号 $d _ { 1 3 }$ 、 $d _ { 1 2 }$ 、 $d _ { 1 1 }$ 、d10、d9、d8、d7、d6、d5、d4、d3、d2、 $d _ { 1 }$ 均给定 1100,显示为十六进制数码 C。经过 13 个时钟周期后,在电路的输出端 ROUT 得到校验符号 $R { = } 0 1 0 0$ ,在电路的输出端 SOUT 得到校验符号 $S { = } 1 0 0 0$ 。从右数第 4 个数码管显示校验符号 $R$ ,显示为十六进制数码 4,从右数第 1 个数码管显示校验符号 S,显示为十六进制数码 8。与理论计算、仿真结果一致。

图 85 第 13 个时钟周期之后得到校验符号

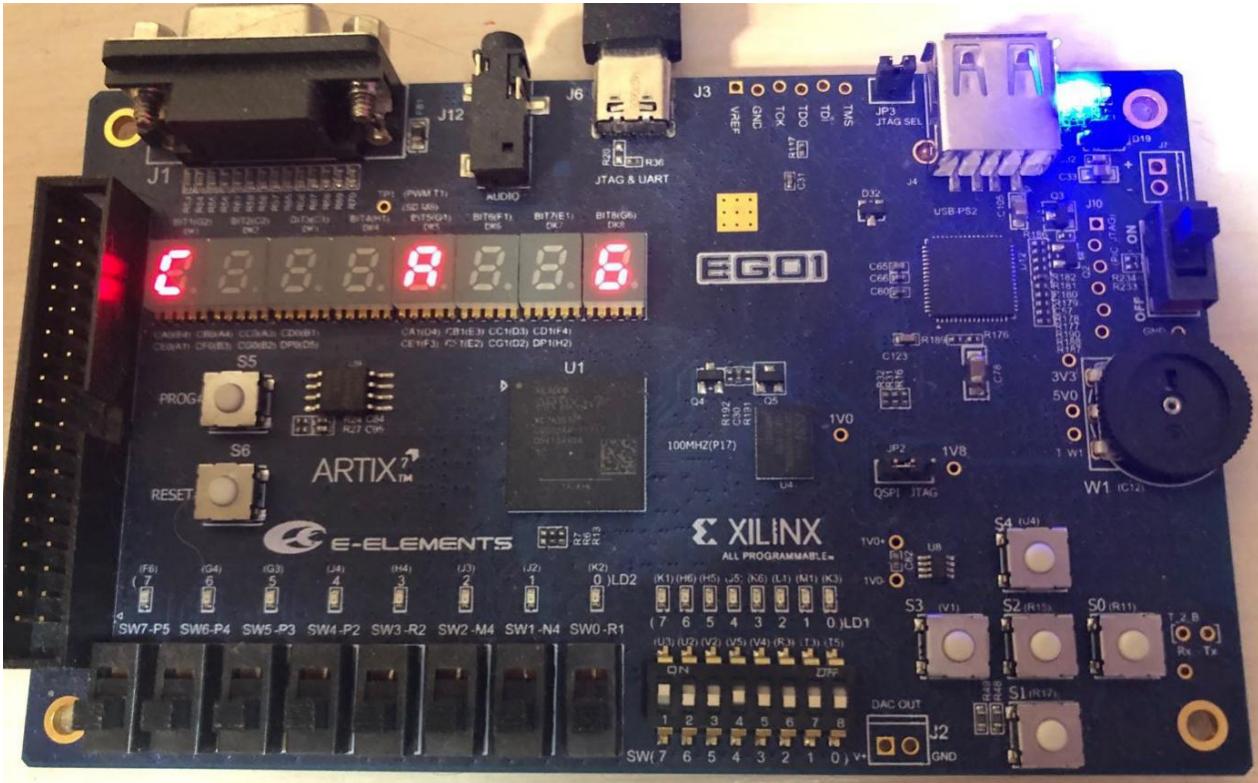

改变信息符号再次下载到 EGO1 口袋实验板进行验证,本次验证的信息符号 d13、d12、d11、d10、d9、d8、d7、d6、d5、d4、d3、d2、d1 依次给定为 0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100。这样的信息符号无法由拨码开关提供。因此专门设计了一次计数器,也就是图 86 中的符号产生电路模块,此模块产生 0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100 信息符号,如图 87 所示的第 45 行到第 51 行。左侧四个拨码开关的位置永远保持在低电平,提供第一个信息符号 0000 作为初态,然后由符号产生电路依次生成0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100 送入编码器 rsencoder的输入端 datain。

图 86 内部连接示意图

图 87 与图 86 对应的顶层源程序(Verilog-HDL)

信息符号 d13、 $d _ { 1 2 }$ 、d11、d10、d9、d8、d7、d6、d5、d4、d3、d2、d1 依次给定为 0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100。如图 88 所示,左侧第一个数码管连续显示信息符号,经过 13 个时钟脉冲后,在第13 个时钟周期左侧第一个数码管显示 $d _ { 1 }$ ,即 1100,其十六进制数码的表示为 C,在第 13 个时钟周期电路的输出端 ROUT 得到校验符号 $R { = } 1 0 1 0$ ,其十六进制数码的表示为 A,右侧第四个数码管显示 A,在电路的输出端 SOUT 得到校验符号 $S { = } 0 1 1 0$ ,其十六进制数码的表示为 6,右侧第一个数码管显示 6。与理论计算、仿真结果一致。

图 88 第 13 个时钟周期之后得到校验符号

7. 教学实施进程

(1)发布实验任务。

要求学生查找有限域乘法运算及编码原理的相关技术资料。发布EGO1 口袋实验板技术资料,要求学生课下阅读,熟悉实验环境。

(2)学习MOOC 视频

学习中国大学 MOOC 平台数字电子技术基础 SPOC 课有关 EGO1 口袋实验板、VIVADO软件的安装、设计、下载、数码管动态显示原理的相关视频。EGO1 口袋实验板MOOC 视频如图89所示。数码管动态显示原理MOOC 视频如图90所示。

图 89 EGO1 口袋实验板 MOOC 视频

图 90 数码管动态显示原理MOOC 视频

(3)组建学习小组。

除课下同学们自己讨论外,定期组织同学们讨论,助教和教师均参与。图 91 同学们在热烈讨论。

图 91 小组讨论

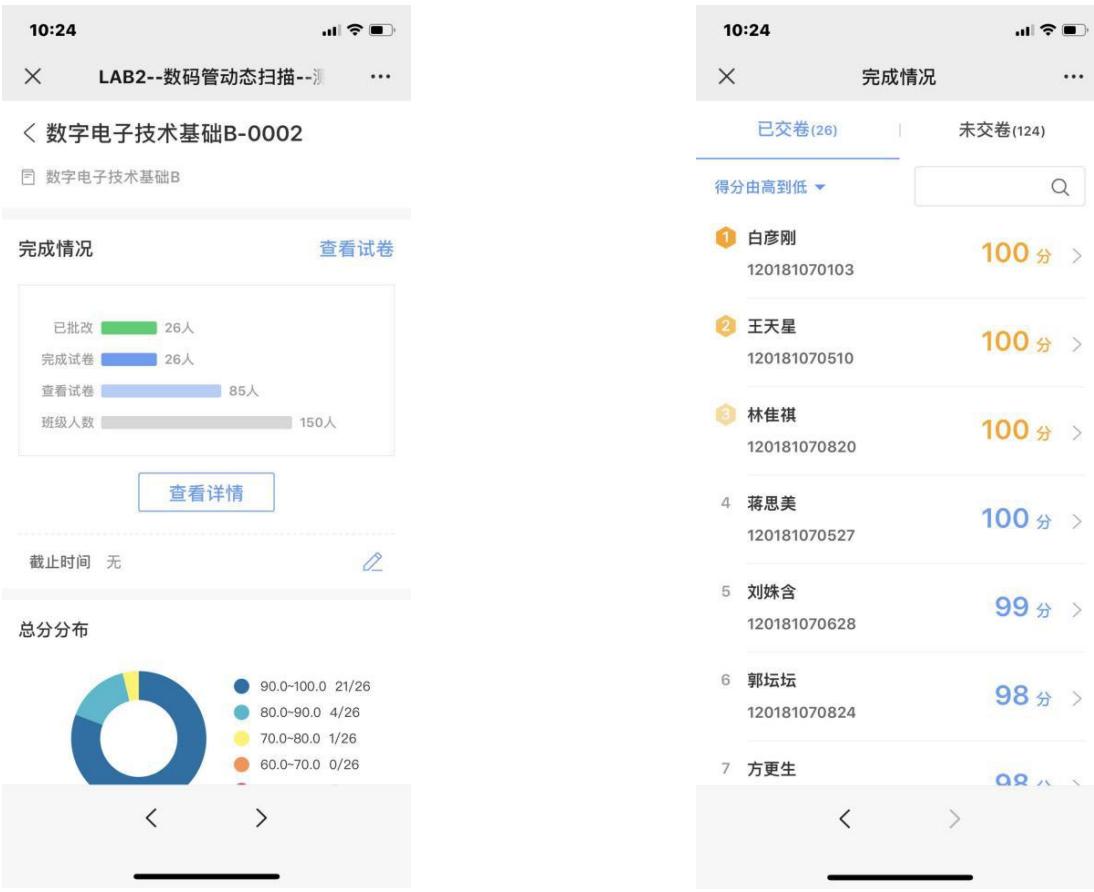

(4)使用雨课堂智慧教学工具发布 EGO1 口袋实验板相关的知识点,共 100 题,检验学生对相关知识点的掌握情况。如图92、图93所示。

图 92 雨课堂测试

图 93 雨课堂测试

(5)提交预习报告。

(6)定期组织答疑、讨论。如图94所示。

图 94 教师、助教答疑

(7)提交实验报告,总结实验体会、经验和教训。如图95所示。

图 95 学生分享心得体会

(8)开启雨课堂,每个学生独立完成现场雨课堂测试题,要求 95分以上,下载验证。如图96所示。使用投稿功能上传表示已经成功下载的30秒小视频。

图 96 验收

8. 实验报告要求

(1)阐述实验目的、实验任务。

(2)详细写出理论设计过程。

(3)VIVADO 环境下仿真、调试程序、下载验证。

(4)回答问题。

(5)实验总结,个人体会。

9. 考核要求与方法

(1)相关知识点的雨课堂测试。课前。 $1 5 %$ 。

(2)预习报告,过程是否详细。课前。 $20 %$ 。

(3)EGO1 口袋实验板实际操作是否熟悉。课中。 $20 %$ 。

(4)提交电子实验报告,实验报告是否规范、完整。软件设计过程是否截图、仿真结果是否截图、实验板电路是否拍照。是否回答问题。对实验结果的正确性是否分析。实验过程出现的故障是否有详细描述。提交的照片与理论设计过程是否一致。是否有实验的体会、反思。课后。 $2 5 %$ 。

(5)演讲、答辩。课后。 $20 %$ 。

10. 项目特色或创新

(1)综合性强。涉及到数据选择器、二进制译码器、显示译码器、二进制计数器、编码器等知识点。

(2)两种HDL 语言混合编程。

(3)采用对比学习方法,将 2 位共阴数码管动态显示电路与其 Verilog-HDL 描述一一对应,可快速提升学生对 Verilog-HDL 的接受速度。只需做简单的改变就可扩展至4位、8位数码管动态显示电路,体会HDL 描述数字电路的优势。

参赛信息表

| 案例提供单位 | 华北电力大学 | 相关专业 | 自动化、智能电网、测控、 | |||

| 设计者姓名 | 李月乔 | 电子邮箱 | lyqiao@ncepu.edu.cn | |||

| 移动电话 | 13146992391 | 通讯地址(含邮编) | 102206,北京市昌平区北农路2号华北电力大学电工电子中心 | |||

| 设计者姓名 | 樊冰 | 电子邮箱 | fanbing@ncepu.edu.cn | |||

| 移动电话 | 13810402555 | 通讯地址(含邮编) | 102206,北京市昌平区北农路2号华北电力大学电工电子中心 | |||

| 设计者姓名 | 杨晓静 | 电子邮箱 | yangxiaojing@ncepu.edu.cn | |||

| 移动电话 | 13810083019 | 通讯地址(含邮编) | 102206,北京市昌平区北农路2号华北电力大学电工电子中心 | |||

| 相关课程名称 | 数字电子技术基础实验 | 学生年级 | 自动化1703、04班;智能电网1801、02、03班;测控1801、02班 | 学时(课内+课外) | 20(20+20) | |

| 支撑条件 | 仪器设备 | EGO1口袋实验板 | ||||

| 软件工具 | VIVADO 2017.2、Multisim12 | |||||

| 主要器件 | ||||||