基于FPGA的流水灯电路设计

实验题目:基于FPGA的流水灯电路设计

课程简要信息

课程名称是《电子器件与电路(二)》,它是我校工程科学学院一门本科生三年级上学期课程,内容涵盖数字逻辑(含HDL、FPGA)、集成电路版图设计、时序分析和硬件调试,学时数为56(理论)+32(实验),实验课不是独立设课。培养计划和教学大纲加拿大麦克马斯特大学教授制定,由我校老师和外籍教授(18(理论)+8(实验))共同授课。本实验是FPGA应用方面的第一个入门性质的实验,总共两次实验课(8学时)。在电子信息类专业开设的数字电子技术实验也是适用的。

我校工程科学学院是全国首批四所“示范学院”之一(另外三所是,天津大学药物科学与技术学院、上海交通大学数学系、西安交通大学可持续发展学院)。 “示范学院”是国家外国专家局和教育部提出实施“高校国际化示范学院推进计划”建立的,目的是通过引进海外高层次专家团队,推动高校二级学院在教学、科研、管理等方面实现体制机制创新。目前,共三批十六所高校获示范学院立项。

实验内容与任务(限500字)

根据所学数字电子技术理论知识,把二进制译码器、计数器和分频器等单元电路结合起来,按照框图1.1完成一个流水灯电路设计。

图1.1 流水灯电路组成框图

基本要求:

-

每隔1秒钟,点亮一个LED灯,依次点亮8个LED后,再从头开始循环。

-

当使能端nEN=1(高电平)时,3/8线译码器不工作,所有发光二极管均熄灭;当nEN=0(低电平)时,译码器正常工作。要求采用数据流方式对电路建模。

-

当异步清零端nCLR=0时,计数器被清零;当nCLR=1,Mod=0时,可逆计数器递增计数,发光二极管从下往上(L

0~L7)依次被点亮;当nCLR=1,Mod=1时,可逆计数器递减计数,发光二极管从上往下(L7~L0)依次被点亮。另外,对50MHz的振荡器进行分频,得到1Hz脉冲信号,作为计数器的时钟脉冲输入。 -

根据框图,使用Verilog HDL和分层次、分模块的方法设计电路。

-

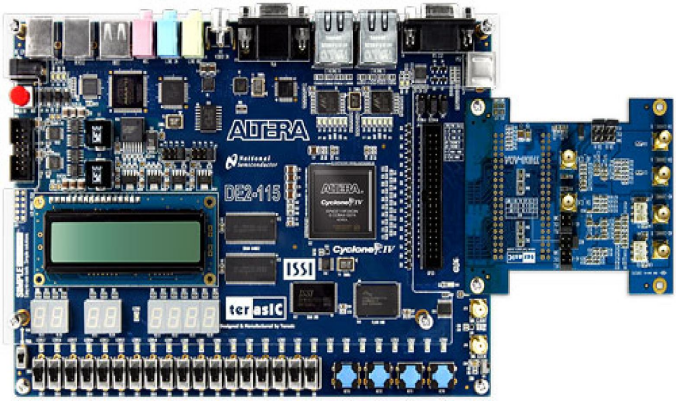

在FPGA开发平台(DE2-115)上实现该电路,观察、记录实验结果。

扩展要求:

-

去掉可逆计数器中的模式控制开关Mod,让计数器能够自动地完成加、减计数功能。即计数器先递增计数,计到最大值7时,自动地进行递减计数,递减到0时,再自动地进行递增计数,如此不断地循环(0→1…→7→6…→0→1…)。

-

将图1.1中虚线框内部的两个模块改为8位移位寄存器,是否可以完成上述电路的所有功能?如果将移位寄存器设计成具有置数、保持和双向移位功能的电路,会带来什么样的好处?试通过实验,来验证你的想法。

-

如果希望实现16个发光二极管的流水灯电路,你会如何扩展设计?试通过实验进行验证。

实验过程及要求(限300字)

-

在理论课堂上讲到用Verilog HDL建模时,现场演示仿真软件(ModelSim)的使用方法。并要求学生在自己的笔记本上安装仿真软件,给出相关学习资料,让学生自己课外学会仿真方法。

-

在理论课堂上讲到计数器的Verilog HDL建模时,有意识地讲解实验内容。在黑板上画出图1.1所示的框图,分析电路的工作原理;布置作业,让学生对其中的单元电路进行设计与仿真。(比实验课提前两周)

-

要求学生在实验课前,用Verilog HDL数据流描述方式,编写3/8线译码器模块电路,学会用ModelSim软件进行仿真分析。

-

做该实验的第一次课,除布置实验任务外,要讲解Quartus Prime 17.1软件使用过程,还要讲解如何使用开发板(DE2-115)上提供的各种资源(例如,开关、LED灯等)。现场指导学生在开发板上完成3/8线译码器模块的测试验证(教师要给出比较详细的学习文档)。

-

第一次实验课后,要求学生继续完成其他单元模块的设计与仿真;最后,完成顶层电路的设计与仿真。体会自底向上的层次化设计方法。(有条件的话,可以让学生将DE2-115带回宿舍)。

-

上第二次实验课时,学生在开发板上完成整体电路的调试与功能测试。本次实验课,老师的主要任务是解决学生提出来的各种具体问题,并对实验结果进行验收,做好成绩记录。

-

扩展要求不安排课内学时,供有兴趣、有能力的同学在课外选做。如果学生完成了扩展实验,老师要验收实验结果,并做好登记,作为平时成绩的一部分。

相关知识及背景(限150字)

这是一个数字电子技术实验的典型案例,能够将译码器、计数器、分频器、移位寄存器、FPGA器件、Verilog HDL及EDA技术等相关知识结合起来,实现一个功能比较简单、又具有一定趣味性的流水灯实验项目。

教学目的(限100字)

推动实验课程在 FPGA 新技术方面教学活动的开展。

通过课堂实验和课外开放实验相结合的方式,引导学生分模块、分层次进行电路设计。通过扩展实验,了解实现方法的多样性。培养学生运用理论知识的能力,掌握EDA技术。

实验教学与指导

在实验教学中,应在以下几个方面加强对学生的引导:

-

上实验课时,要求学生自己复习相关的理论知识(译码器、计数器、分频器、Verilog HDL等)。布置实验任务时,要讲清楚设置实验基本要求及扩展要求的目的,说明扩展要求的验收没有时间限制,只要在实验课结束之前都可以验收。要鼓励学生自主学习的积极性,消除学生对实验课程的畏惧心理。

-

做该实验的第一次课,要讲解图1.1所示框图的工作原理。要求先用Verilog HDL设计各个单元电路,再调用各个模块组成顶层电路,并用ModelSim软件进行仿真分析。

-

还要讲解Quartus Prime 17.1软件使用过程,讲解开发板(DE2-115)上提供的各种资源(例如,开关、LED灯等)的使用方法。具体内容包括新建工程项目、输入Verilog HDL源文件、编译、分配引脚、综合、对FPGA器件进行编程、在开发板上测试电路工作情况。要指导学生在开发板上完成3/8线译码器模块的测试验证。

-

第二次课,讲解时序电路的仿真方法。对于分频器的仿真,要缩小分频系数。还要讲解测试计数器与译码器功能方法。在实现分频器之前,可以用实验板上的按钮开关作为时钟信号,测试电路的功能。每按动一次(按下再松开)按钮,产生一个单脉冲。

-

对于16个发光二极管的流水灯电路设计,先提问,并请同学回答,然后再给出提示。即实例引用两次8位移位寄存器;或者设计一个带参数的通用移位寄存器模块,在顶层实例引用该模块时,将参数值传到子模块中。

实验原理及方案

流水灯实验采用计数器加上译码器、或者采用采用移位寄存器都能够实现。其实现框图分别如图1.1和图1.2所示。

采用分层次、分模块的方法进行设计。先使用Verilog HDL分别对各个单元电路进行建模和仿真,再实例引用底层模块组成顶层电路。最后,使用FPGA开发板实现整个电路,并进行功能测试。

图1.2 移位寄存器构成的流水灯电路

实验报告要求

实验报告需要反映以下工作:

-

设计过程及实验步骤

-

单元电路、整体电路设计思路和代码(对代码要进行注释)、仿真分析结果,对仿真波形要有解释或说明。

-

电路测试方法描述

-

实验结果记录及描述

-

实验过程中遇到的困难、问题及其解决方法

-

实验的收获、体会与建议

考核要求与方法(限300字)

对于基本功能,做该实验的第2周验收,也允许学生推迟到第3周完成并验收。对于扩展功能,则允许学生到实验课结束之前完成并验收。

-

实物验收:电路基本功能的完成程度(要求现场演示),完成时间。

-

自主创新:电路扩展功能的完成程度(要求现场演示),自主思考与独立实践能力。

-

代码与仿真:打开工程文件,对随机抽查的代码进行讲解。检查单元电路与整体电路仿真完成程度。

-

实验报告:实验报告的规范性与完整性。

项目特色或创新(可空缺,限150字)

将数字电子技术课程中译码器、计数器、分频器、移位寄存器、FPGA器件、Verilog HDL及EDA技术等相关知识结合起来,实现一个功能比较简单、又具有一定趣味性的实验项目。

体现了分模块、分层次的设计方法。通过扩展电路功能,体现了实现方法的多样性。实验项目从简单到复杂、由基础到综合,循序渐进,培养学生的实践动手能力。

实验案例信息表

| 案例提供单位 | 华中科技大学 | 相关专业 | 电信、通信、电子 | |||

|---|---|---|---|---|---|---|

| 设计者姓名 | 罗杰 | 电子邮箱 | Luojiewuhan@hust.edu.cn | |||

| 移动电话 | 18186487079 | 通讯地址 (含邮编) |

华中科技大学电信学院430074 | |||

| 设计者姓名 | 吴建新 | 电子邮箱 | wujx@hust.edu.cn | |||

| 移动电话 | 13507167927 | 通讯地址 (含邮编) |

华中科技大学电信学院430074 | |||

| 设计者姓名 | 龚军 | 电子邮箱 | gongjun@hust.edu.cn | |||

| 移动电话 | 13349830568 | 通讯地址 (含邮编) |

华中科技大学电信学院430074 | |||

| 相关x课程名称 | 电子器件与电路(二)(数字电子技术实验) | 学生年级 | 大二下或者大三上 | 学时(课内+课外) | 8+8 | |

支撑 条件 |

仪器设备 | 计算机、FPGA开发板(DE2-115) | ||||

| 软件工具 | Quartus Prime 17.1,ModelSim 10.5b | |||||

| 主要器件 | ||||||