基于Matlab仿真+VerilogHDL的5G Reed-Muller码译码器设计

课程简要信息

课程名称:数字系统课程设计

课程学时:20学时

项目学时:课内20学时、课外12学时

适用专业:电子信息类(电子信息工程、通信工程)

学生年级:大二下

实验内容与任务(限500字,可与“实验过程及要求”合并)

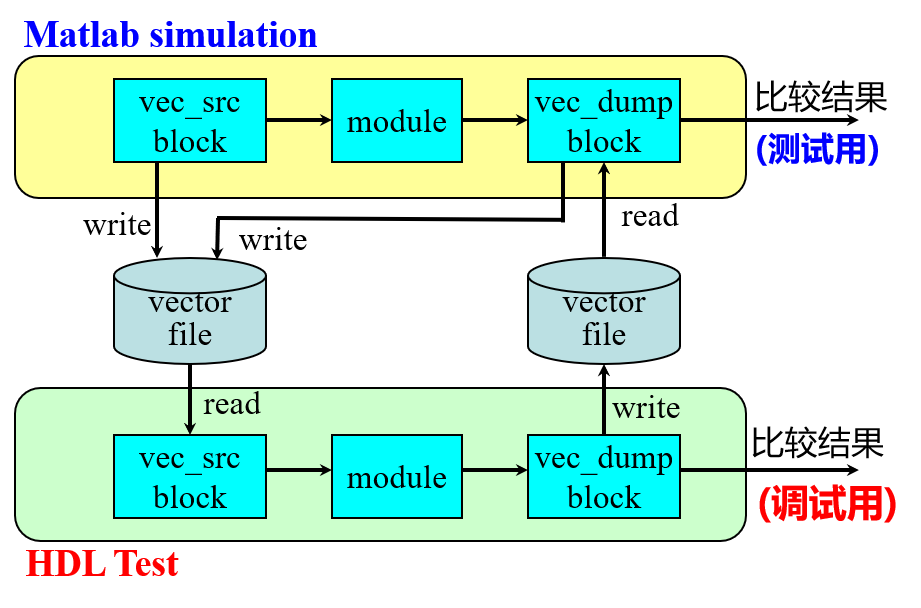

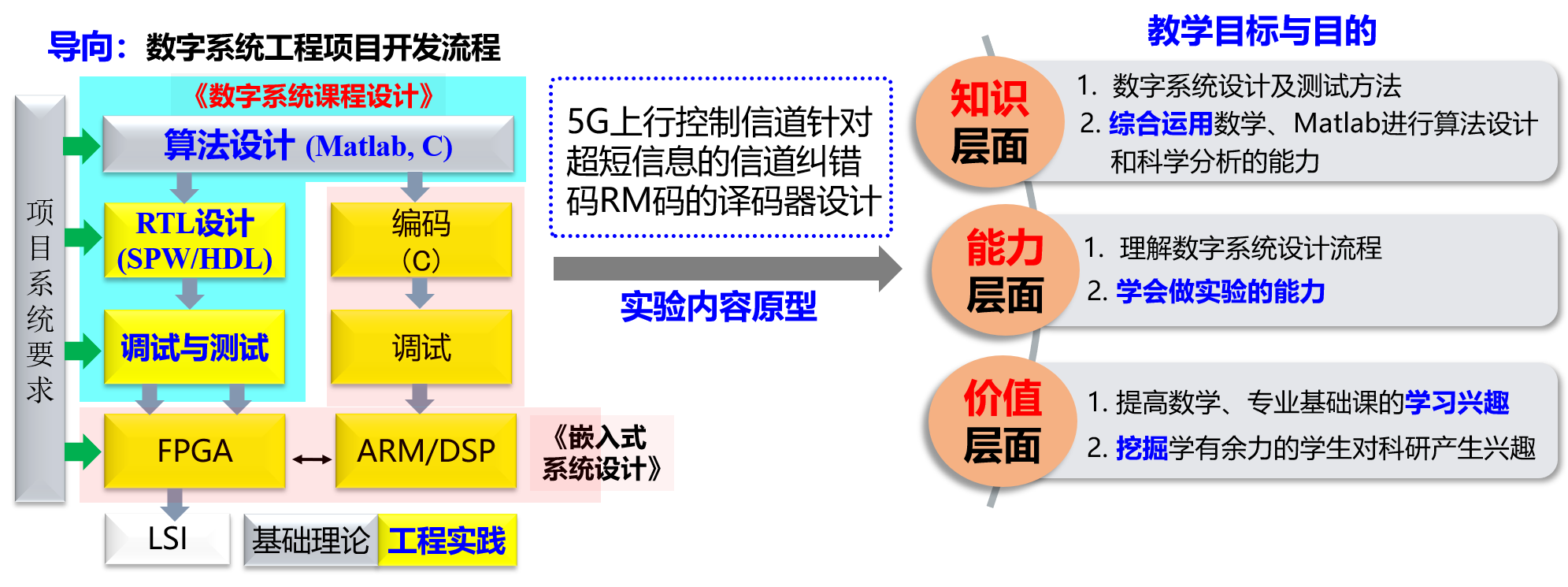

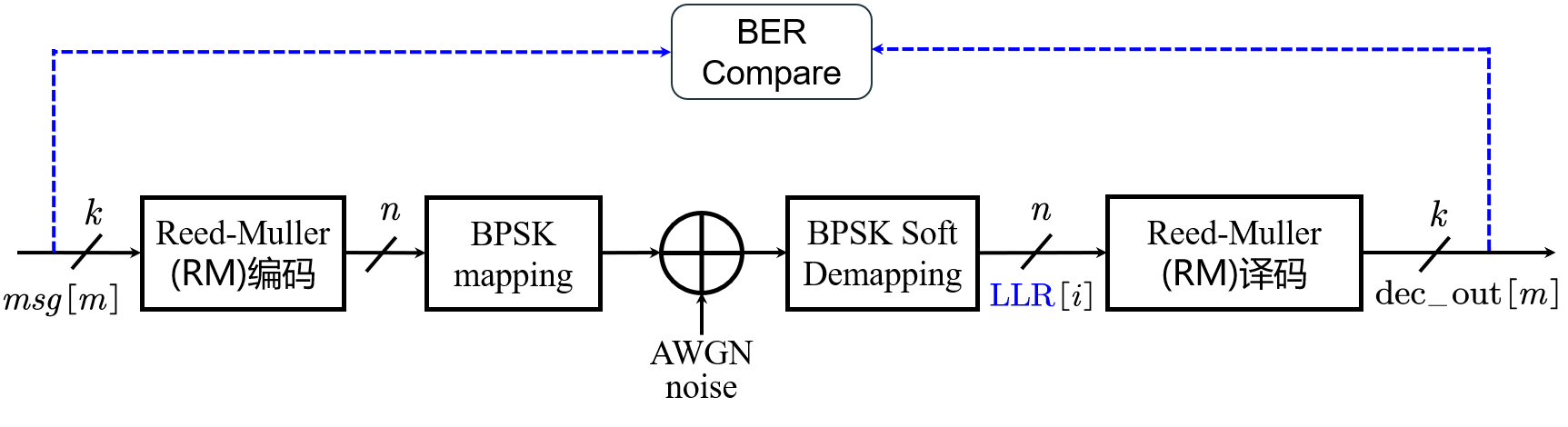

图2-1 实验系统框架

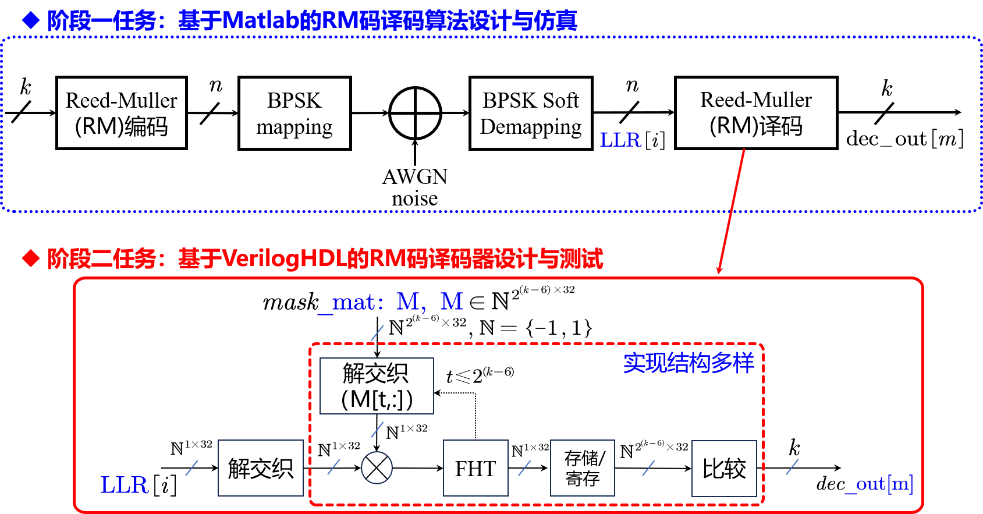

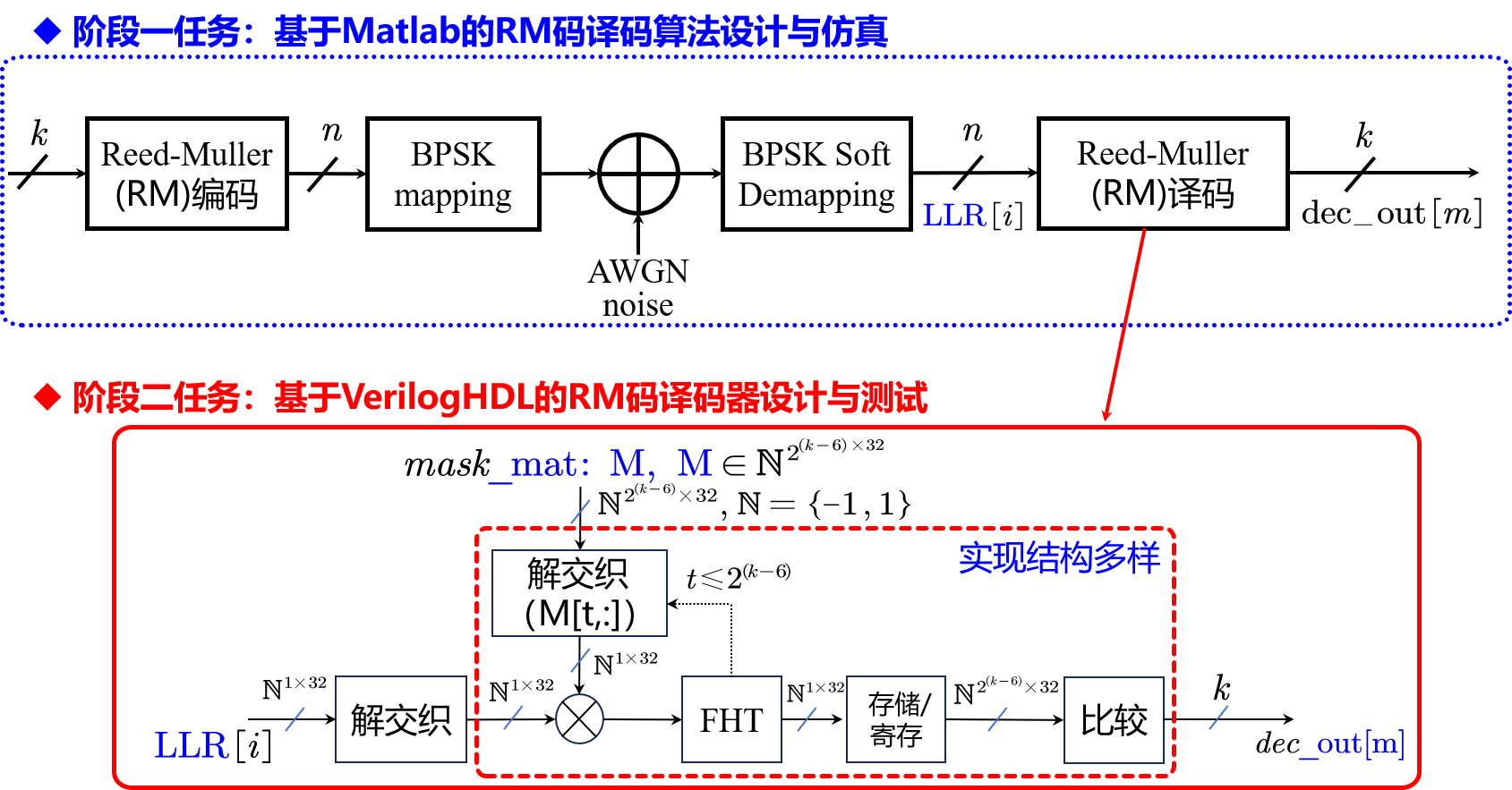

本案例的项目设计任务围绕“5G移动通信物理层中使用的Reed-Muller(RM)码的译码器设计与实现”展开。RM码是一种线性分组结构的前向纠错码,由于其低复杂度的编码和译码方法,以及在超短码(信息比特在3-11比特范围)上的优良纠错性能而得到广泛应用。4G/5G系统连续采用了RM码作为上行控制信道针对超短码信息(3-13比特)的信道纠错编码方式。

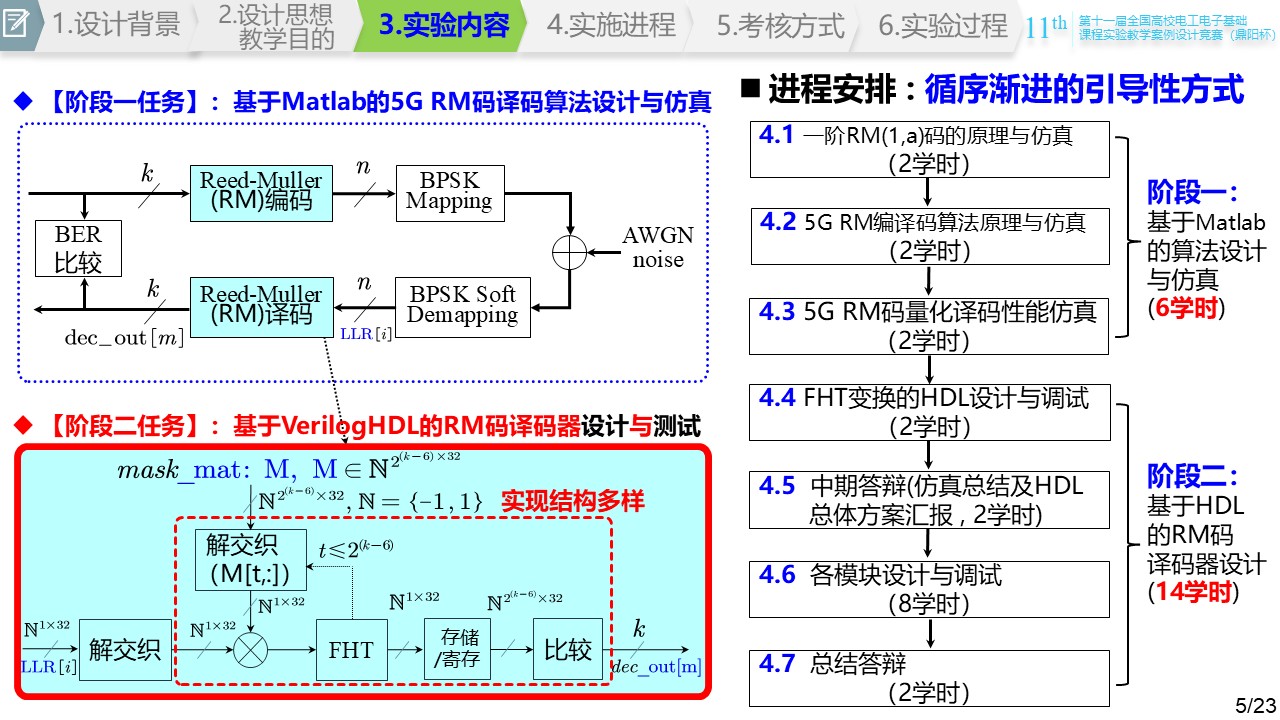

实验系统框架如图2-1所示,实验内容分两个阶段任务,具体如下:

【阶段一任务】:基于Matlab的5G RM码译码算法设计与仿真。

**基本任务1:**学习RM码的构造和译码原理。

**基本任务2:**基于Matlab构造RM信道编译码仿真框架,给出误码率(Bit Error Rate:BER)仿真性能。

**扩展任务1:**使用Matlab评估RM译码算法在信息量化时的纠错性能。

**扩展任务2:**针对译码性能和FHT实现时信息比特量化时的tradeoff展开评估,并给出具体仿真依据。

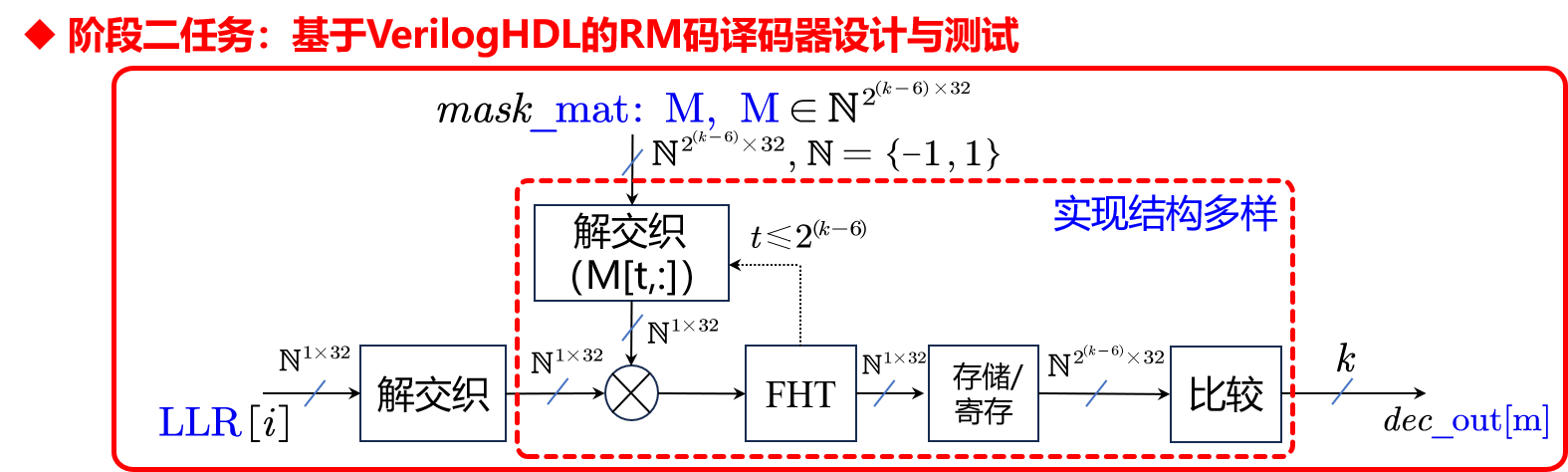

**【阶段二任务】:**基于VerilogHDL的RM码译码器设计与测试。

**基本任务1:**作为单独的公共模块,使用VerilogHDL语言设计快速哈达玛变换模块,并编写testbench对FHT模块进行调试。

**基本任务2:**设计RM译码器的数字系统整体实现方案并明确各子模块的功能划分,基于PPT完成中期答辩。

**基本任务3:**使用VerilogHDL语言完成各子模块的设计。

**基本任务4:**使用VerilogHDL编写RM译码器的testbench,进行模块逻辑调试。

**扩展任务1:**融合Matlab对RM码译码器进行逻辑测试。

**扩展任务2:**基于Vivado工具对所设计的RTL电路进行综合,并分析综合报告。

实验过程及要求(限300字)

【阶段一过程及要求】

-

**课前预习:**完成指定的中文论文2篇、英文资料2篇的阅读,并翻译其中一篇的英文资料。根据需要自行完成资料查询。

-

**RM码编译码算法理解:**理解课中理论引导式讲解,运用向量线性组合、相关运算等数学基础理论理解RM码译码算法原理。

-

**信道译码仿真框架构建:**理解并梳理信道译码仿真框架的构建,掌握基于Matlab的信道编译码仿真方法和BER测试方法。学会或者提高做仿真实验的能力。

-

**MATLAB编程能力提高:**学习或提高Matlab基于向量的编程技能,并领悟其编程特点和代码艺术。

-

**量化性能评估:**理解未来FPGA实现信道译码时,信息比特量化对于性能和复杂度的影响,并能学会译码器信息量化时的性能评估方法。

-

**算法性能仿真总结报告编写方法:**具体实践算法原理说明和性能仿真总结报告的编写思路和方法。

【阶段二过程及要求】

-

**基于Verilog的数字系统设计能力提高:**掌握Verilog进行数字系统实现时的总体架构设计、模块间API端口管理、FPGA占用和运算时间的权衡。提高Verilog编程能力和代码艺术。

-

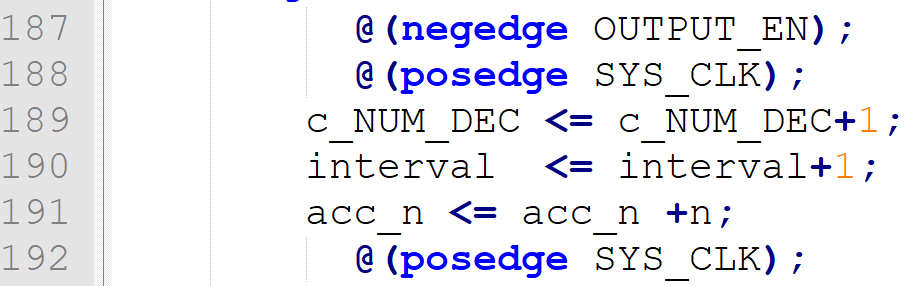

**Testbench代码能力提高:**掌握基于事件驱动型架构的激励信号生成方法和Verilog代码艺术。

-

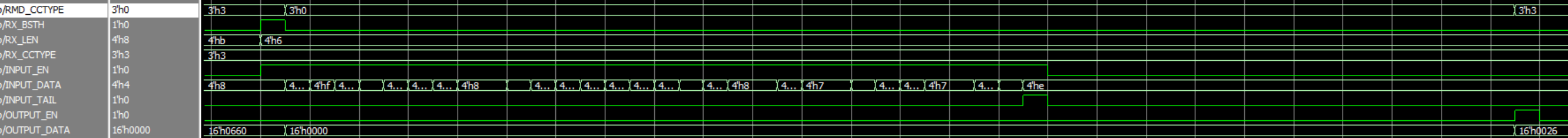

**融合Matlab的RTL电路测试方法:**理解融合Matlab对RM码译码器进行逻辑测试的必要性,并掌握进行复杂电路的仿真和测试等相关知识与技术方法。

-

**技术文档的编写思路:**具体实践技术文档的编写思路和方法。

最后,提交设计总结报告(算法性能仿真报告+RTL技术报告),并通过分组演讲,学习交流不同解决方案的特点。

相关知识及背景(限150字)

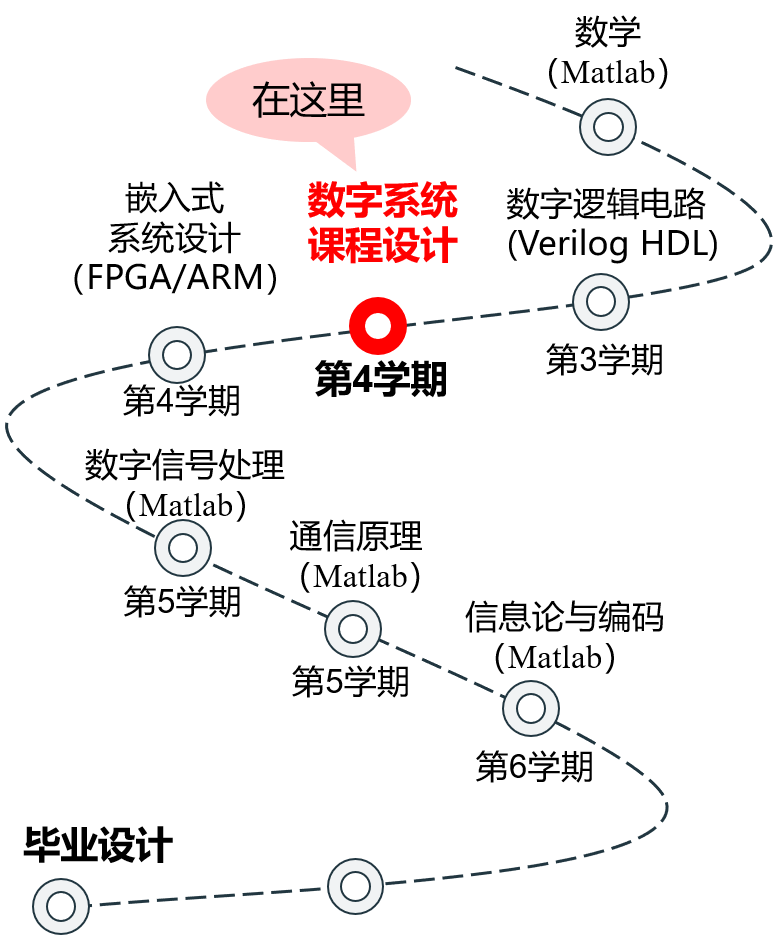

图4-1 相关背景

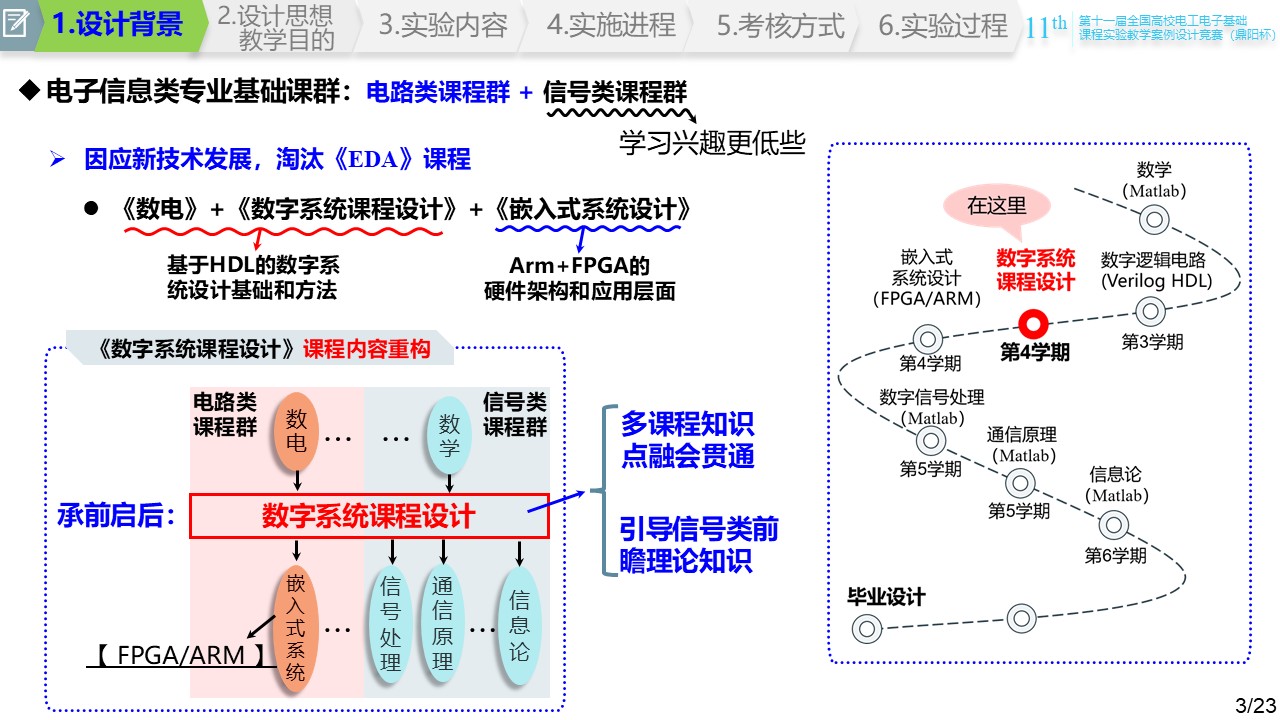

本项目是针对电子信息类专业的二年级学生所学的《数字逻辑电路》课程开设的技能实习。在新工科教学改革大背景下,我校电子信息工程专业进行了专业基础课程群建设改革:电路类+信号处理类。淘汰了原有的Matlab和EDA设计课程。将EDA设计课程的内容分散到《数字逻辑电路》+《数字系统课程设计》+《嵌入式系统设计》中。《数字逻辑电路》在理论基础知识的基础上,增加VerilogHDL的基础知识和基础实验内容。《嵌入式系统设计》课程重在ARM和FPGA的硬件架构和应用层面。《数字系统课程设计》以数字系统工程项目开发流程为导向,将基于Matlab的算法仿真、与基于Verilog HDL的数字系统设计的学习与提高相融合。结合5G移动通信技术的一个工程案例,提高学生学习兴趣,也引导学生对将要学习的《数字信号处理》、《信息论》等课程的知识产生浓厚的学习兴趣。

实验环境条件

硬件:笔记本PC

软件:Matlab、ModelSim、Vivado

教学目标与目的(限150字)

-

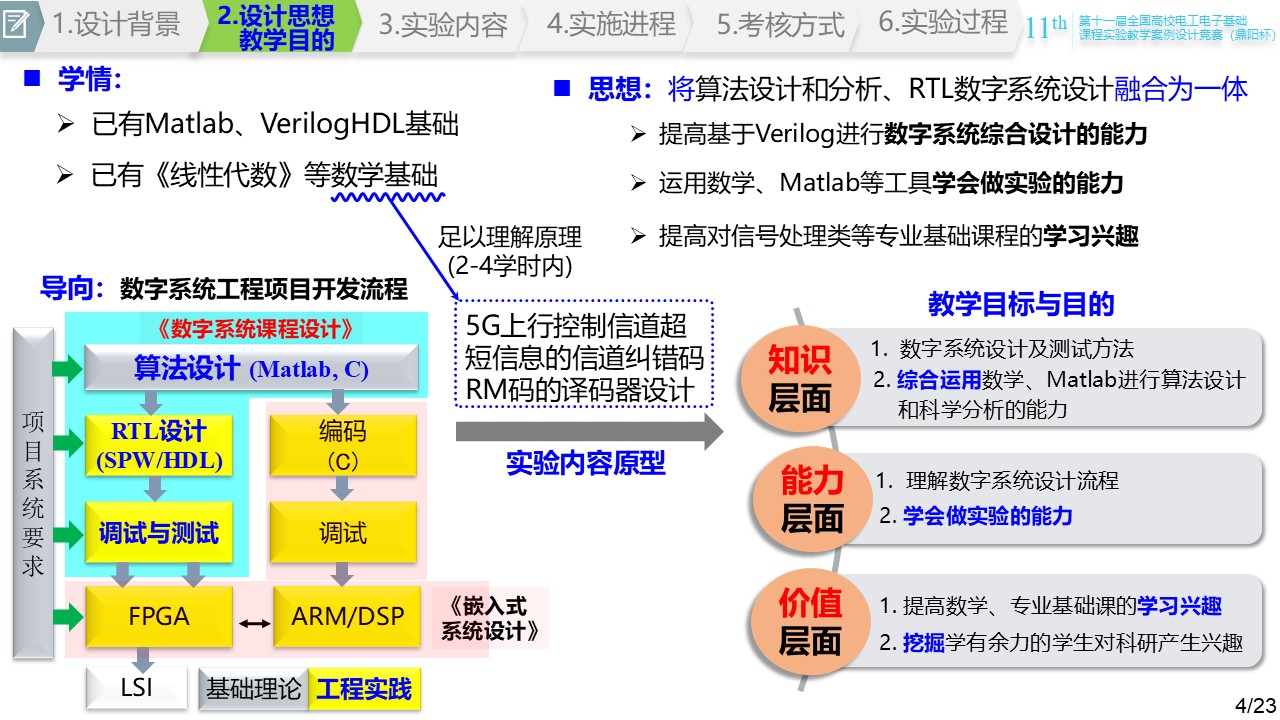

**“知识层面”的培养:**提高基于VerilogHDL进行数字系统综合设计和测试的能力,以及运用数学、Matlab进行算法设计和科学分析的能力。

-

**“能力层面”的培养:**理解数字系统设计流程和方法的基础上,培养学生学会做实验的能力。

-

**“价值层面”的培养:**切身理解基础理论与工程创新相互融合的关系,提高数学和信息类专业基础课的学习兴趣的同时,挖掘学有余力的学生对科研产生兴趣。并能切身体会我国20年来在通信领域特别是5G通信系统方面为国际做出的巨大贡献。

教学设计与实施进程

数字系统设计是现代电子信息产品开发中非常重要的关键技术。很多高校已经将《数字系统设计》作为大二学期培养电子信息类专业学生实践动手能力的重要课程。经过多年的实验教学实践改革和努力,虽然已经有很丰富和实用的教学案例,但因为大二学生课程理论基础的学习不够等因素,这些案例仍然存在多课程知识点融汇贯通、前瞻理论知识引导不够等缺点。

本项目是一个完整的项目驱动型数字系统实践项目,需要经历中英文论文和5G标准中RM码的学习理解、基于Matlab的算法仿真研究、数字逻辑电路设计方案论证、数字逻辑电路系统实现、模块仿真调试、整体逻辑功能测试等环节。最后,需要进行PPT汇报,并提交设计文档总结。在实验教学中,主要进行如下教学设计和实施。

7.1 教学设计思路

图7-1 教学设计思路

本案例以数字系统工程项目开发流程为导向,争取达到对学生“知识层面”、“能力层面”和“价值层面”等三个维度培养的教学目标与目的。具体体现在如下几个方面:

- 多课程知识点的融汇贯通,挖掘培养学生的科研兴趣或者创新意识

将基于Matlab的基础理论算法设计和仿真、与基于Verilog HDL的数字系统设计的学习与提高相融合。RM码本身属于《信息论》课程中的一个信道编码方式,通过本案例的实践过程,学生对将要学习的《数字信号处理》、《信息论》等课程的知识产生浓厚的学习兴趣。本项目还有利于挖掘学有余力的学生对科研产生兴趣。

- 立足基础知识应用、强化基础理论联系实际

数学等基础课程的学习内容较为抽象,学习难度大。本案例RM码译码算法的核心在于向量线性组合、相关运算等数学基础理论的灵活应用。案例本身结合了5G移动通信技术的一个工程实践项目,可以较好的培养学生将基础理论联系实际的能力,并提高学习兴趣,培养学生学会做实验的能力。

- 强化数字系统设计的工程实践能力,培养学生工程素养

本案例是一个综合性工程实验项目,可以让学生掌握使用Verilog进行数字系统实现时的模块间API端口管理、有符号定点数处理、以及融合Matlab产生测试向量进行复杂电路的仿真调试和测试等相关基础知识与技术方法。

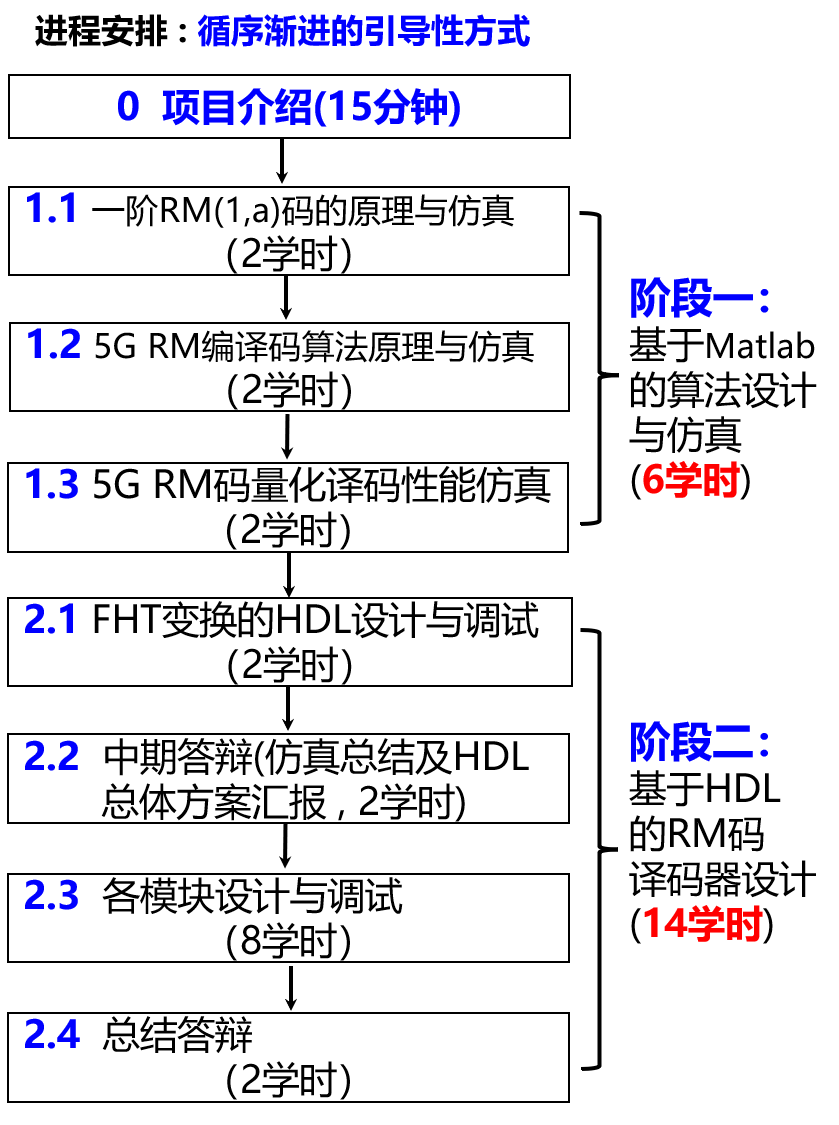

7.2 教学实施

教学实施总体进程以循序渐进的引导性方式,如图7-2所示分7个步骤完成。

图7-2 教学实施进程安排

具体步骤如下表所示:

| 步骤 | 内容说明 | 课内学时安排/课后学时预估 |

|---|---|---|

阶段一任务: 1.1 符合5G标准的一阶RM码的编译码原理与仿真 |

1.教师进行实验项目介绍(15分钟,面授),包括信道编译码的基本概念,整体实验内容概述,以及一阶RM码的基本原理和需要提前学习的内容;布置翻译一篇RM码的英文文献(8页A4),重点理解一阶RM(1,m)码编码矩阵的构造方法。 2.学生阅读完并翻译至少4页的英文文献;学习并理解教师提供的基于MATLAB的AWGN信道下BPSK的BER测试代码。

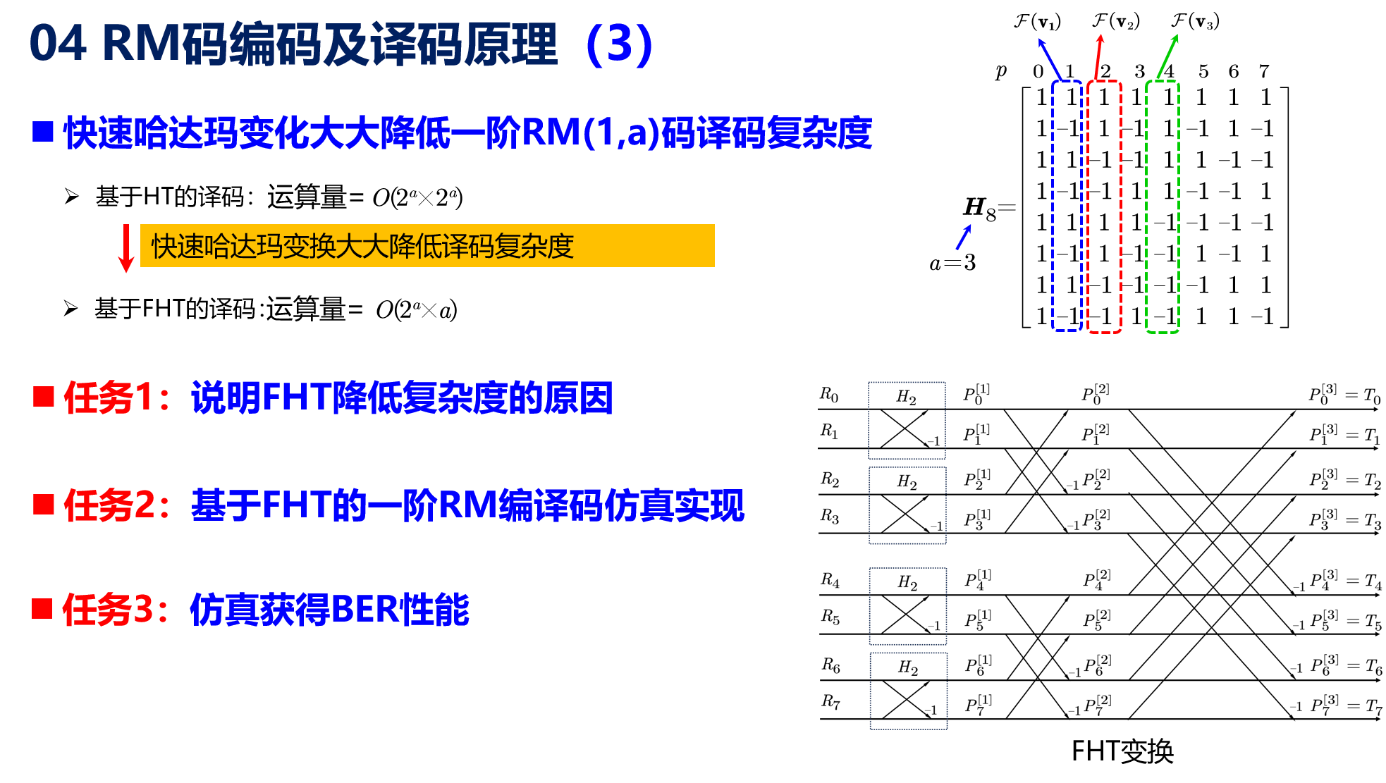

1.教师讲授一阶RM(1,a)码编码及其译码原理,本子任务的具体实验任务和要求;课中遇到的代码共性问题的讲解 2.演示本子任务的Matlab代码; 3.学生在BPSK的BER测试代码基础上完成基于5G标准的一阶RM码编译码仿真,采用基于FHT算法的译码。 4.关键点1:基于线性组合视角的编码方式,以及基于哈达玛变换(实质是接收向量与哈达玛矩阵的相关运算)的RM码译码原理;理解三种算法(穷举法、基于HT的译码算法、基于FHT的译码算法)的复杂度分析; 5.关键点2:教师视完成情况带写并演示完成一阶RM码的编译码仿真框架的构建

1.一篇中文论文的阅读:《LTE系统中Reed-Muller码的编译码算法》 2.继续阅读并完全理解RM码的英文文献资料。 3.作业:提交信息比特k小于a的5G RM码的误比特(BER)仿真性能 4.提交FHT与HT的译码复杂度比较分析方面的作业 |

2学时/4学时 |

阶段一任务: 1.2基于RM(1,a)的5G RM超码编译码原理与仿真 |

1.讲授基于掩码结构的5G RM超码编码及译码原理(15分钟);教师答疑,课中遇到的代码共性问题的讲解 2.在1.1代码的基础上完成完全符合5G标准的5G RM码译码算法仿真,并获得BER/FER性能曲线。 4.关键点1:当RM码的编码信息k大于m时的超码编码方式,及其对应的译码原理的理解。 5.完成掩码矩阵的生成代码的编写

|

2学时/2学时 |

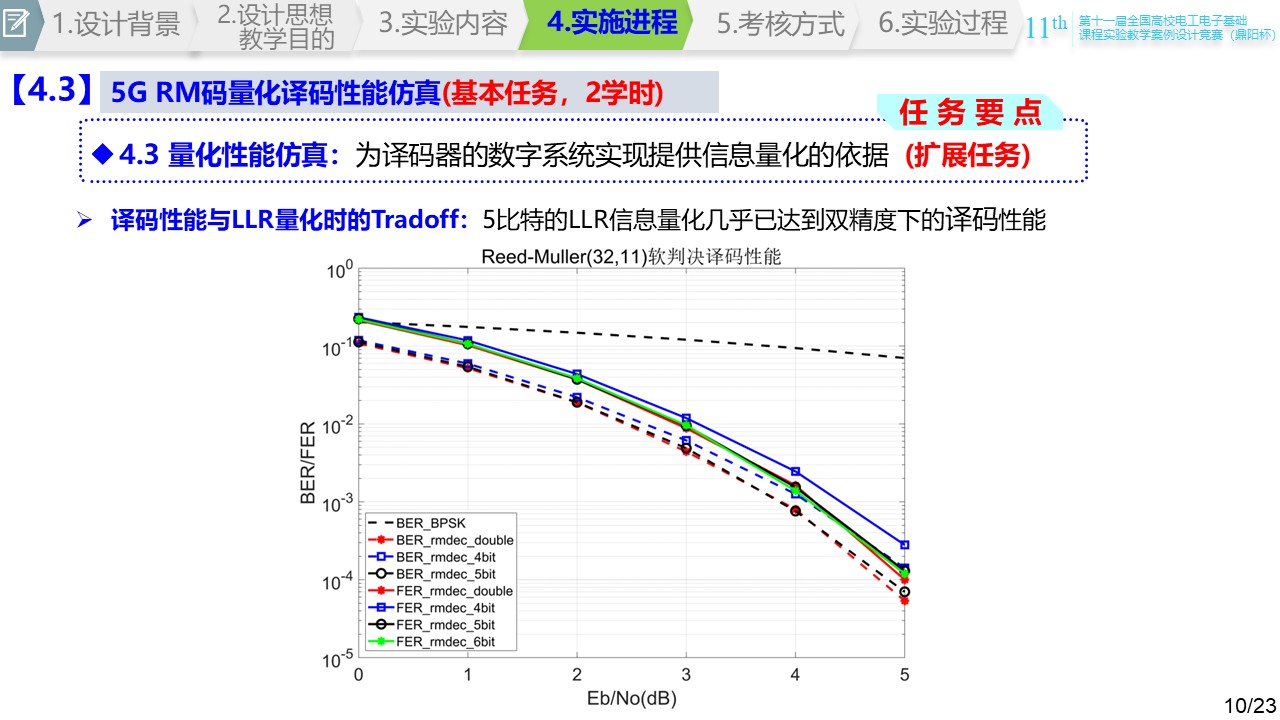

阶段一任务: 1.3 5G RM码量化译码性能仿真 |

1.讲授信道译码中译码器输入信息量化的必要性及量化仿真方法;教师答疑,课中遇到的代码共性问题的讲解。 2.学生使用Matlab评估RM译码算法在信息量化时的纠错性能 3. 学生围绕BER性能与信息量化时的tradeoff展开评估 4. 完成阶段1任务,并开始整理阶段一的文档总结。 5. 教师布置下次课暨实验任务2.1的内容(15分钟)

1.完成FHT的VerilogHDL设计方案图及要点说明 |

2学时/2学时 |

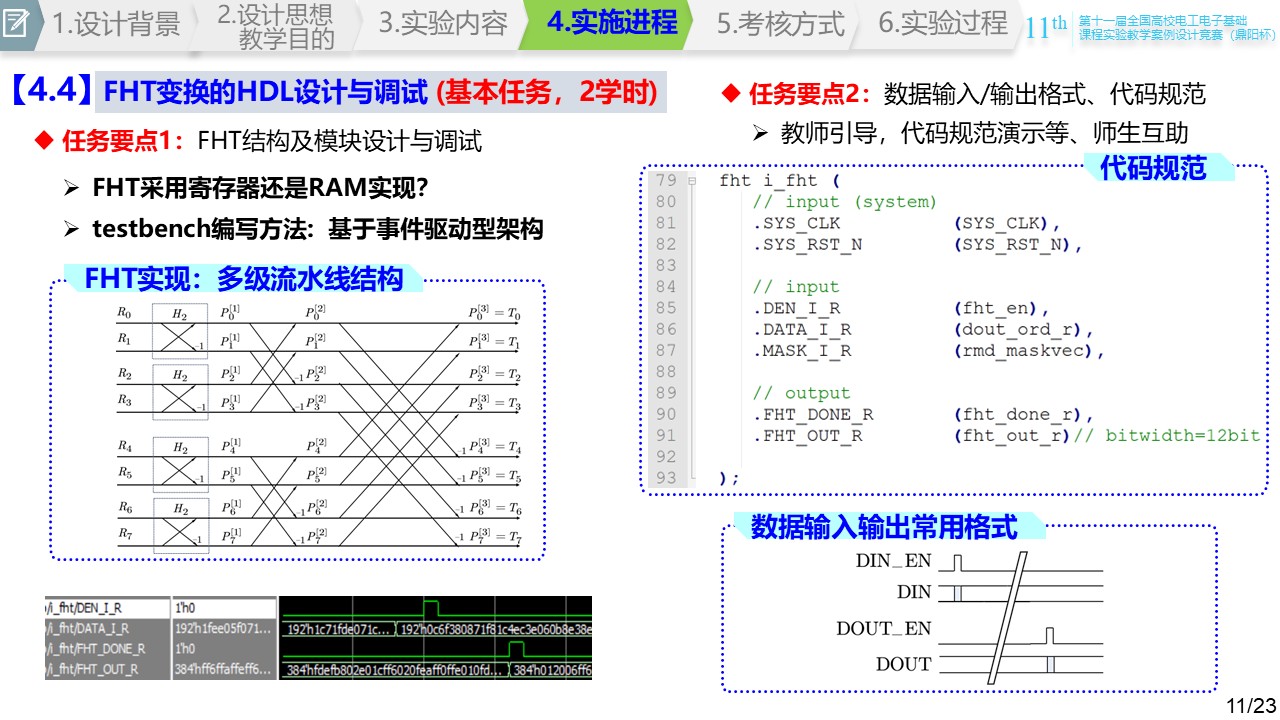

阶段二任务: 2.1 快速哈达玛变换模块的VerilogHDL设计与调试 |

整理并完成阶段一的实验报告总结;完成FHT的VerilogHDL设计方案

1.根据作业完成情况重点讲解核心关键点 2.讲授基于RAM以及基于寄存器的FHT实现架构上的优缺点。作为本案例单独的公共模块,推荐学生基于寄存器架构来实现FHT变换。 3.演示基于VerilogHDL的模块设计以及基于事件驱动型架构的testbench代码艺术;模块间API端口管理。 4.师生互助+学生自主编码模式下完成FHT的模块设计和仿真调试 5. 课中最后15分钟传授基于二维数组形式的信号定义的便利性,以及二维数组信号不能作为输入输出端口的解决办法。

1. 完成2.1的所有任务 2.学生设计RM译码器的数字系统整体实现方案并明确各子模块的功能划分,完成中期答辩PPT和关于算法原理说明和性能仿真的中期总结报告。 |

2学时/2学时 |

阶段二任务: 2.2 中期答辩及整体方案汇报 |

学生完成2.1的所有任务;完成阶段二任务的整体方案设计并体现在中期答辩PPT中。

1.中期答辩及点评(重点围绕仿真结果的解读和后续RM译码器的Verilog整体方案的设计) 2.教师点评:FPGA实现时资源占用率及运行效率视域下的整体实现方案讨论 3. 以共性问题提出中期总结报告的修改意见

讨论完善并确定系统实现方案 |

2学时/1学时 |

阶段二任务: 2.3 完成各子模块的设计及调试 |

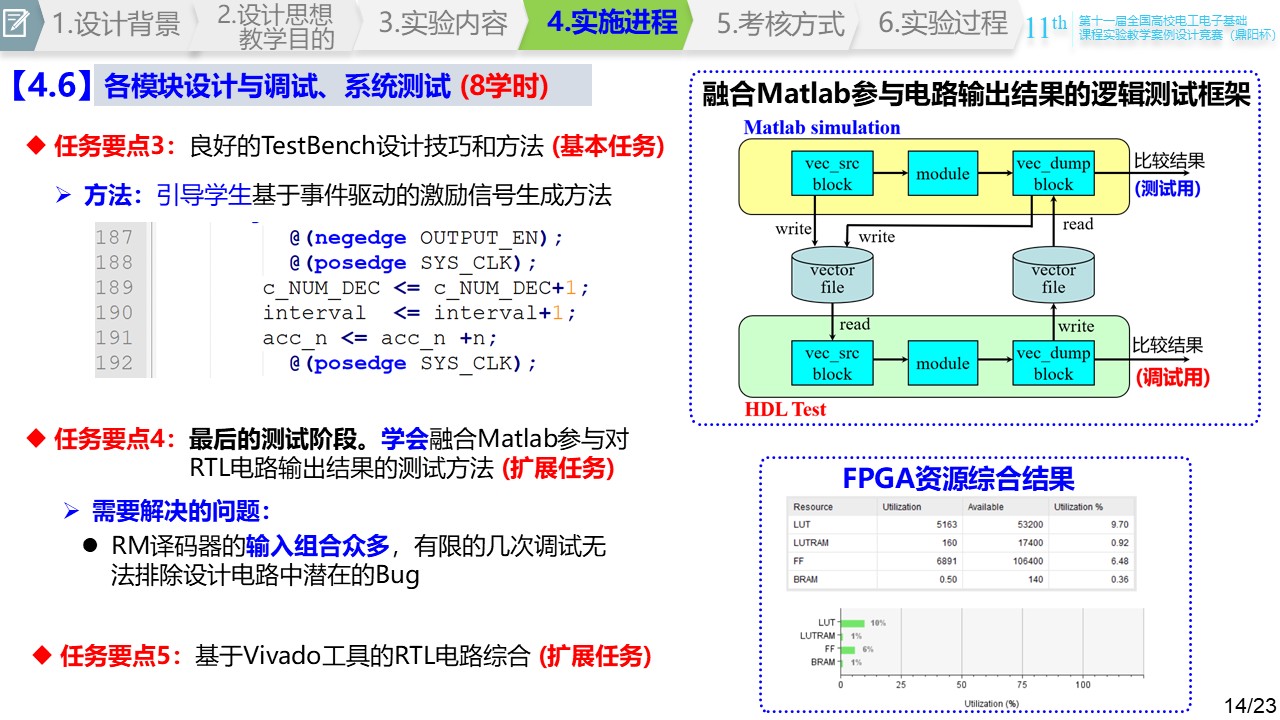

1.组内讨论+学生自主编码,完成各子模块的设计与调试 2.教师对共性问题进行解答 3.教师讲授:融合Matlab对RM码译码器进行逻辑测试的重要性及实现思路与方法

|

8学时 |

阶段二任务: 2.4 总结答辩 |

1.分组演讲答辩及点评

1.学生根据教师意见修改答辩PPT以及总结报告 |

2学时/1学时 |

实验原理及方案

8.1系统结构

依据项目规划,整理出本项目的两个阶段性任务,并规划清晰各阶段的具体任务、关键技术原理与时间安排。

图8-1 实验任务系统总体结构

- 阶段一任务:基于Matlab的5G RM码译码算法设计与仿真

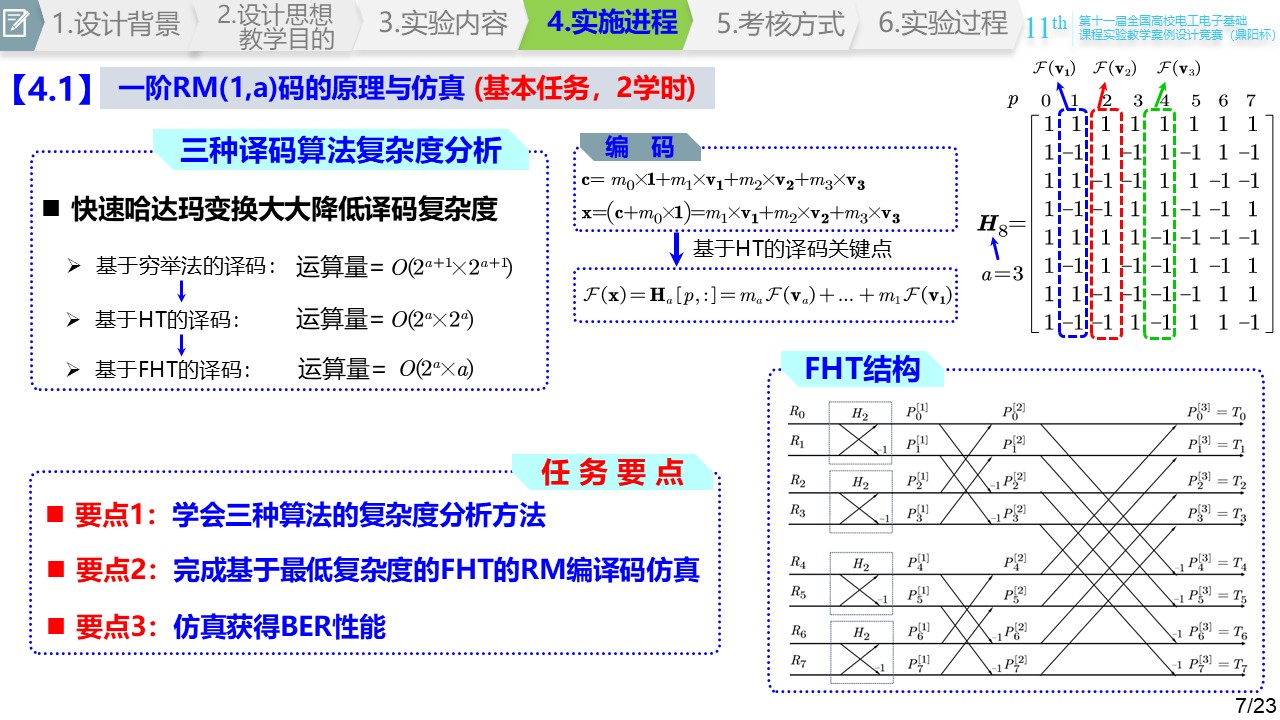

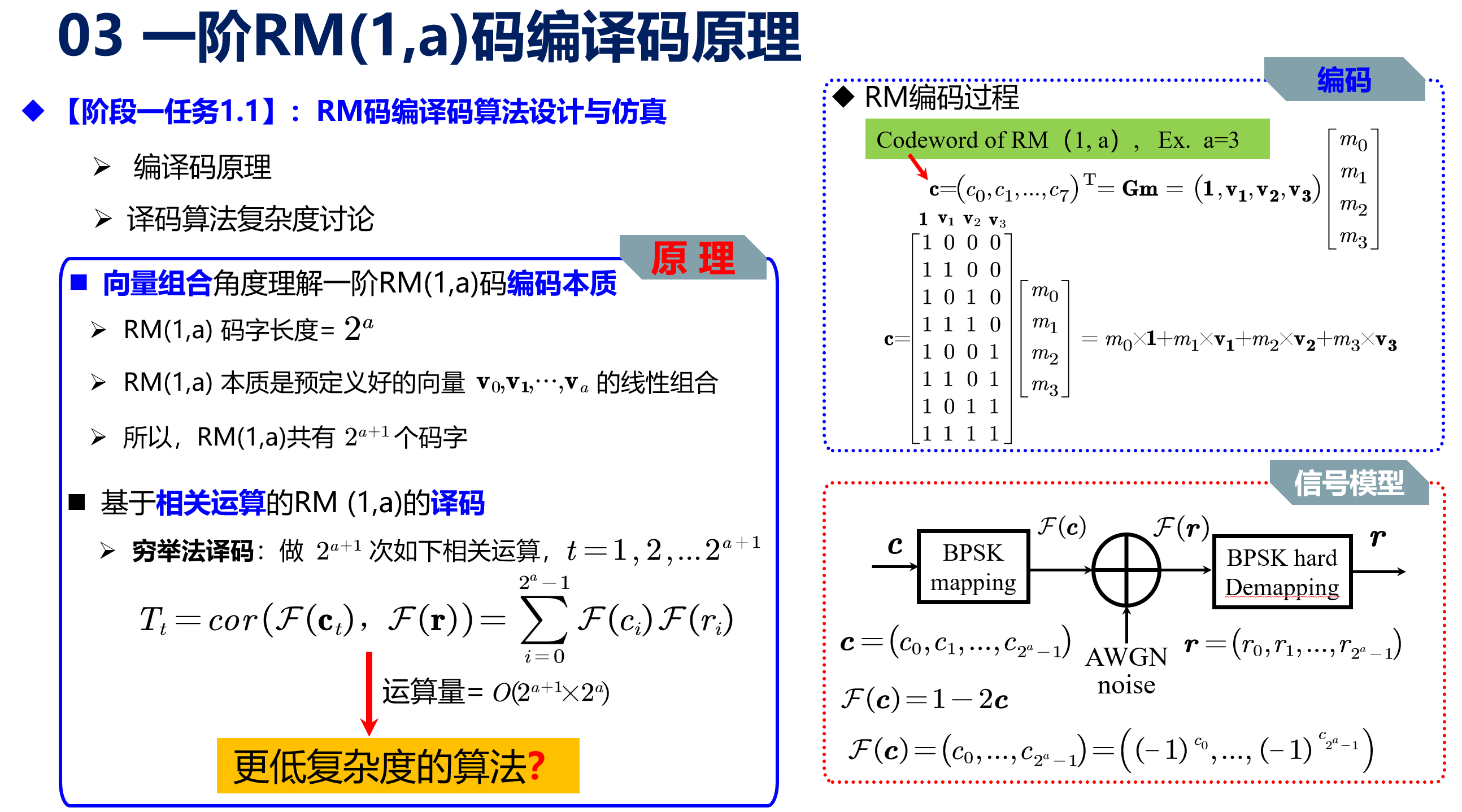

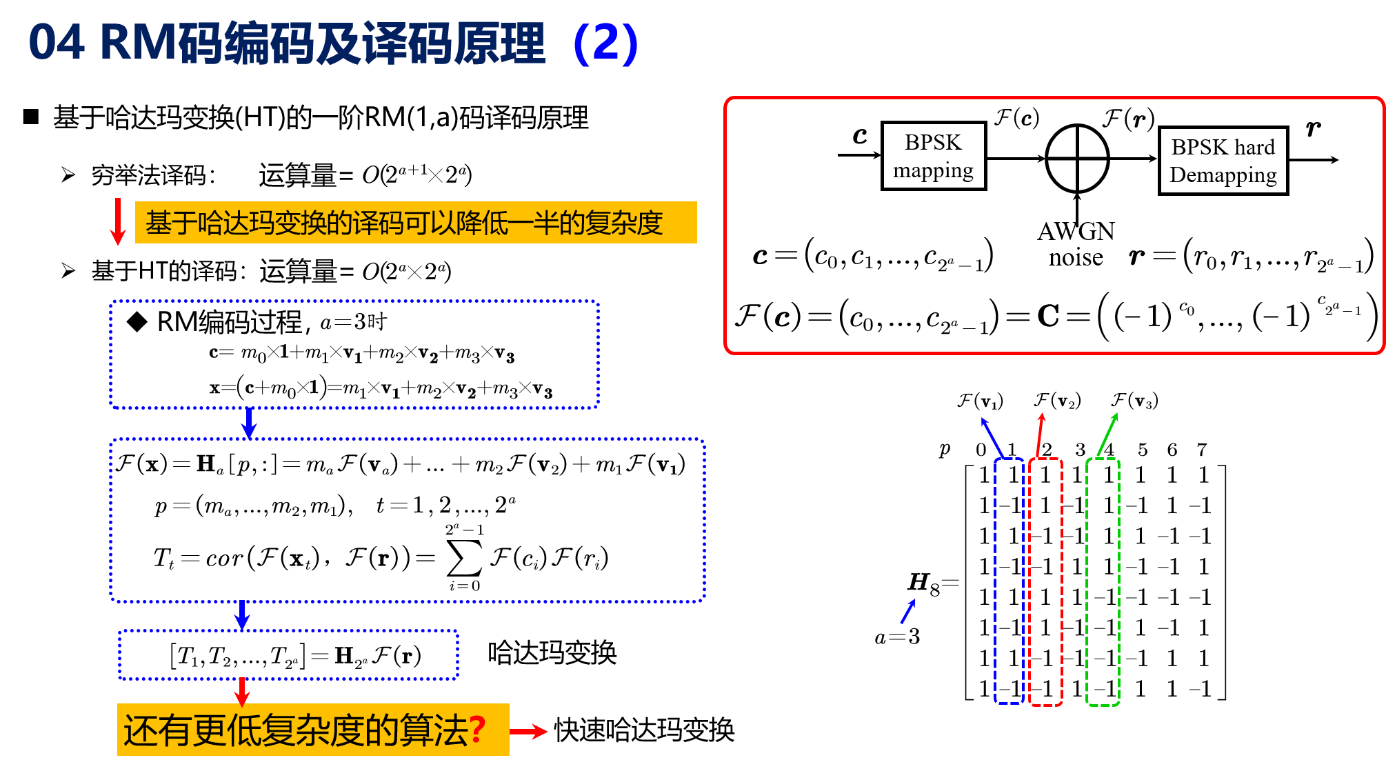

8.2.1符合5G标准的一阶RM码的编译码原理与仿真

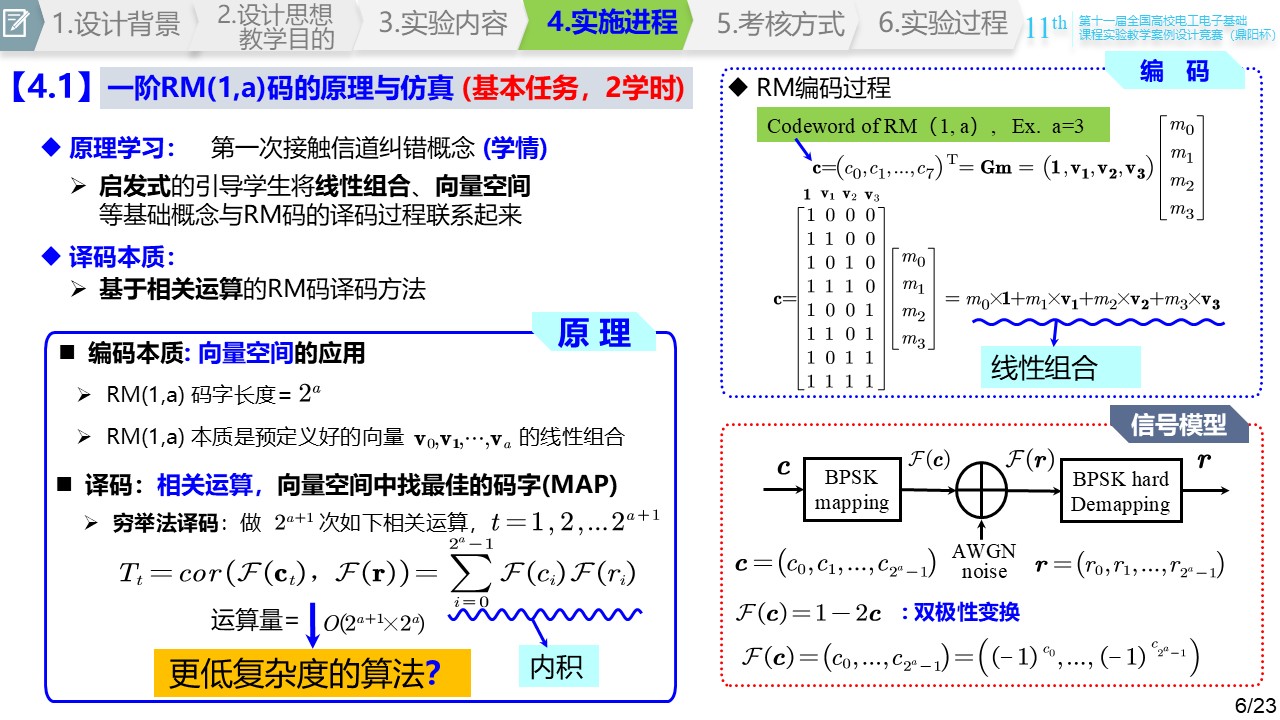

本案例是大二学生第一次接触到信道纠错的概念。因此,案例的第1个小任务是对5G RM码的基础,暨一阶Reed-Muller码原理的学习与仿真。结合星座映射的双极性变换特点,需要将《线性代数》课程中所学习到的线性组合、向量空间等基础概念与RM码的编译码过程联系起来,最后能够找到基于相关运算的Reed-Muller码译码方法。源于相关运算的RM译码原理,重点从复杂度角度分析RM码的三种译码算法的原理和设计,需要学会科学的分析它们的复杂度区别。三种译码器算法分别是基于穷举法的译码、基于哈达玛变换的译码、基于快速哈达玛变换的译码。根据复杂度分析的结果,引导学生能够选择快速哈达玛变换作为本次译码算法的实现方案。最后布置具体的Matlab仿真任务,并能得出具体的BER性能,并整理到总结报告中。

具体的任务要点有以下三个:

1)说明FHT降低复杂度的原因,并能理解FHT变换的架构;

2)基于FHT的符合5G标准的一阶RM编译码仿真;

3)仿真获得符合5G标准的一阶RM码的BER译码性能。

图8-2 基于穷举法的RM译码原理

图8-3 基于哈达玛变换的RM译码原理

图8-4 基于快速哈达玛变换的RM译码原理

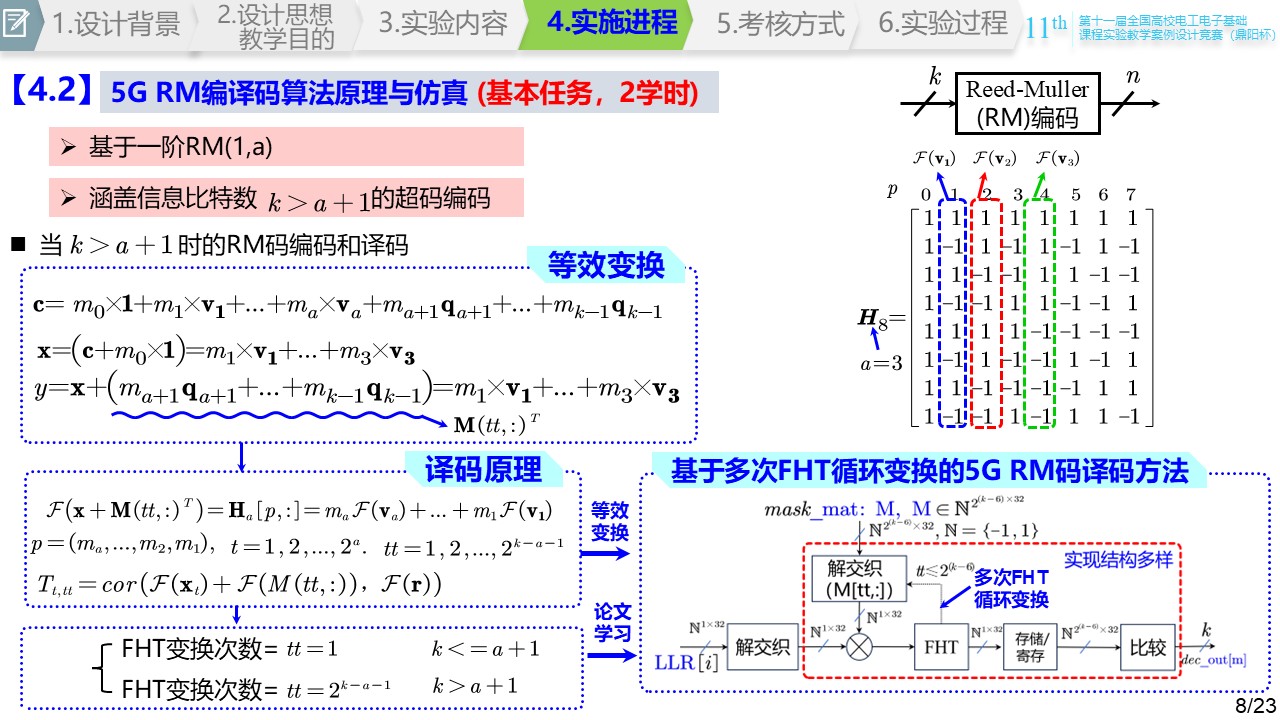

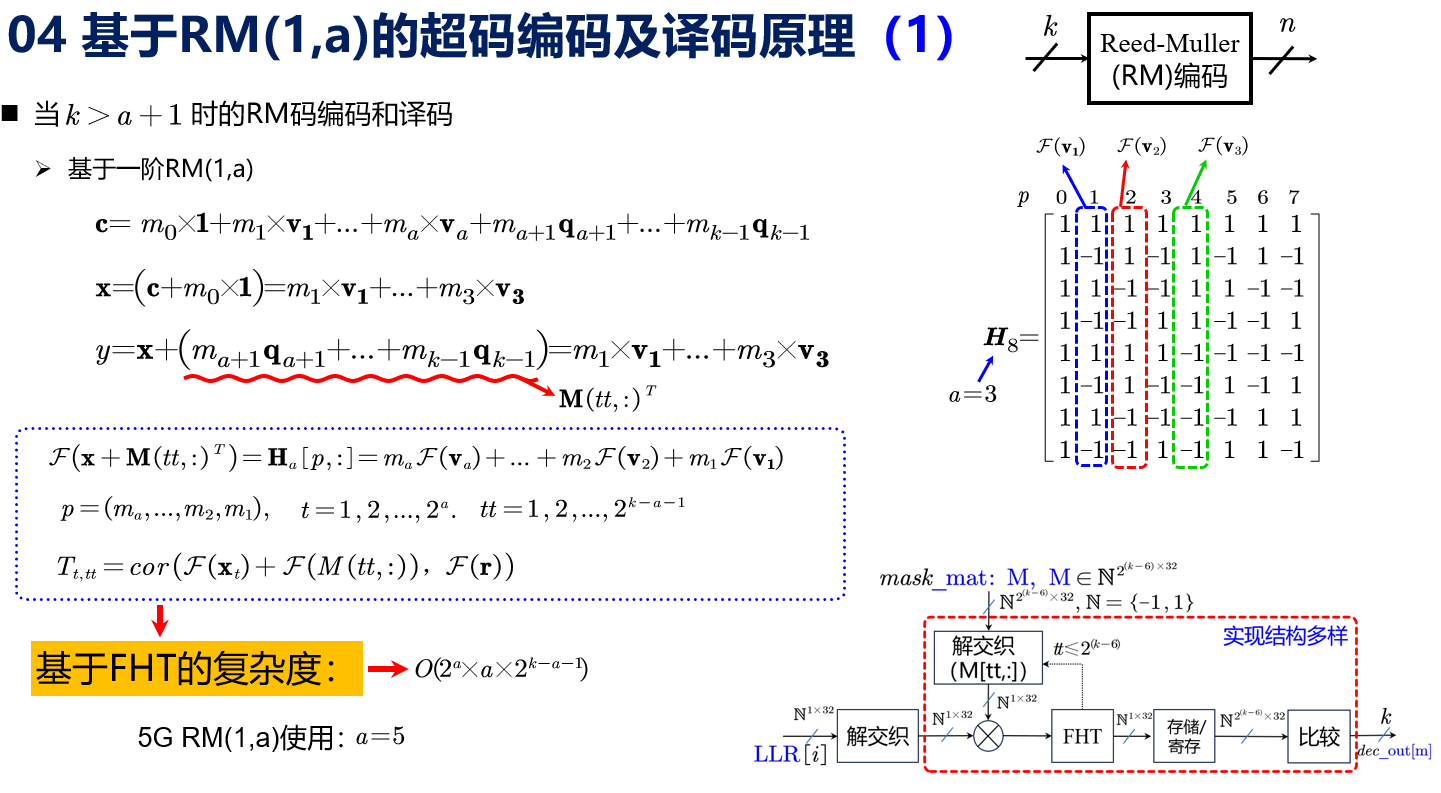

8.2.2 基于RM(1,a)的5G RM超码编译码原理与仿真

图8-5 基于掩码结构的RM编译码原理

5G

RM码的码长固定为 ,信息比特长度

,信息比特长度 在3~11比特之间。当信息比特长度小于等于6比特是,它是基于一阶

在3~11比特之间。当信息比特长度小于等于6比特是,它是基于一阶 码构造出来的。当

码构造出来的。当 时,它是基于

时,它是基于 的一种超码编码方式。对于一阶

的一种超码编码方式。对于一阶 码来说,只要做一次的FHT就能译码出结果。然而,当

码来说,只要做一次的FHT就能译码出结果。然而,当 时,FHT运行的次数需要等于

时,FHT运行的次数需要等于 。本任务需要理解基于多次FHT循环变换的5G

RM码译码结构,具体编码及译码原理如图8-5所示。

。本任务需要理解基于多次FHT循环变换的5G

RM码译码结构,具体编码及译码原理如图8-5所示。

具体的任务要点有以下三个:

1)基于RM(1,a)掩码结构的5G RM超码编译码算法和结构;

2)译码性能仿真和分析;

3)量化性能仿真,为译码器的数字系统实现提供译码器LLR信息输入提供量化依据。

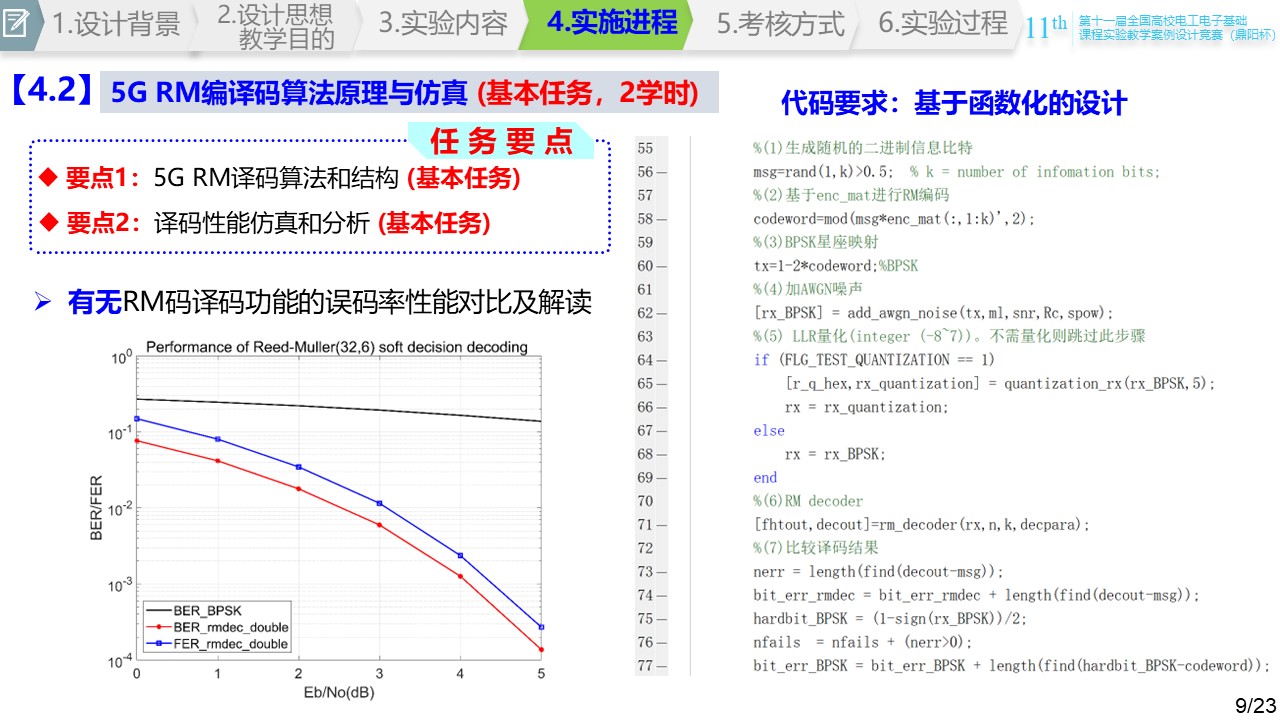

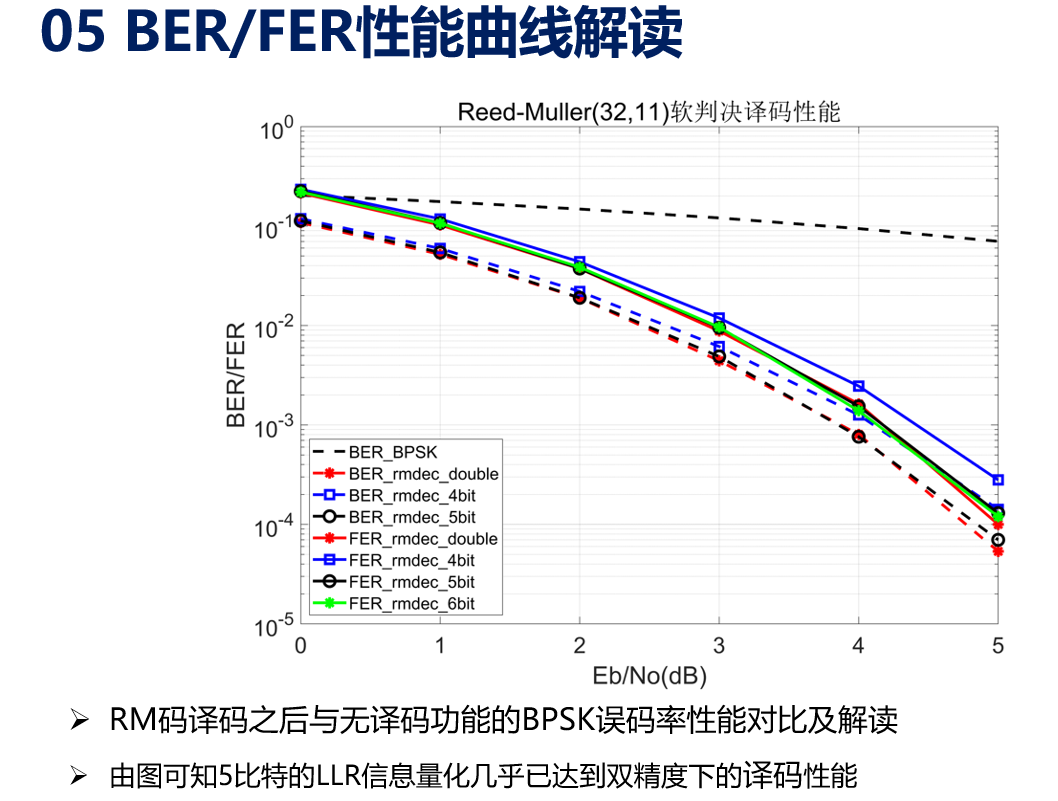

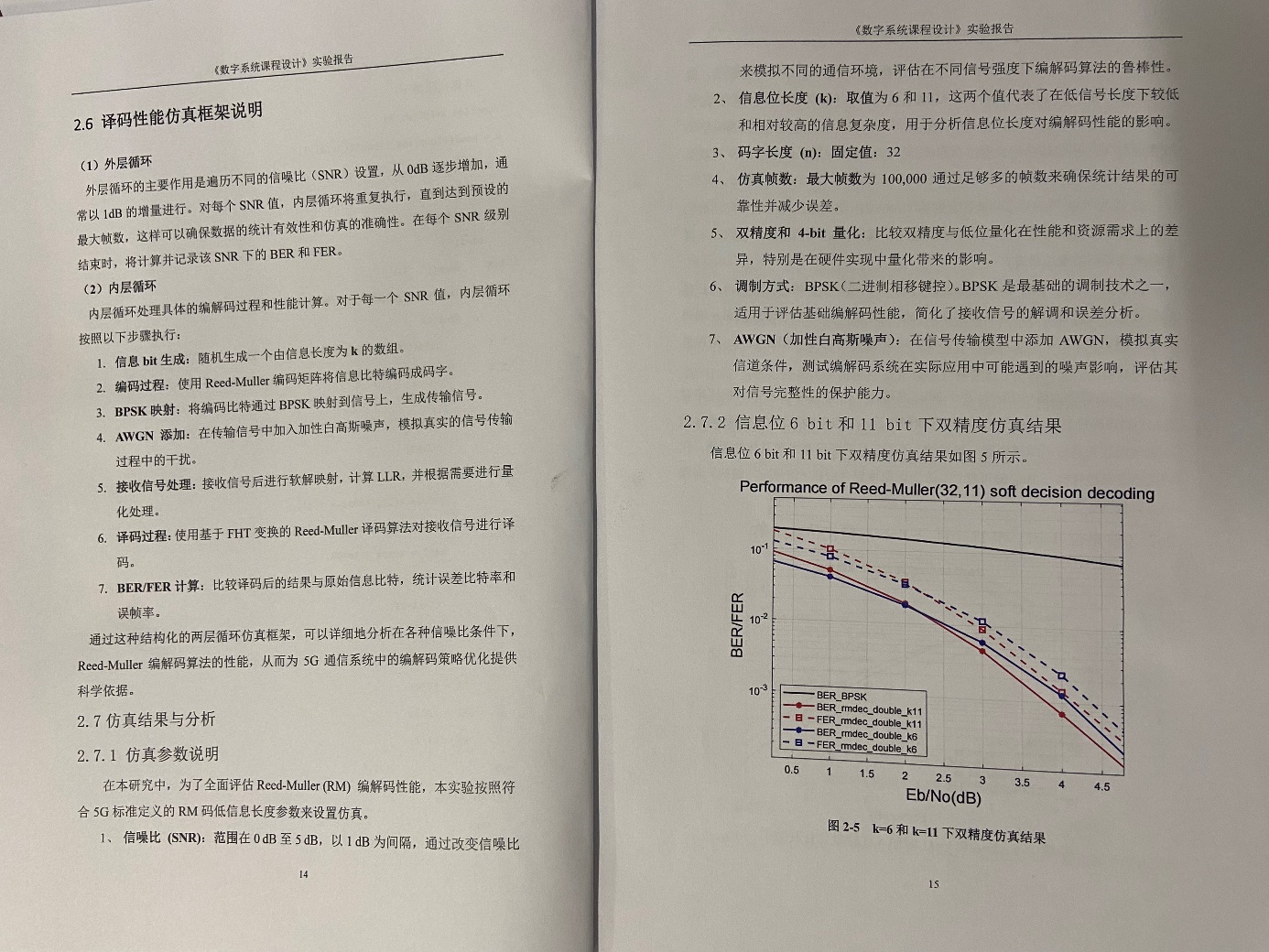

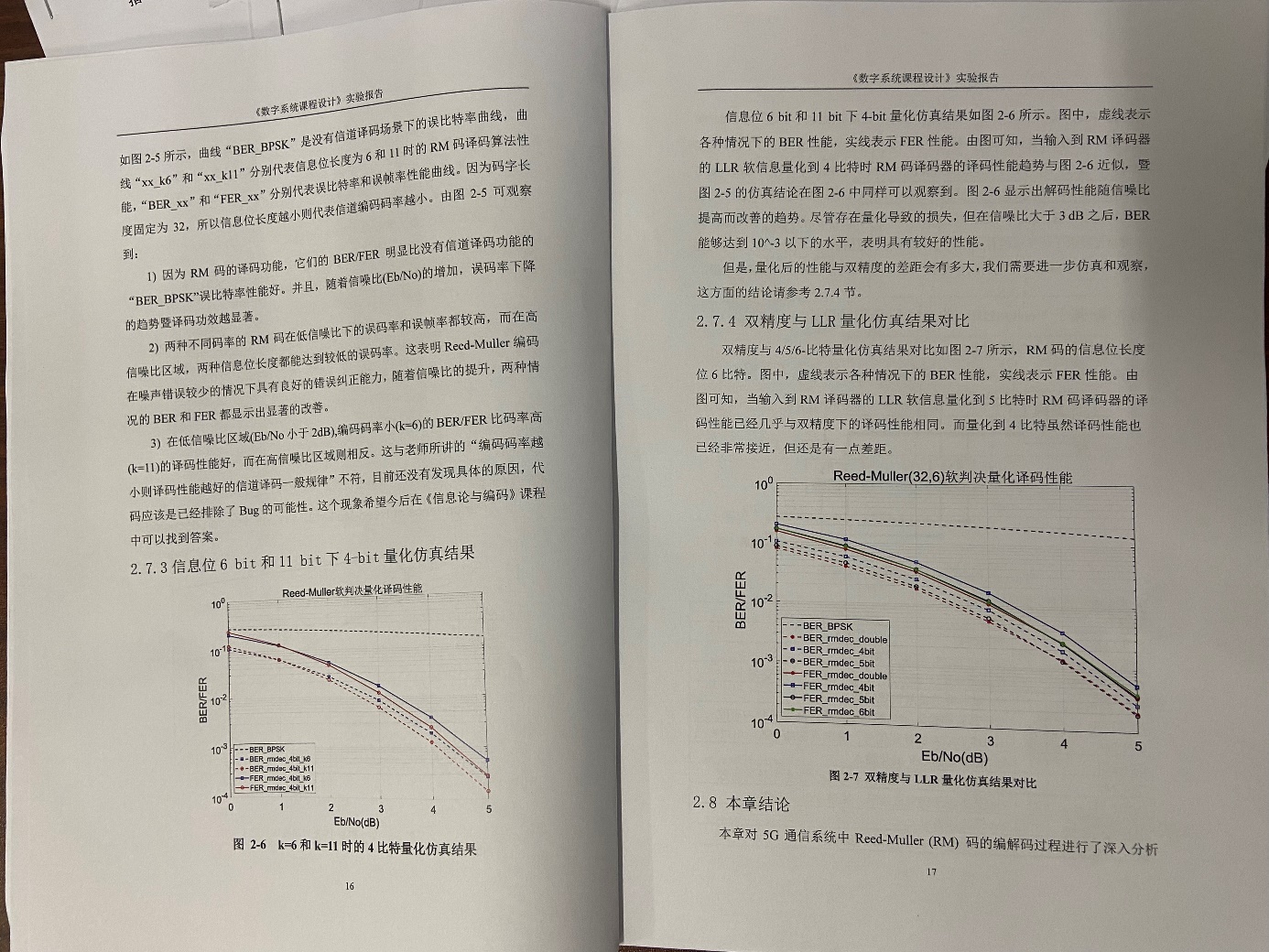

8.2.3 误码率特性仿真

对于信道编码来说,误码率主要可以从误比特率(BER)和误帧率(FER)的性能来衡量。BER/FER是验证信道编码方式及对应译码方式纠错能力非常重要的测试指标,阶段一要求学生给出如图8-6所示的误码率曲线,并能根据BER/FER性能曲线精确解读和评估信道编译码的译码性能。BER和FER的测试方法如图8-7所示。

图8-6 误码率性能示意图

图8-7 误码率仿真结构

- 阶段二任务:基于VerilogHDL的RM码译码器设计与测试

图8-8 阶段二电路实现总体结构

阶段二任务如图8-8所示。

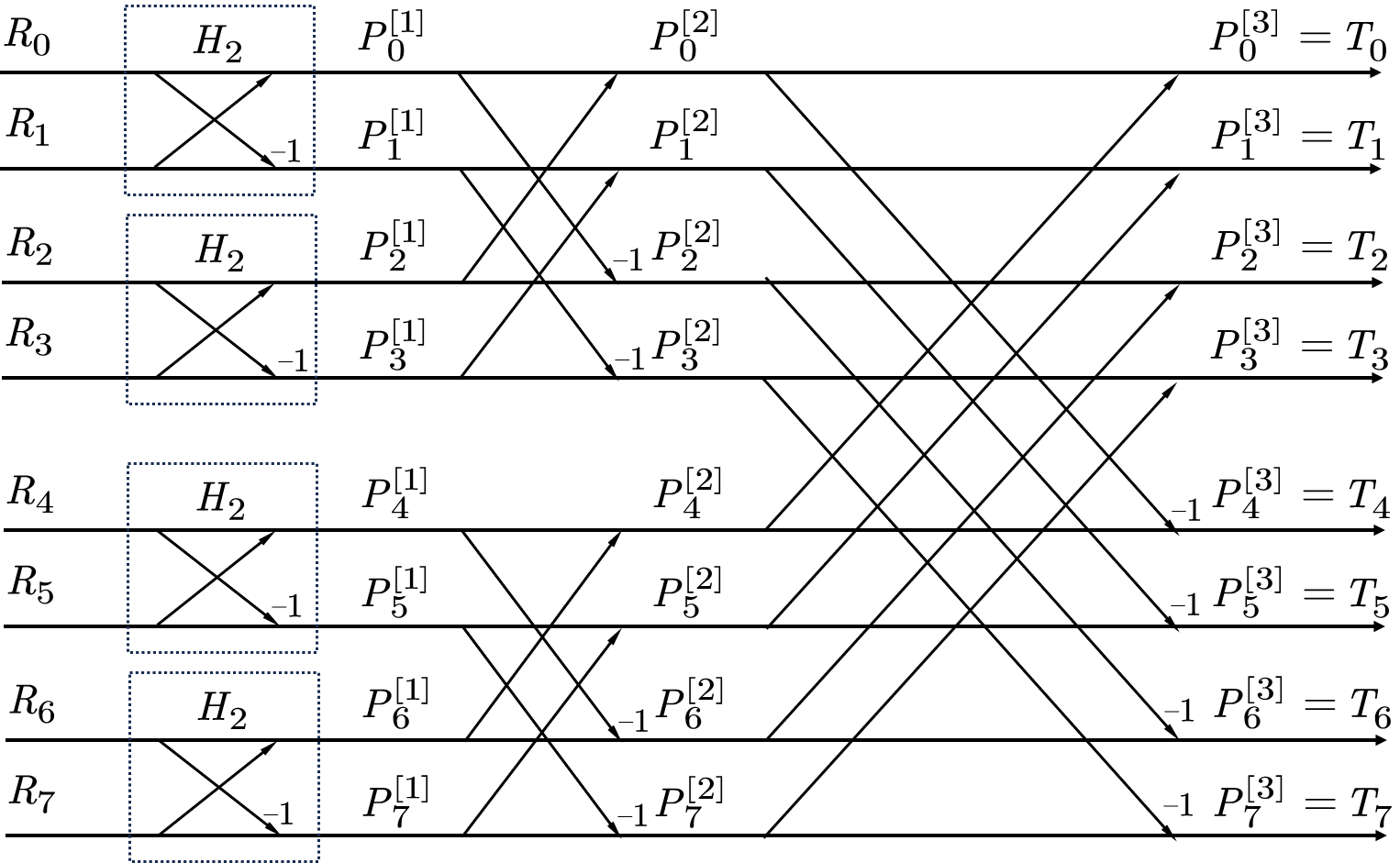

8.3.1 快速哈达玛变换模块的VerilogHDL设计及仿真调试

当信息比特长度 时,译码器需要经过多次FHT运算的循环才能得出最后的结果。因此,本项目依从易到难得原则开始设计。先设计FHT模块。FHT模块架构如图

所示,采样流水线的架构设计。具体实现时,数据的读取可以基于存储器或者寄存器的方式来实现。但考虑到5G系统得码长较短(

时,译码器需要经过多次FHT运算的循环才能得出最后的结果。因此,本项目依从易到难得原则开始设计。先设计FHT模块。FHT模块架构如图

所示,采样流水线的架构设计。具体实现时,数据的读取可以基于存储器或者寄存器的方式来实现。但考虑到5G系统得码长较短( ),从Latency以及实现难易程度考虑,建议采样基于寄存器的数据读取方式来实现。

),从Latency以及实现难易程度考虑,建议采样基于寄存器的数据读取方式来实现。

图8-9 FHT结构

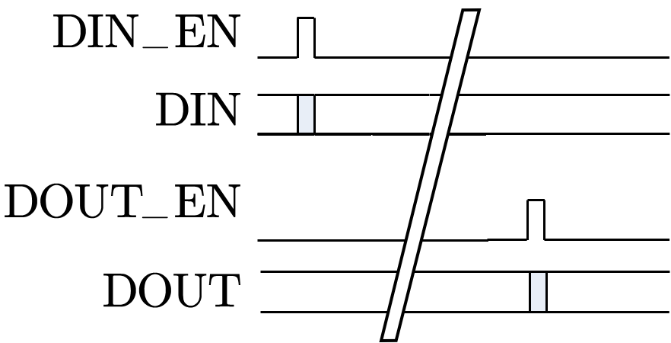

另外,从工程素养培训的角度,一定要注意API端口管理方面的实现问题,每个模块的输入输出的数据都建议配有对应的ENABLE信号,当ENABLE信号为高电平时表示对应的输入输出数据有效。比如,如下面所示的时序图一样:输入信号DIN配有DIN_EN, 而输出信号DOUT配有DOUT_EN。

图8-10 子模块API时序示意图

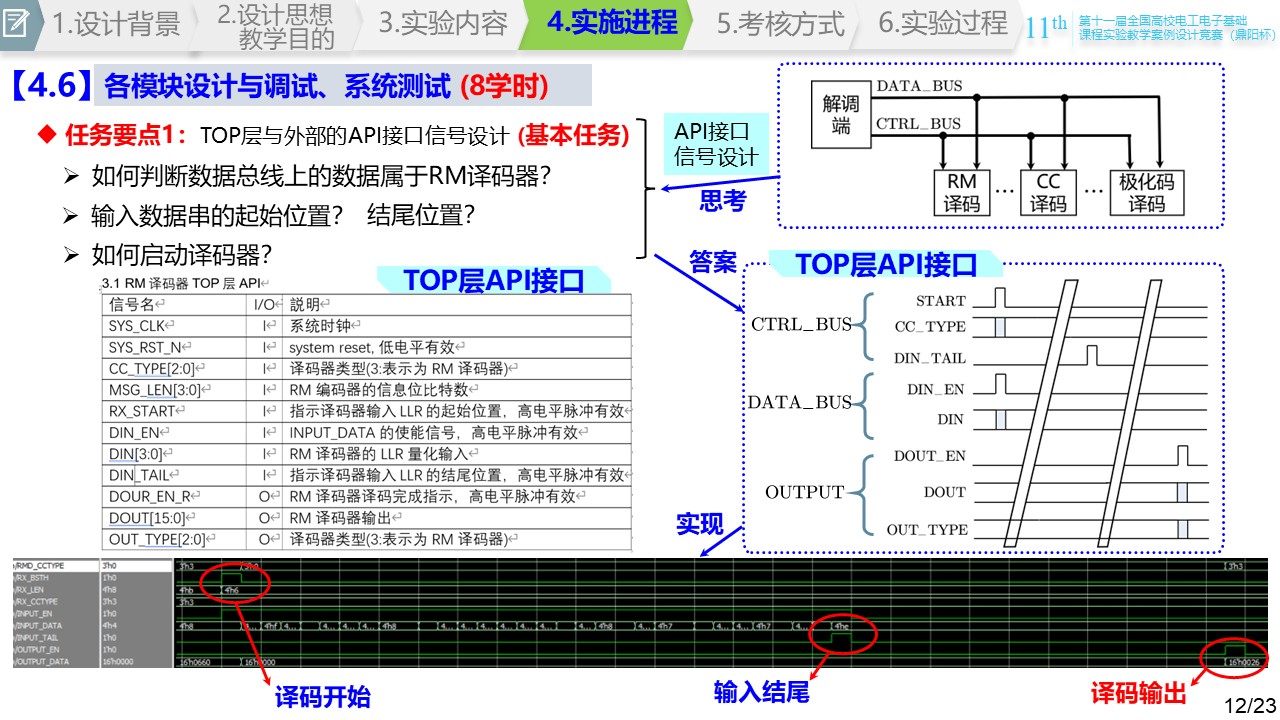

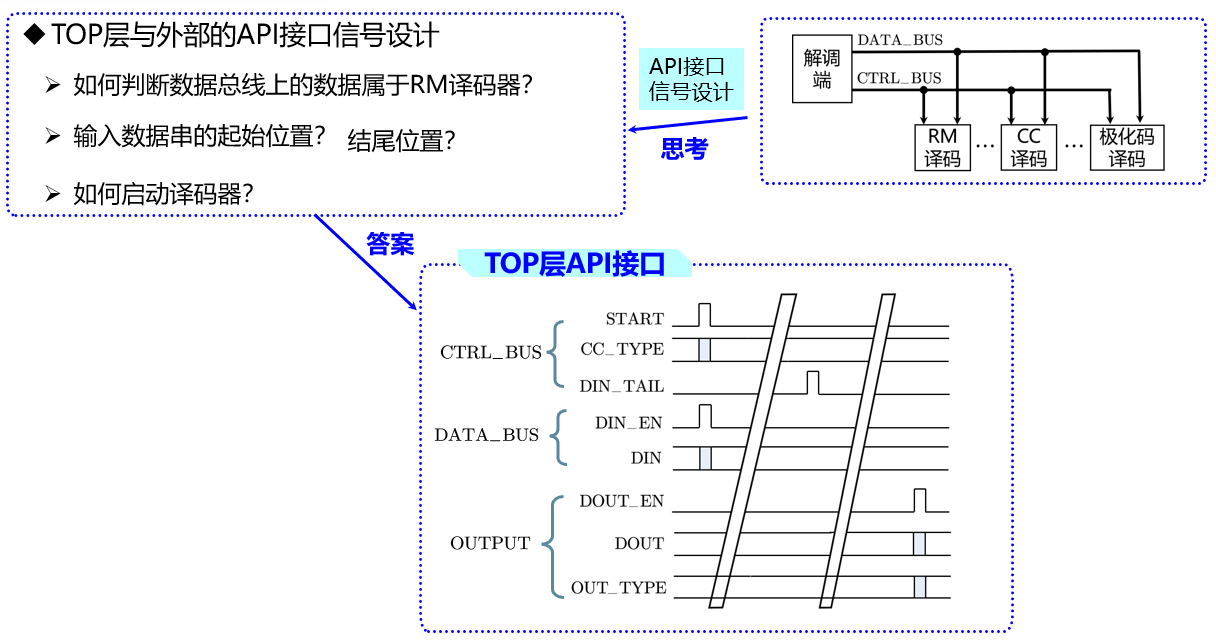

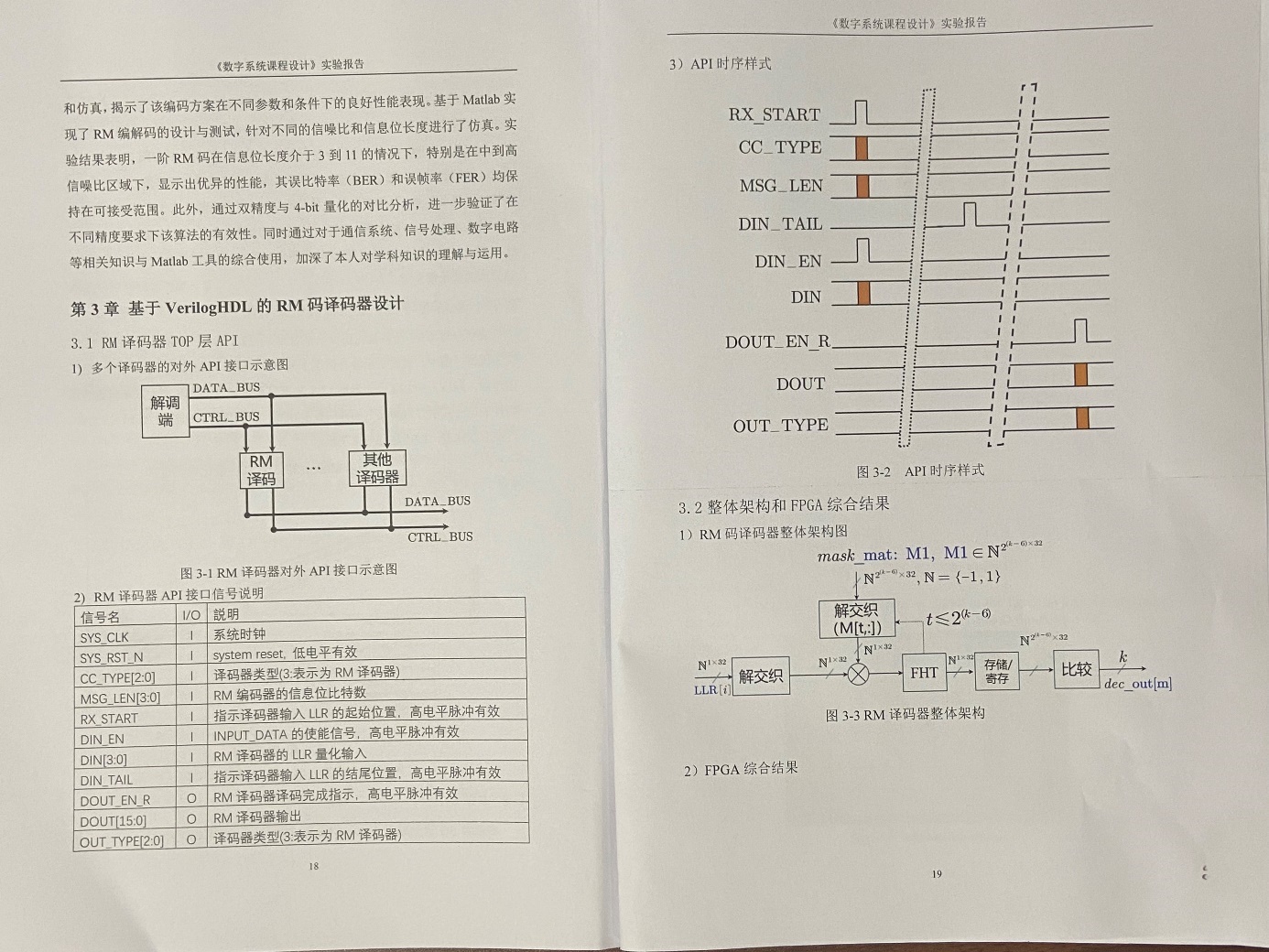

8.3.2 RM码TOP层与外部的API接口及时序设计

数字逻辑电路的整体架构设计首先遇到的问题就是它的TOP层与外部的API接口信号设计问题。项目结合5G上行控制信道的实际工程问题,引导学生如图8-11所示思考译码器与解调短的数据和控制总线设计,设计好几个需要同学们思考的问题,然后根据这些问题的答案设计出TOP层的API接口。

图8-11 TOP层API接口及时序设计

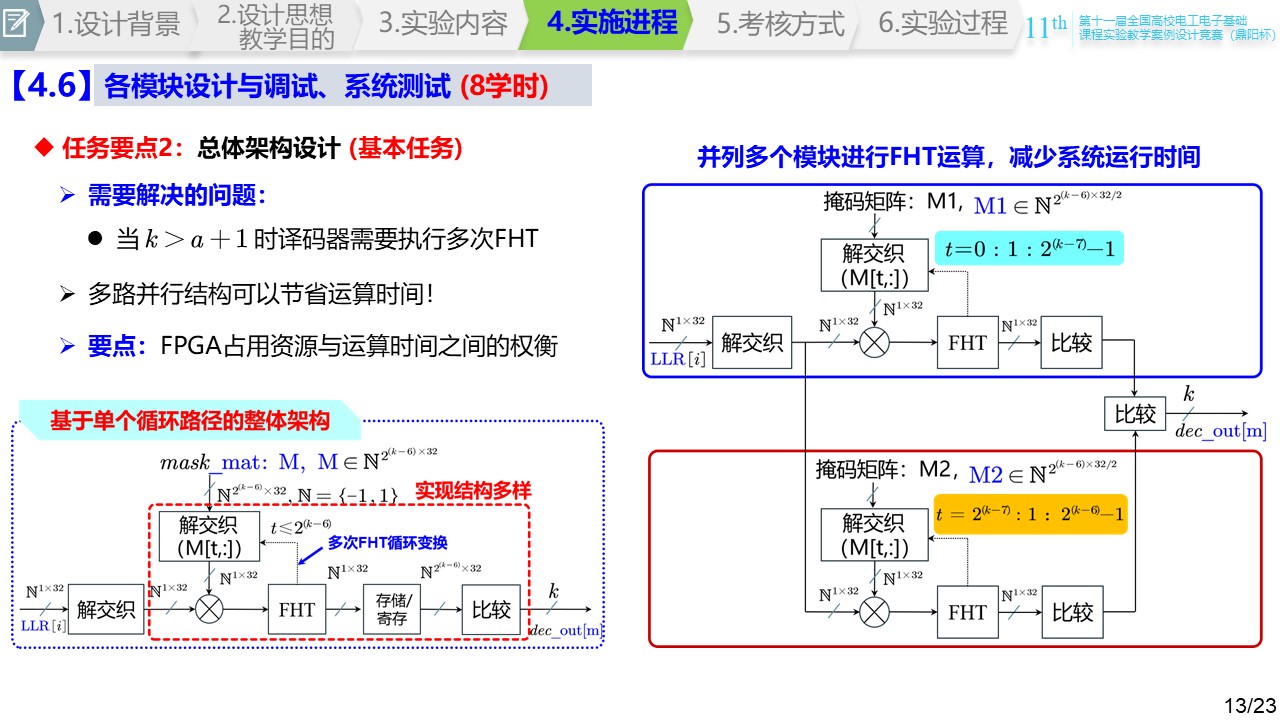

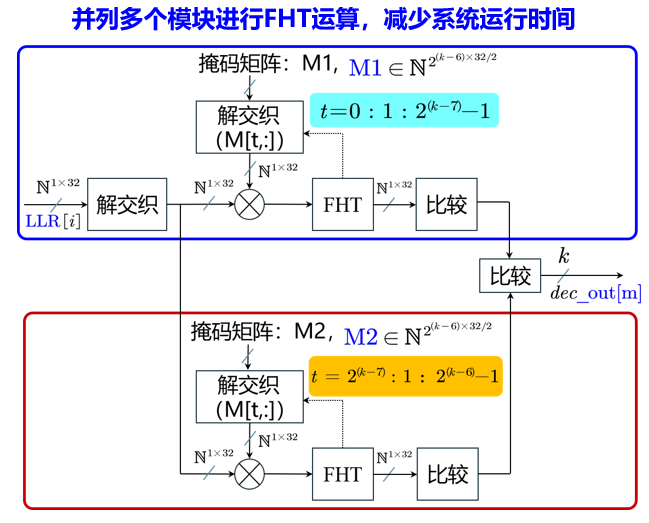

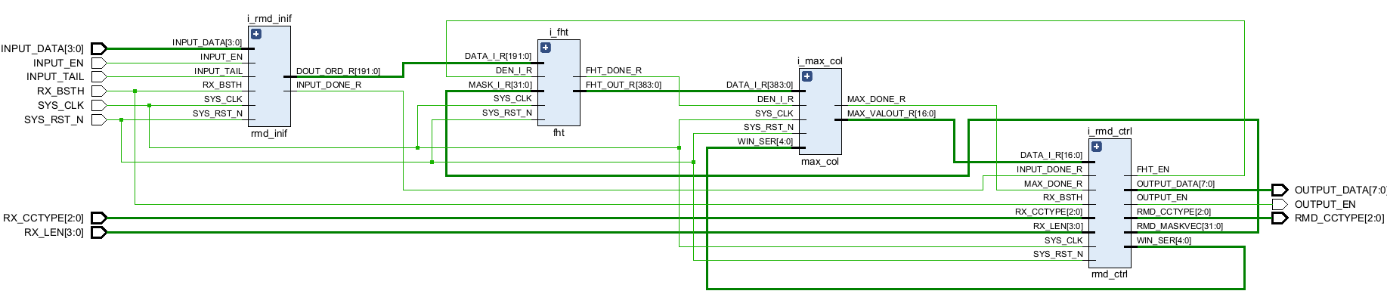

8.3.3 系统整体方案及各子模块的设计及调试

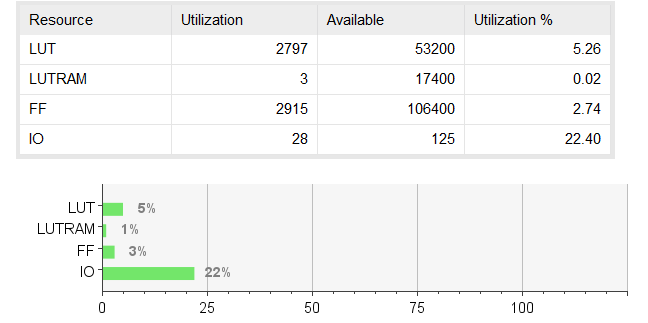

当 时,实现图8-8所示的RM译码,需要做多次FHT运算,在电路实现上结构方式可以多样。比如,可以采用图8-8所示的一个循环路径的方式,这样的架构占用的FPGA资源少,但是Latency相对长。也可以如图8-12所示的并列多个模块进行FHT运算,这样的架构占用FPGA资源多,但Latency可以做的更快。学生可以组内讨论自行决定采用什么样的方案,需要说明理由。并给出最后电路综合出来的FPGA资源占用及Latency之间权衡的分析结果。

时,实现图8-8所示的RM译码,需要做多次FHT运算,在电路实现上结构方式可以多样。比如,可以采用图8-8所示的一个循环路径的方式,这样的架构占用的FPGA资源少,但是Latency相对长。也可以如图8-12所示的并列多个模块进行FHT运算,这样的架构占用FPGA资源多,但Latency可以做的更快。学生可以组内讨论自行决定采用什么样的方案,需要说明理由。并给出最后电路综合出来的FPGA资源占用及Latency之间权衡的分析结果。

图8-12 并列多个模块的FHT运算的架构设计

8.3.4 良好的TestBench设计技巧和方法

良好的TestBench设计对于有效调试数字逻辑电路功能异常重要。在HDL的基础阶段学生习惯于使用基于时间延迟的激励信号生成方法来编写TestBench。我们会要求学生基于事件驱动的激励信号生成方法来进行testbench代码编写,如图8-13所示,完成各模块的功能调试。

图8-13 基于时间驱动的激励信号生成方法

8.3.5 融合Matlab对RM码译码器进行逻辑测试

RM译码器的输出结果组合非常多,有限的几次调试很难排除所设计的电路的Bug。 为此,借助第三方工具,比如Matlab参与输出结果的测试就非常重要和关键。作为扩展任务,理解融合Matlab对RM码译码器进行逻辑测试的必要性,并掌握进行复杂电路的仿真和测试等相关知识与技术方法。具体测试原理和方式如图8-14所示。

图8-14 融合Matlab的电路测试架构

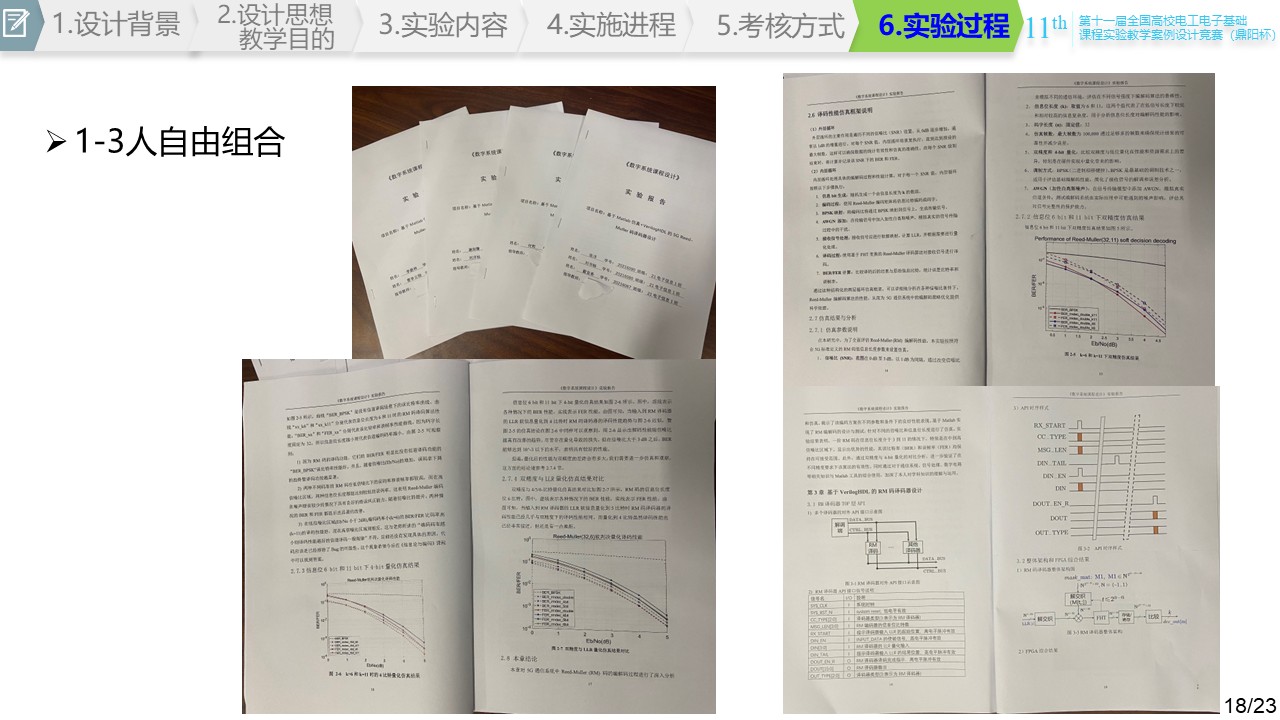

实验报告要求

实验报告整体分为Matlab仿真的总结报告以及VerilogHDL设计的技术文档报告两部分构成。实验报告内容教师给定建议的实验报告框架,具体章节安排可以由学生根据具体情况自由组织,但需涵括教师给定框架内的内容。教师给定的建议实验报告框架如下所示。

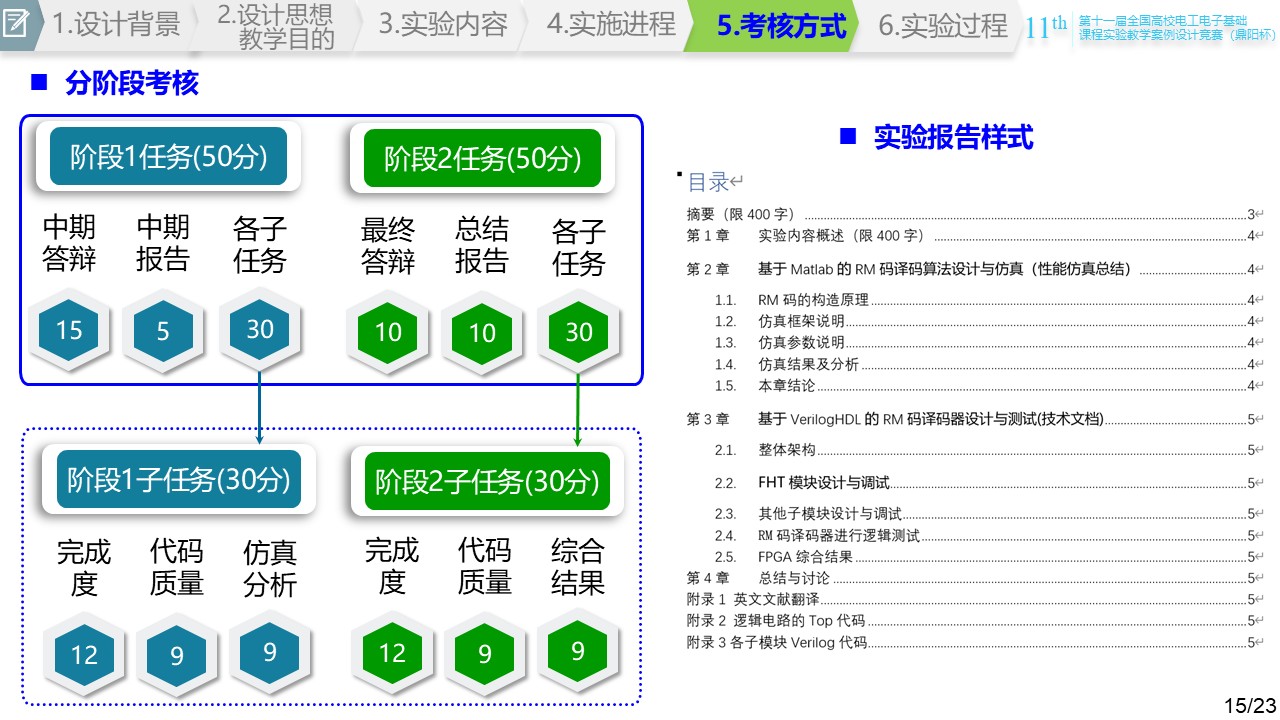

考核要求与方法(限300字)

10.1 项目总成绩构成

总成绩 = 阶段性任务1(50%)+ 阶段性任务2(50%)。其中,阶段性任务1的考核成绩= 中期答辩(30%/15分)+中期报告(10%/5分)+子任务(60%/30分); 阶段性任务2的考核成绩 = 最终答辩(20%/10分)+总结报告(20%/10分)+子任务(60%/30分) 。

10.2 报告成绩侧重点

中期报告和中期答辩侧重对RM译码算法原理讨论的科学性和逻辑性,以及译码算法性能仿真的正确性与讨论的理论逻辑性方面。最终答辩重在Verilog实现的工程性意识,以及逻辑综合的结果以及FPGA资源与电路Latency方面的讨论。总结报告重在Verilog电路实现上技术文档的规范性方面。

10.3 各个子任务的考察重点

完成度以及正确性方面。重在Verilog实现的工程性方面,以及逻辑综合的结果以及FPGA资源与电路Latency方面。

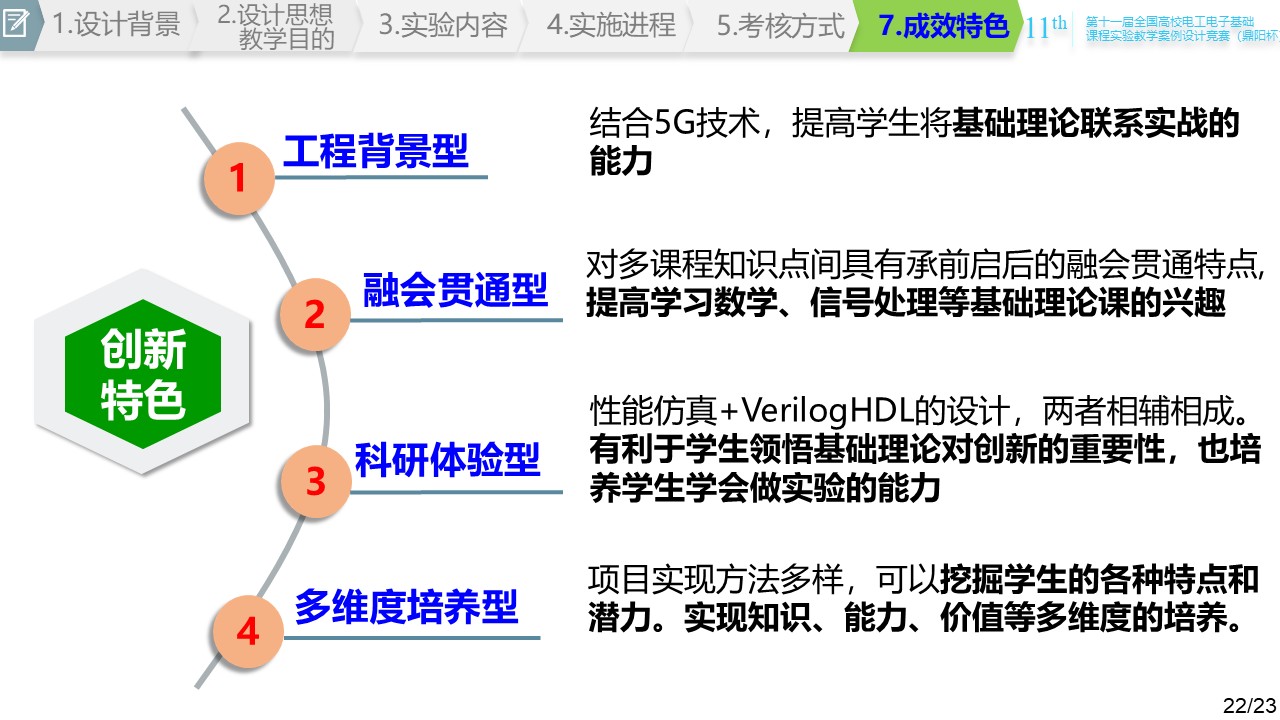

11.项目特色或创新(可空缺,限150字) {#项目特色或创新可空缺限150字}

本项目是一个完整的项目驱动型数字系统实践项目,特色和创新体现在以下几个方面:

**(1)工程背景强。**项目设计以数字系统工程项目开发流程为导向,案例本身结合了5G移动通信技术的一个工程实践项目,可以较好的培养学生将基础理论联系实际的能力,并提高了学习兴趣。

**(2)项目对多课程知识点间具有承上启下的融汇贯通特点。**项目需要性能仿真论证,又需要VerilogHDL的设计,两者间相辅相成。算法原理的研究和理解上需要用到线性代数的知识点。RM码本身属于《信息论》课程中的一个信道编码方式,通过本案例的实践过程,学生对将要学习的《数字信号处理》、《信息论》等课程的知识产生浓厚的学习兴趣。

**(3)项目实现方法多样,可以挖掘学生的各种特点和潜力,培养团队协作精神。**仿真方面,项目提出了不同的性能仿真要求。电路实现方面,译码器的实现架构多样。

附件1:教学大纲

《数字系统课程设计》课程教学大纲

执笔人 :[ XXX]{.underline} 专业负责人:

编写日期:XXXX年 [XX]{.underline} 月 分管院领导:

课程名称:数字系统课程设计 课程编号: 英文名称:Digital System Curriculum Design 课程类型:必修 授课学院:XXXX 学分学时:1.5学分,20学时 教学方式:课堂讲授为辅,学生实践为主 考核方式:全程考核 |

课程简介、内容、基本要求及学时分配: 一、课程简介 《数字系统课程设计》实验是电类专业的一门重要的专业基础实验课程。它以数字系统工程项目开发流程为导向,将基于Matlab的算法仿真、与基于Verilog HDL的数字系统设计的学习与提高相融合。结合5G移动通信技术的一个工程案例,提高了学生学习兴趣。同时学生需要运用向量线性组合、相关运算等数学基础理论理解RM码译码算法原理。要求学生掌握Verilog HDL进行数字系统实现时的模块间API端口管理、有符号定点数处理、以及融合Matlab产生测试向量进行复杂电路的仿真调试和测试等相关知识与技术方法。最终引导学生对将要学习的《数字信号处理》、《信息论》等课程的知识产生浓厚的学习兴趣。该课程的目的是: 1)培养学生综合运用《线性代数》基础理论、Matlab进行算法设计和科学分析;运用数字电路等课程的基础知识进行数字系统综合设计和系统测试的工程能力。 2)达到对学生的“知识层面”和“能力层面”的培养,引导学生学会做实验。 3)达到对学生“价值层面”的培养,切身理解基础理论与工程创新相互融合的关系,切身体会我国20年来在通信领域特别是5G通信系统方面为国际做出的巨大贡献。 二、理论教学内容及学时分配 理论授课20学时。本课程是一个案例型实验教学方式,整个实验过程需要完成两个阶段性的任务,如下图所示。

第1章 基于一阶RM码的5G RM编译码原理讲解(2学时) 1.1信道编译码基本概念 1.2一阶RM(1,m)码编码及其译码原理 1.3介绍并演示本项目的内容与要求 1.4关键点1:基于线性组合视角的编码方式,以及基于哈达玛变换(实质是接收向量与哈达玛矩阵的相关运算)的RM码译码原理 1.5关键点2:教师带写并演示完成一阶RM码的编译码仿真框架的构建 第2章 基于一阶RM码掩码结构的5G RM超码编码方式及其译码原理(2学时) 2.1根据作业完成情况重点讲解核心关键点 2.2 FHT变换基本原理讲解 2.3基于掩码结构的5G RM超码编码及译码原理 2.4关键点1:当RM码的编码信息k大于m时的超码编码方式,及其对应的译码原理的理解。 2.5完成掩码矩阵的生成代码的编写 第3章 5G RM码编码方式及其译码原理(2学时) 3.1根据作业完成情况重点讲解核心关键点 3.2任务:使用Matlab评估RM译码算法在信息量化时的纠错性能 3.3围绕BER性能与信息量化时的tradeoff展开评估 3.4完成阶段1任务,并整理好阶段一的文档总结 第4章 快速哈达玛变换模块的VerilogHDL设计及仿真调试(2学时) 4.1 根据作业完成情况重点讲解核心关键点 4.2 讲授基于RAM以及基于寄存器的FHT实现架构上的优缺点。作为本案例单独的公共模块,推荐学生基于寄存器架构来实现FHT变换。 4.3 演示基于VerilogHDL的模块设计以及testbench的代码艺术,模块间API端口管理、有符号数处理等。 4.4 师生互助+学生自主编码模式下完成FHT的模块设计和仿真调试 第5章 中期答辩及整体方案讲解(2学时) 5.1 中期答辩及点评 5.2 教师讲授:FPGA实现时资源占用率及运行效率视域下的整体实现方案讨论 5.3 以共性问题提出中期总结报告的修改意见 第6章 完成各子模块的设计及调试(8学时) 6.1 组内讨论+学生自主编码,完成各子模块的设计与调试 6.2 教师对共性问题进行解答 6.3 教师讲授:融合Matlab对RM码译码器进行逻辑测试的重要性及实现思路与方法 第7章 总结答辩(2学时) 7.1分组演讲答辩及点评 7.2检查总结报告的问题点并提出修改意见 三、考核方式及成绩评定 总成绩 = 阶段性任务1(50%)+ 阶段性任务2(50%)。其中,阶段性任务1的考核成绩= 中期答辩(30%)+中期报告(10%)+子任务(60%); 阶段性任务2的考核成绩 = 答辩(20%)+总结报告(20%)+子任务(60%) |

参考资料: [1] 王宇尧.5G NR短码编译码算法研究及FPGA实现[J].信息化研究,2020,46(04):52-61. |

[2] 陈发堂,何坚龙.LTE系统中Reed-Muller码的编译码算法[J].重庆邮电大学学报(自然科学版),2010,22(04):395-399+410. [3] 5G标准38.212, 自制讲义。 |

附件2:实验报告

**

附件3:FPGA综合结果**

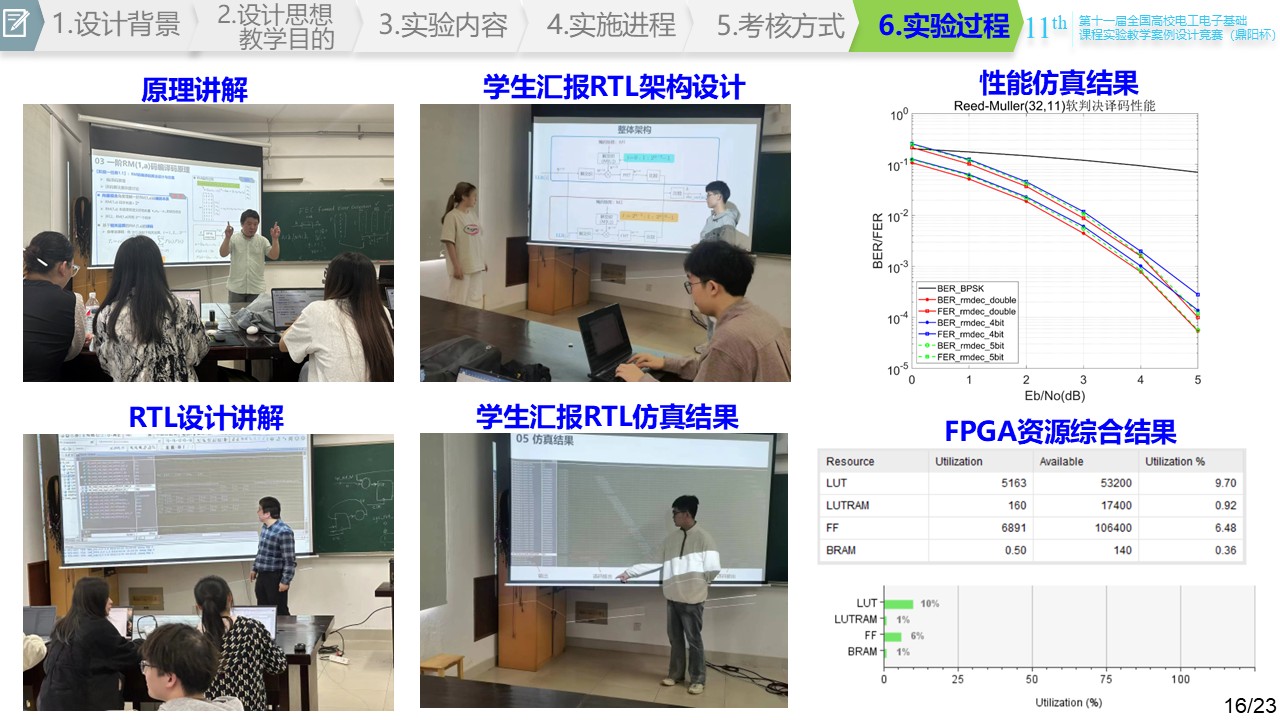

附件4:实验教学现场

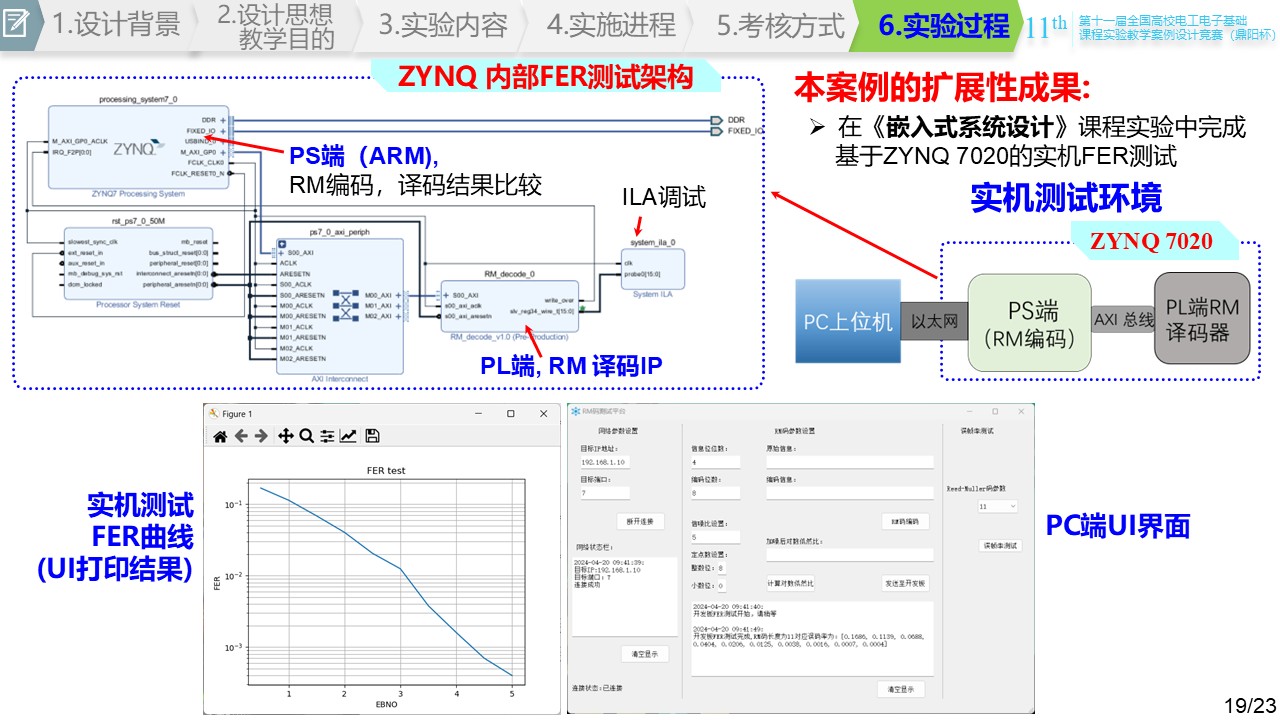

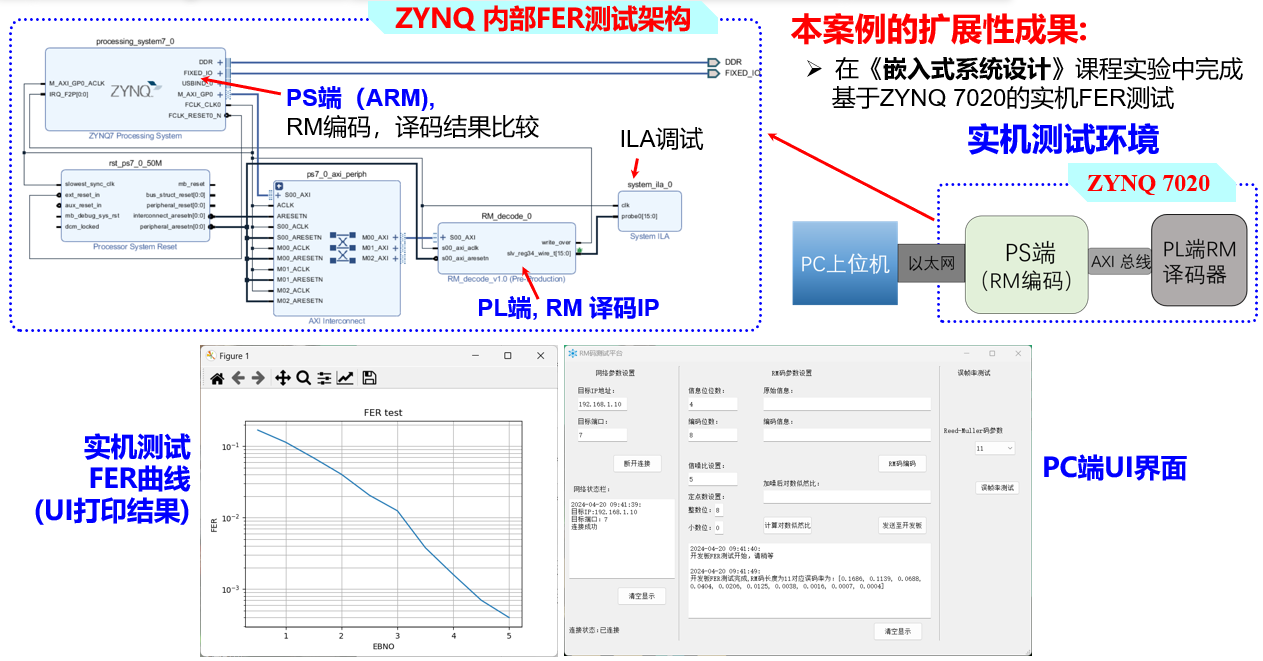

附件5:同学期开设的《嵌入式系统设计》实验课中实现的本项目RTL电路实机测试

作为本案例的可扩展性成果,我们团队又在同学期开设的《嵌入式系统设计》实验课中,将本项目的RTL设计成果在ZYNQ 7020上进行了实机测试。ZYNQ的PS部分承担RM编码和译码结果计算,FPGA实现本项目的RM译码IP。ZYNQ的PS端将测试所获得的误帧率译码性能,通过以太网上传到PC机的UI界面显示。

附件5-1

附件5-2