基于PLD的交通灯系统逐层优化设计实验

课程名称:数字逻辑电路

实验题目:基于PLD的交通灯系统逐层优化设计实验

课程简要信息

课程名称:《数字逻辑电路》

课程学时:讲课56学时,实验16学时(本实验为最后4学时)

适用专业:信息专业、自动化专业、电子专业、微电子专业、计算机专业

学生年级:大二第二学期或大三第一学期

实验内容与任务(限500字)

-

在Quartus软件中学习交通灯工程示例,工程原型已经在课堂讲过,分析软件中该工程的错误在哪里。

-

改正错误,使软件中的工程与课堂中的交通灯运转一致。

-

优化交通灯设计,使用更少的逻辑资源实现系统。

-

讲解实际电路应用中对模型需进行的改动,并让学生自己完成这些改动,在开发板上实现出来。

实验过程及要求(限300字)

-

在实验step1中,让学生将工程与课堂讲授的交通灯进行对照,寻找差异;引导学生在仿真中沿时间轴观察电路输入到中间信号再到输出的逻辑因果关系,查找错误;鼓励相互讨论。

-

在实验step2中,要求学生不能进行组间讨论,只能自己解决错误问题。解决问题后,举手让老师检查。

-

在实验step3中,引导学生充分考虑计数器的描述方式,引导学生修改状态机的转换条件。

-

在实验step4中,让学生自由发挥进行设计,老师只负责解决编译错误和程序下载问题。

-

提出实验报告要求,引导学生将实验报告不是看成任务,而是进一步的学习过程。

相关知识及背景(限150字)

相关知识:这个实验涉及到简单数字系统的控制单元和信息处理单元的设计及通信方法,通过仿真查找问题的方法,电路优化的方法,异步复位、时钟管理、输入同步等概念和应用。

学生知识背景:在课堂上教学中,通过框图、逻辑流程图、ASM图完成了交通灯模型。学生已学习VHDL语言的基本语法,可以实现基本电路模块。

教学目标与目的(限100字)

(1)学习数字系统中控制单元和信息处理单元的基本设计方法。

(2)区分何时该用组合逻辑,何时该用时序逻辑。

(3)正确地认识和掌握仿真。

(4)了解模型与电路实用的差异,实用电路需要考虑很多问题。

教学设计与引导

本实验的过程是一环扣一环的循序渐进的设计创新过程,需要经历发现问题、分析问题、改正错误、设计优化、电路实用化、系统调试、设计总结等过程。因为课堂已经讲授过基本的交通灯模型,所以学生很熟悉,不用在实验中过多涉及理论。在实验教学中,应在以下几个方面加强对学生的引导:

1)在step1讲解状态机和计数器的代码时,要注意将PPT和电路图进行对照,使学生能在清晰的引导下进行代码学习。

2)在step1仿真过程中,先让学生自由仿真一会儿,再提示要注意激励信号的输入方法,不同的变化规律会导致可能发现不了问题或者很难发现问题,应按照由简单到复杂情况的顺序进行仿真。

3)在step2改正错误的过程中,要允许学生发散思维,只要能得到正确的结果就行。然后假设黄灯的时间只有1秒钟,通过集中讨论,使学生发现必须从根本上解决问题才行,从而回归正途。

4)在step3优化电路设计的过程中,鼓励学生创新设计,不论用什么样的描述方法,新手只要能实现对应功能就值得赞扬,激发他们的斗志和创新力。

5)在step4环节,要引导学生注意编译错误,注意管脚约束,注意爱惜开发板。教师要在这个环节着力于解决学生编译中遇到的问题。只要编译能通过,其他的疏忽让他们自己调试解决。

6)在实验完成后,总结本实验的目的和学到的东西。

7)在每个环节的验收过程中,要鼓励学生新奇的想法而不是排斥其中有瑕疵的意见。

实验原理及方案

1)实验模型(课堂讲授)

例:设计一个十字路口交通灯控制系统。

设:东西道(EW)为主道,南北道(NS)为副道。

若EW及NS均有车,则EW每次通行60秒(绿灯),NS每次通行40秒(绿灯),EW、NS轮流放行;

若仅有一个通道有车,则禁止无车通道(红灯);

若两通道均无车,则NS禁止,EW 放行;

若通道转换时,两通道均需停车3秒(黄灯)。

课堂上根据题目要求,定义输入输出和内部变量,如表6-1所示。

表6-1 变量定义

| 监测器送入 | 定时器 | 定时器进位输出 | 定时器使能输入 | 输出灯光信号 |

|---|---|---|---|---|

NSCAR (由NT、ST生成) EWCAR (由ET、WT生成) |

TIMER60 TIMER40 TIMER3 |

TM60 TM40 TM3 |

ENTM60 ENTM40 ENTM3 |

NSRED NSGREEN NSYELLOW EWRED EWGREEN EWYELLOW |

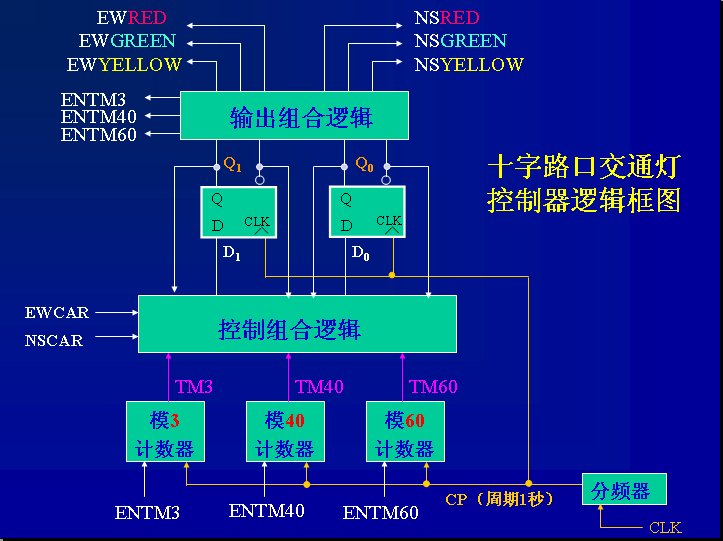

再通过框图,逻辑流程图,ASM图的设计流程,设计出状态机两个触发器组成的控制电路的组合逻辑表达式,并完成交通灯控制器的逻辑框图,如图6-1所示。

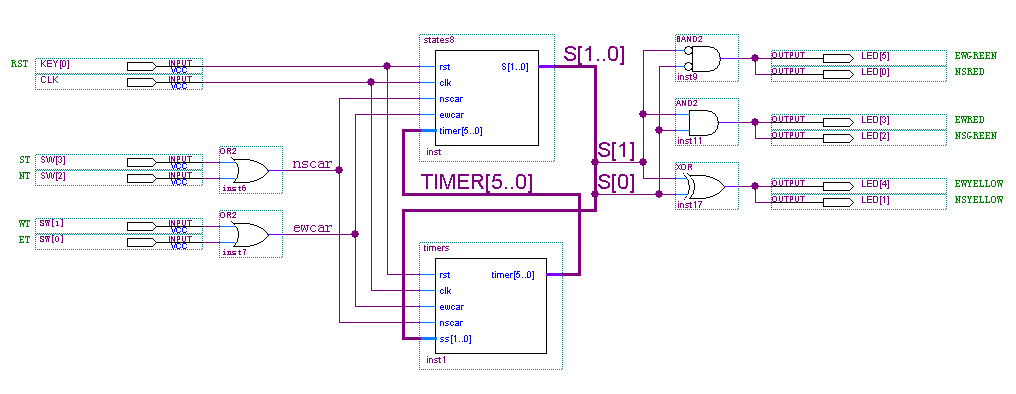

图6-1 课堂讲授的交通灯模型

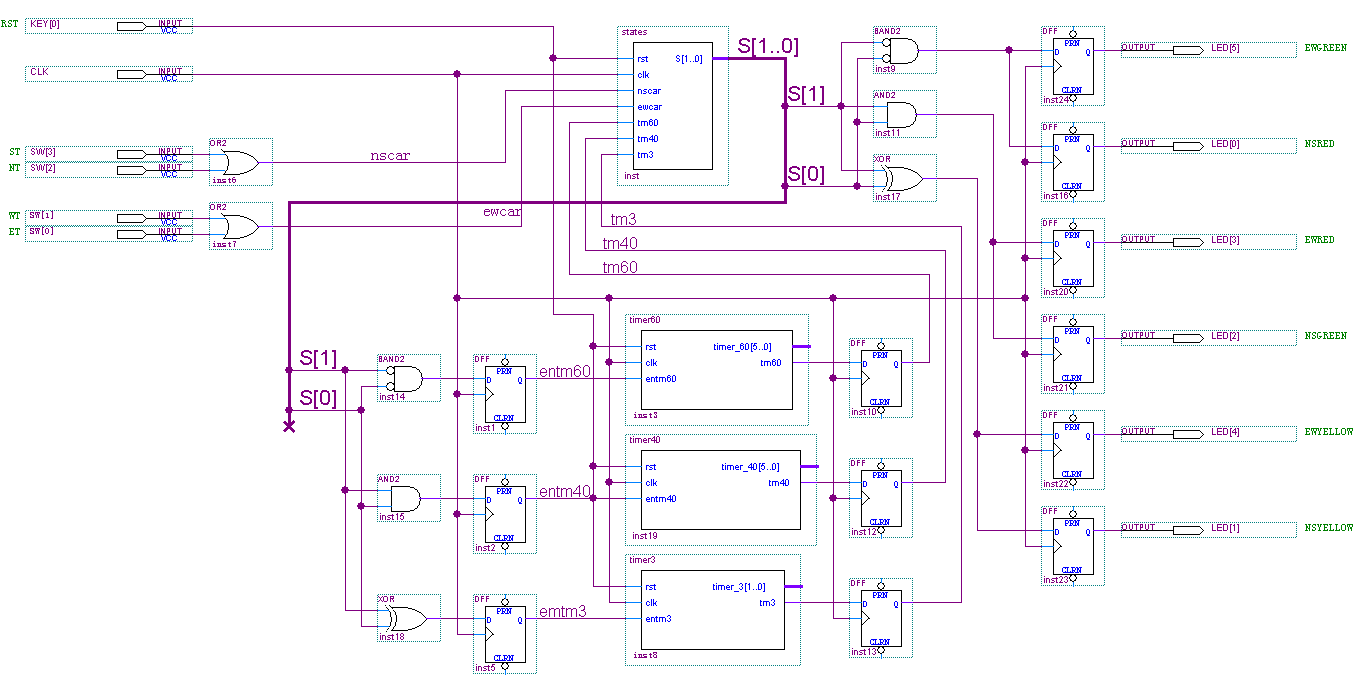

2)初始工程示例及查找错误(step1)

图6-2 初始工程示例图

实验以图6-2的工程开始进行,状态机输出的三个计数使能,计数器的三个溢出信号和状态控制的6个灯都通过触发器延迟实现,导致状态转换时多出2秒,状态转换后灯的变化延迟1秒。通过仿真,学生会了解到仿真的重要性和仿真的基本方法。

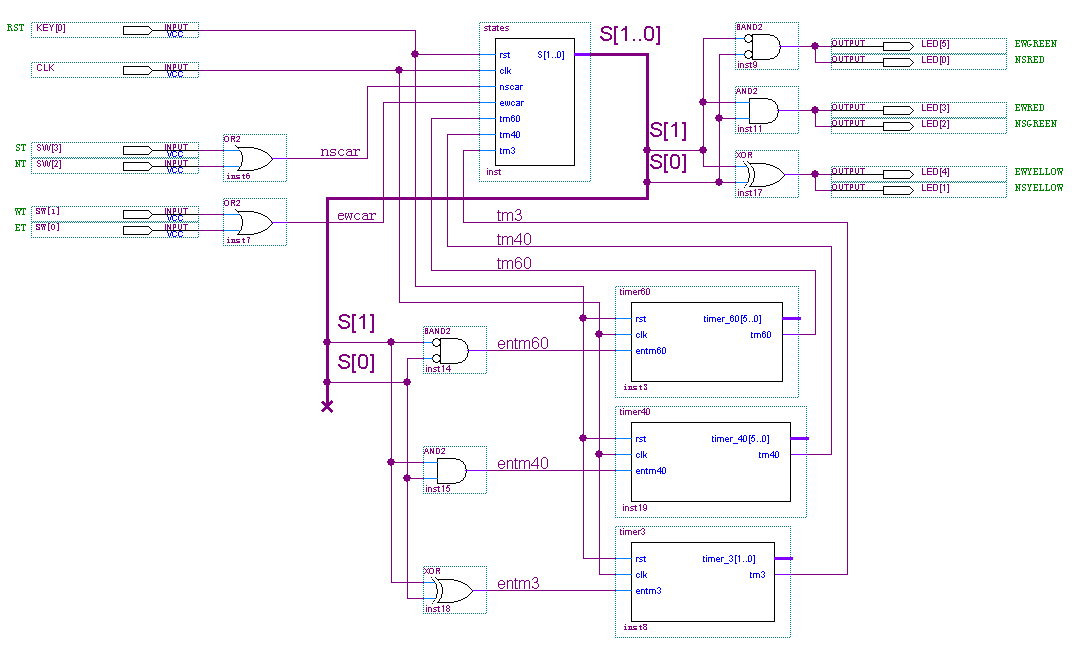

2)改正错误(step2)

同学们经过仿真发现延迟问题,将多出的12个触发器删除,如图6-3所示,成为与课堂上相同的交通灯。

通过这个步骤,学生思维发散,又能在老师的引导下统一认识。清楚意识到逻辑电路中插入时序单元会造成电路按时钟周期延时。

图6-3 改错后工程示例图

3)设计优化(step3)

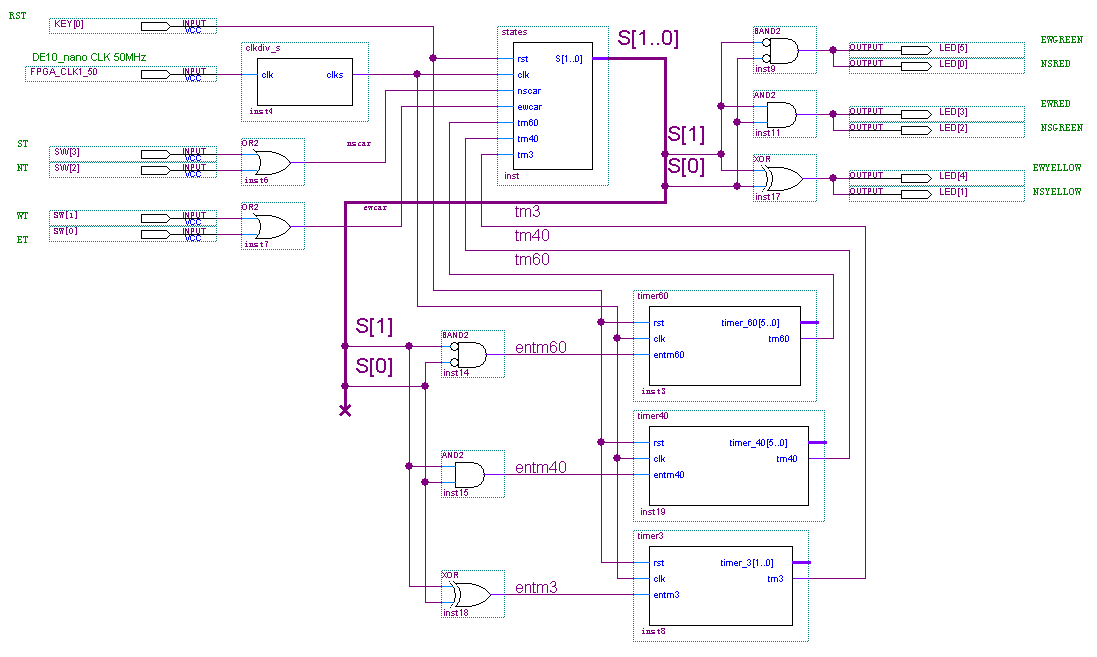

这个步骤进行电路优化,将3个计数器合并为1个。经过计数器合并,16个触发器变为只用了8个触发器,如图6-4所示。通过这个步骤,学生会非常高兴,因为优化掉了1半的资源。同时,学生也学习掌握了用VHDL语言描述计数器的基本规律和技巧,学习了状态机的描述方法。

图6-4 优化后工程示例图

4)实用设计(step4)

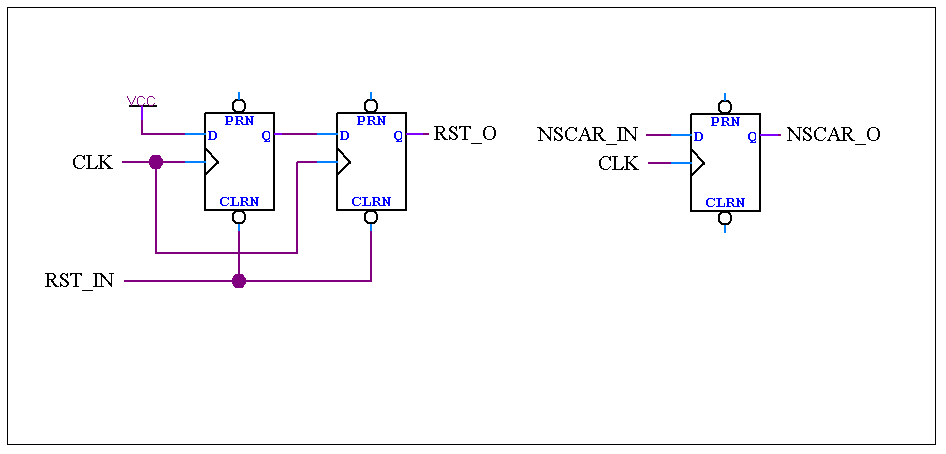

如图6-5所示,讲解异步复位同步释放的原理和重要性;讲解输入同步的原理和重要性;讲解时钟选择和分频使用的原理和重要性。

图6-5 异步复位和输入同步示意图

异步复位同步释放,输入同步都可以使系统外用户输入信号满足同步时序电路内触发器的建立保持时间,从而保持系统的稳定正常运行。

- 系统调试

表6-2 信号对照表

| 输入 | 输出 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 信号名 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| DE10_Nano |

|

|

|

|

|

|

|

|

|

|

|

|

|

图6-6 De10_nano初始工程示例图

step4目录中只存放如表6-2和图6-6所示的优化前完整工程示例,包含管脚约束,可直接下载。最终的下载工程由学生根据这个模版自由设计完成。

将工程文件按每一步分别存放在step1~step4目录下,使学生上一步的设计差异不会影响到下一步,但也允许学生按照自己的创意继续下一步设计。

教学实施进程

step1:(50分钟)

(1)让学生打开Quartus Prime软件,打开/lab/tlight/step1/tlight工程,打开tlight28.bdf。

(2)让学生将PPT放在屏幕一侧,软件放在屏幕另一侧,对照描述代码。

(3)展示课堂讲过的交通灯的例子,展示电路框图。

(4)展示用Quartus II 软件图形界面设计的交通灯。沿着输入到输出的顺序给学生讲解电路结构图。

(5)讲解状态机代码,向学生显示状态机描述与设计目标一致。提醒学生状态机的编码方式使用的是格雷码。

(6)讲解Counter60 代码,让学生看到 tm60 信号的产生。

(7)简要讲解counter40 代码和counter3 代码。

(8)讲解三个使能信号的D触发器产生方式,与电路图进行对照。

(9)讲解三个进位信号的D触发器产生方式,与电路图进行对照。

(10)讲解6个输出信号的D触发器产生方式。

(11)给学生10分钟的时间自己对照电路图,继续熟悉代码。

(12)让学生重新观察电路图有什么不对的地方,从经验看学生难以发现问题。

(13)带领学生进行编译,注意观察占用了28个D触发器。

(14)带领学生进行仿真。交给大家仿真的简单方法,不是一次仿真复杂情况,而是从最简单的情况开始,进行多次仿真。

(15)让学生自己找到仿真出现的两拍延时。

(16)展示黄灯状态时间段的仿真波形,学生首先会发现黄灯持续了5 拍,然后开始找原因。

(17)引导学生从计数器的值等于59 的时钟上升沿时开始记节拍。沿着“计数器59--计数器进位--状态转换到黄灯--3 秒计数器使能--计数器加到1--计数器加到2--3 秒计数器进位--状态转换到南北通行”一拍一拍地看。学生会发现多出来的两拍是由于计数器没有直接推动状态变换和状态变换没有直接推动计数器计数造成的。

step2:(40分钟)

(18)让学生打开Quartus Prime软件,打开/lab/tlight/step2/tlight工程,打开tlight28.bdf。对照电路图,学生会发现是由于加入了2 组触发器造成的。

(19)让学生自己修改代码,电路恢复到删除两组触发器,自己编译和仿真,直到实现正确的电路功能。这个过程可能会拖课时较长时间。有的学生会通过减少计数器的模来缩短时间,先允许他们这样自由设计,完成后再让他们思索如果黄灯原来规定只亮两秒,那么他们的做法就不行了,从而引导他们回到正确的修改路径上。

(20)引导学生得出时序电路的插入会引起电路延迟,认识到时序与组合逻辑在时间上的不同。

(21)通过时钟最高频率和门最大扇出的概念使学生感受到引入时序电路的对组合逻辑电路的分隔会提高系统性能。

step3:(60分钟)

(22)让学生打开Quartus Prime软件,打开/lab/tlight/step3/tlight工程,打开tlight16.bdf,寻找最简电路设计。通过将三个计数器合并,得到最简电路设计。

(23)让学生在设计中不止要注意计数器的变化,由于计数器变化了,状态机也需要随之变化。step3会花相当的时间,部分没完成的学生在实验后继续完成该设计修改。

step4:(90分钟)

(24)让学生打开Quartus Prime软件,打开/lab/tlight/step4/tlight工程,打开tlight8.bdf(工程中的三合一计数器timer内容是空的,防止学生在step3中钻空子)。最简电路看起来很完美,但是电路模型存在问题,以此吸引学生的注意力,

延伸出课程随后要讲解的四个问题:异步复位方法,时钟分频,输入同步,输出同步。

(25)板书异步复位,同步释放的电路图。让学生抄下,并让学生课后自己用VHDL代码设计,进行功能和时序仿真,验证该电路功能。

(26)讲解时钟分频,提出常用的时钟晶体频率,让学生知道晶体频率不是什么频率都可以方便得到的。对交通灯,使用32768Hz就足够了。另一方面,频率越高,则分频次数越多。但对当前的PLD器件而言,时钟频率在20~50M是没有问题的,因为资源很多。

(27)与学生讨论检测是否有车在路口附近的传感器送给数字系统的问题。直接以秒为节拍间隔过长,因为车辆每秒钟会运动数十米,使用高频时钟进行检测就好多了。同时,应对输入信号用高频时钟进行采样,事实是一个输入同步的过程。经过输入同步的信号,满足各个触发器的建立保持时间,不会出现异步问题。

(28)让学生打开Quartus Prime软件,打开/lab/tlight/step4/tlight工程,打开tlight_bd.bdf。这个工程是没有优化,但是能直接下载运行的交通灯工程。让学生自由设计,将复位电路,输入同步电路和优化后的计数器等模块加入系统,并在开发板上进行调试。

(29)提出实验报告要求,实验报告会在教学QQ群中统一发送。同学们不要将实验报告当成负担,而是通过查找文献,回答问题进一步学习和巩固知识。

实验报告要求

实验报告需要反映以下工作:

-

总结实验4个环节自己进行的工作。

-

提出实验结果进一步改进的方向。

-

要求学生实验报告不超过2页A4纸或实验报告纸,节省纸张。不允许机打,只能手写。

-

回答两个实验问题:问题一:请根据实验中复位电路图写出对应VHDL代码。

问题二:请将交通灯的状态机SS用两段式代码重写。

考核要求与方法(限300字)

1)实验过程验收(80%):按照实验的4个环节独立记分。按时完成每个环节,均获得20分。

2)实验奖惩:对提前完成每个实验环节的前10%的学生,给予每次5%的加分。对实验中做与实验无关事情的同学,给予每次10%的扣分。

3)自主创新:在实验各个环节中,提出的解决方案合理并较一般方案更优,给予5%加分。

4)实验报告(10%):实验报告的规范性与完整性,学生需要在实验报告中整理归纳实验收获,并回答实验结束后提出的问题,使实验报告变成一个课后学习的过程。

5)总分计算:实验总分超过100分时,按100分计。大多数学生能完成基本流程,得到80~95分;少数实验完成不好的学生,会得到80分以下的分数;10%~20%的学生可能得到95分以上。

项目特色或创新(可空缺,限150字)

项目的特色在于:项目背景的工程性,知识应用的综合性,实现方法的多样性。

1)趣味性:实验步骤层层嵌套,一山更比一山高,激发学生的兴趣与挑战意愿。

2)实用性:从模型到可操作的控制电路,使学生掌握实际PLD电路设计的几个要点。

3)创新性:在实验各个环节中,不给学生设定答案,激发学生的创造力。

4)综合性:本实验从软件使用到系统调试,涵盖了数字系统中的完整设计流程。

参赛选手信息表

| 案例提供单位 | 西安交通大学 | 相关专业 | 信息工程 | |||

|---|---|---|---|---|---|---|

| 设计者姓名 | 符均 | 电子邮箱 | Ts4@mail.xjtu.edu.cn | |||

| 移动电话 | 18992858095 | 通讯地址 (含邮编) |

陕西省西安市碑林区咸宁西路28号西安交大电信学院西一楼803室(710049) | |||

| 设计者姓名 | 王萍 | 电子邮箱 | Ping.fu@mail.xjtu.edu.cn | |||

| 移动电话 | 13289214336 | 通讯地址 (含邮编) |

陕西省西安市碑林区咸宁西路28号西安交大电信学院西一楼(710049) | |||

| 设计者姓名 | 张翠翠 | 电子邮箱 | zhangcuicui@mail.xjtu.edu.cn | |||

| 移动电话 | 13772160954 | 通讯地址 (含邮编) |

陕西省西安市碑林区咸宁西路28号西安交大电信学院西一楼(710049) | |||

| 相关x课程名称 | 数字逻辑电路 | 学生年级 | 2 | 学时(课内+课外) | 72 | |

支撑 条件 |

仪器设备 | 友晶DE10_Nano开发套件 | ||||

| 软件工具 | Quartus软件包 | |||||

| 主要器件 | Intel FPGA Cyclone® V SE 5CSEBA6U23I7N (110K LEs) | |||||