基于内嵌Cortex-M3内核FPGA的等精度频率计设计

实验题目:基于内嵌 Cortex-M3内核 FPGA的等精度频率计设计

1. 课程简要信息

课程名称:SoPC 系统设计,课程学时:56,适用专业:电子信息科学与技术、电子信息工程,学生年级:大三

2. 实验内容与任务(限 500 字)

项目需要完成的任务(如需要观察的现象,分析某种现象的成因、需要解决的问题等);是否设计有不同层次的任务。

1) 利用 SOPC 技术,以内嵌 ARM Cortex-M3 内核的 FPGA 芯片为控制核心,利用 Verilog 硬件描述语言对 FPGA模块进行设计,利用C语言对 Cortex-M3内核部分的程序进行设计,并借助 AHB 接口的 FIFO 实现 FPGA 与 Cortex-M3 内核之间的数据通信,完成等精度频率计的设计,可以实现频率测量和占空比测量功能;

2) 测量频率范围为 $1 \mathrm { H z } { \sim } 5 0 \mathrm { M H z }$ ,测量相对误差的绝对值不大于 $1 0 ^ { - 4 }$ ;

3) 测量脉冲信号占空比时,被测信号为矩形波,频率范围为 $1 \mathrm { H z } { \sim } 5 0 \mathrm { M H z }$ ,占空比范围为$1 0 % { \sim } 9 0 %$ ,显示的分辨率为 $0 . 1 %$ , 测量相对误差的绝对值不大于 $1 0 ^ { - 2 }$ ;

4) 利用 ModelSim 软件对用于频率和占空比测量的各个 FPGA 模块进行功能仿真;

5) 利用Primace和 Keil 等开发工具对整个系统进行设计并下载至开发板,然后利用所设计的频率计测量待测信号的频率和占空比,频率计设计要求达到结果显示刷新时间不大于2s,测量结果稳定,并且能够自动调整显示单位;

6) 通过对ModelSim仿真结果和硬件实测结果的观察与计算,分析在频率、占空比测量中误差的来源和影响因素,并进一步分析减小误差、提高精度的方法和途径。

3. 实验过程及要求(限 300 字)

如对学生在实验过程中在需求分析、资料查询、自学预习、思考讨论、方法设计、进程规划、软件仿真、平台构建、器件选择、表格设计、现象观察、数据测试、问题分析、总结报告、验收答辩、演讲交流等各方面的要求。

1)学习了解不同量程、精度要求下,频率测量所采用的方法,分析各种方法的优缺点、误差的来源及其影响因素等;

2) 学习 FPGA 开发中所用到的工具,如 ModelSim、Primace 等软件,了解其基本操作和功能;

3) 根据等精度测量法的原理,利用 Verilog HDL 设计各个模块,利用ModelSim软件对各个模块的时序和功能进行仿真验证;

4)理解SOPC的概念和原理,利用C语言对所提供的实验平台内嵌的ARM Cortex-M3 内核的程序部分进行设计;

5) 基于实验平台中的 AHB 总线,利用 FIFO 模块实现 FPGA 与 Cortex-M3 内核之间的数据传输;

6) 根据系统的整体设计方案,在实验平台上构建完整的频率计系统,并对待测信号的频率和占空比进行测量,自行设计表格,对测量数据进行记录;

7)根据设计方案和测量结果的误差值,分析误差来源和影响因素,并提出进一步减小误差、提高精度的方案;

8)撰写设计总结报告,并通过分组演讲,学习交流不同解决方案的特点。

4. 相关知识及背景(限 150 字)

项目涉及的知识方法、实践技能、应用背景、工程案例。

这是一个运用 SOPC 技术在内嵌 ARM Cortex-M3 内核的 FPGA 平台上设计实现频率计系统,以解决现实生活和工程实际问题的典型案例,需要运用频率测量、Verilog HDL、FPGA 设计与仿真、时序分析、SOPC、嵌入式系统、数据处理与显示、参数设定与调整等相关理论知识和技术方法,并涉及到测量仪器精度、测量数据处理与分析、系统改进与优化等工程概念和方法。

5. 教学目标与目的(限 100 字)

如学习、运用知识、技术、方法;培养、提升能力、素质。

在较为完整的工程项目实现过程中引导学生了解频率测量方法、ARM Cortex-M3应用、FPGA与SOPC设计与仿真等技术;引导学生根据指标要求选择系统实现方案;引导学生根据系统结构对FPGA模块进行设计与功能仿真,并通过系统搭建、测试与分析对项目做出技术评价。

6. 教学设计与引导

如预习要求及检查;课堂知识讲解、方法引导、背景解释;实验中的方法指导,问题设置、思路引导等。研讨主题、观察节点、验收重点、质询问题的设计等。

本实验的过程是一个比较完整的工程实践工程,需要经历学习研究、方案论证、系统设计、实现调试、测试标定、设计总结等过程。在实验教学中,应在以下几个方面加强对学生的引导:

1)学习频率测量的基本方法,了解随着频率测量范围与测量精度要求的不同,在测量方案设计、测量方法选择等方面不同的处理方法。

2) 实验任务中给出了一定的精度和误差的要求,注意误差或相对误差的计算方式和影响因素分析方法。

3) SOPC 技术是一种基于 FPGA 的片上系统解决方案,该技术将嵌入式处理器集成到 FPGA 芯片中,需要学习SOPC技术与传统的单片机、嵌入式处理器和FPGA之间的关系与区别。

4) 本实验所采用的平台是 FPGA 芯片 CME-M7A12N0F484C7,开发工具包含 Primace、ModelSim、Keil 等,需要讲解实验平台 FPGA 芯片的基本结构,各种工具的基本使用和功能介绍,并对整个开发流程作简单介绍。

5) 可以简单介绍整个系统的工作原理、模块组成和工作流程,要求学生根据课前预习和课上讲解实现频率计系统的设计。

6) 在电路设计、搭试、调试完成后,必须要用标准仪器设备进行实际测量,同时计算所测定频率的误差和精度,给出误差影响因素。

7) 在实验完成后,可以组织学生以项目演讲、答辩、评讲的形式进行交流,了解不同解决方案及其特点,拓宽知识面。在设计中,要注意学生设计的规范性;如系统结构与模块构成,模块间的接口方式与参数

要求;在调试中,要注意工作电源、参考电源品质对系统指标的影响,电路工作的稳定性与可靠性;在测试分析中,要分析系统的误差来源并加以验证。

7. 实验原理及方案

实验的基本原理、完成实验任务的思路方法,可能采用的方法、技术、电路、器件。

1) 系统结构

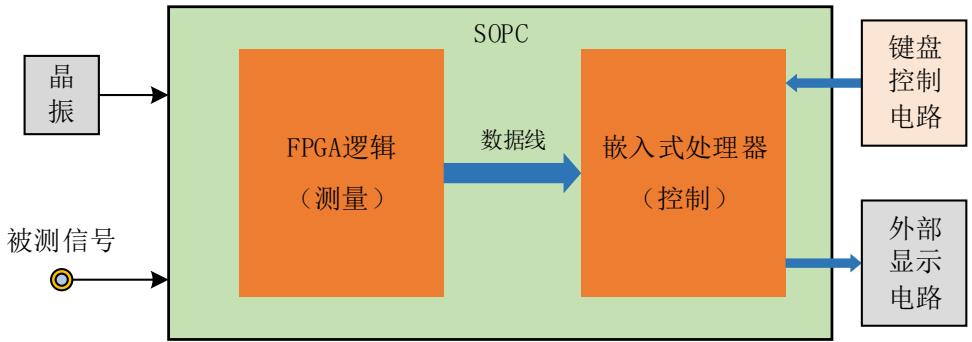

图1 系统结构

本实验的系统结构如图 1所示,外部晶振产生标准时钟信号作为整个系统的基准时钟,SOPC系统中的FPGA逻辑部分用于频率和占空比的测量,并产生测量数据,然后利用一定的数据通讯方式将其传输至嵌入式处理器中。嵌入式处理器根据实际采用的方法和测得的数据来计算测量所得的频率值和占空比值,然后控制外部显示模块显示结果,而键盘控制电路可以利用键盘对系统复位、控制测量等。另外,图 1 所示的系统结构只是一个参考图,在实际设计中,可以根据系统需求适当扩充其他的外围电路。

2) 实现方案

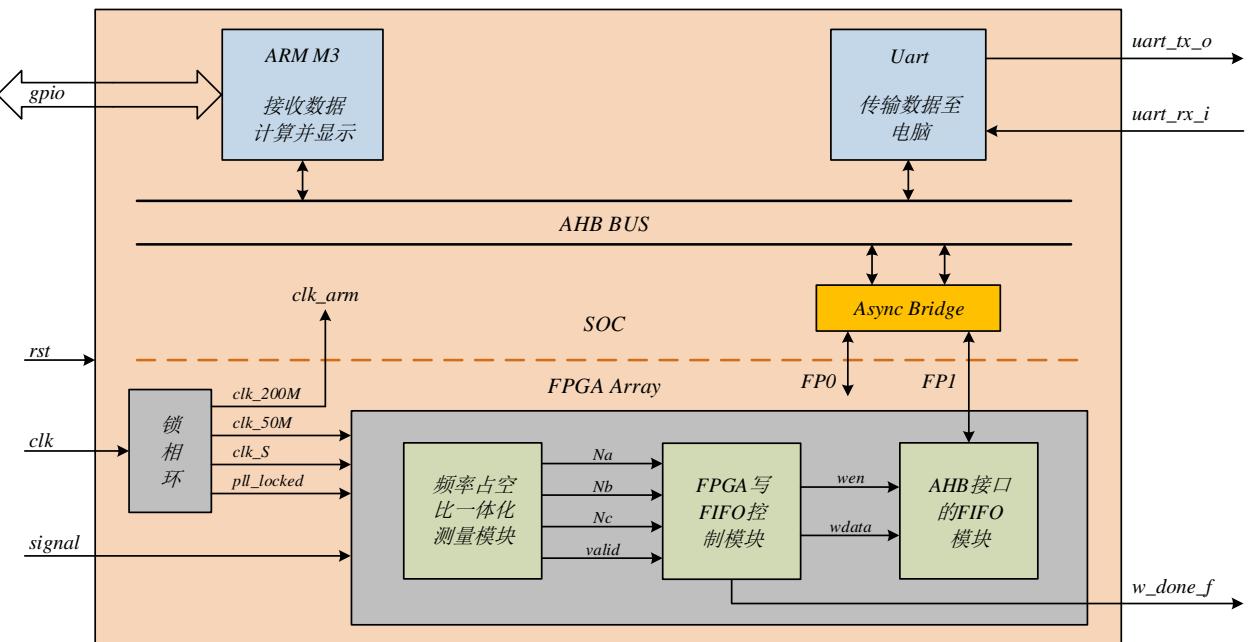

图2 频率计的参考方案

如图 2 所示为基于本实验平台所给出的一种系统解决方案,本实验所设计的频率计系统中包含一个锁相环模块、频率占空比一体化测量模块、FPGA 写 FIFO 控制模块、AHB 接口 FIFO 模块和 ARMCortex-M3 内核等,其中 ARM Cortex-M3 内核、锁相环模块和 AHB 接口 FIFO 模块均为定制化的 IP核,利用 Primace 软件的 IP Wizard 生成即可,而频率占空比一体化测量模块、FPGA 写 FIFO 控制模块则采用Verilog HDL编写设计。整个系统的工作过程如下:

(1)锁相环模块用于对输入的时钟信号 clk 进行倍频,从而产生各路高频时钟信号用于各个FPGA 模块和 ARM Cortex-M3 内核工作。

(2)频率、占空比一体化测量模块用于测量被测信号的频率和占空比,并输出测量所得的计数值(Na、Nb和Nc)和数据有效信号(valid),该模块根据具体的频率、占空比测量方法进行设计。

(3)FPGA写FIFO控制模块用于将频率、占空比一体化测量模块测量所得的数据按照时序要求依次写入到AHB接口FIFO模块中进行缓存,在数据写完成后将写完成信号w_done_f 输出端置高。

(4)ARM Cortex-M3 内核中有一个 32 位的 GPIO,其中一位与上述写完成信号 w_done_f 的输出端相连,当检测到该位有效之后,通过AHB总线依次读取 FIFO地址下的数据。

(5)按照公式对接收到的数据进行计算,从而得到频率值和占空比值,然后通过 GPIO 控制外部显示器显示测量,同时还可以通过UART将数值发送至电脑端显示。

8. 教学实施进程

简要介绍实验实施进程的各个环节(如任务安排、预习自学、现场教学、分组研讨、现场操作、结果验收、总结演讲、报告批改等)中,教学设计的思路、目的,教师、学生各自需要完成的工作任务,需要关注的重点与细节。

1)任务安排:要求每名同学都要掌握测量原理、频率测量所采用的方法以及各种方法的优缺点、误差的来源及其影响因素等。在此基础上根据学生分组,按照实现系统的各个组成模块进行分工,下达实验任务;

2) 预习自学:预习 FPGA 开发中所用到的工具,如 ModelSim、Primace 等软件,熟练 Verilog HDL、C语音编程,等精度测量法原理等;

3) 现场教学:分析设计方案,对每一个组成模块讲解设计要领;

4) 分组研讨:分组讨论系统实现方案以及各个组成模块的设计思路;

5) 现场操作:利用Verilog HDL设计各个模块,利用ModelSim软件对各个模块的时序和功能进行仿真验证;利用 C 语言对所提供的实验平台内嵌的 ARM Cortex-M3 内核的程序部分进行设计;基于实验平台中的 AHB 总线,利用 FIFO 模块实现 FPGA 与 Cortex-M3 内核之间的数据传输;根据系统的整体设计方案,在实验平台上构建完整的频率计系统,并对待测信号的频率和占空比进行测量,自行设计表格,对测量数据进行记录;

6)结果验收:对设计方案和实验测量数据进行评定,并分析测量误差来源和影响因素,为进一步减小误差、提高精度打好基础;

7) 总结演讲:讨论实验中遇到问题,自己的见解、体会和收获,提出对实验的改进意见等;

8)报告批改:主要从是否掌握实验原理、设计性方案可行性如何,实验任务是否明确、是否能正确使用工具和软件,独立、正确完成实验过程;是否能自行发现并排除一般性的实验故障;实验报告是否内容完整、叙述严谨、版面布局合理整洁、数据处理过程完整正确、实验结论是否正确;是否能正确回答实验思考题,实验讨论有一定的见解。

9. 实验报告要求

需要学生在实验报告中反映的工作(如:实验需求分析、实现方案论证、理论推导计算、设计仿真分析、电路参数选择、实验过程设计、数据测量记录、数据处理分析、实验结果总结等等)

实验报告需要反映以下工作:

1) 实验需求分析:反映本实验需要掌握的知识点和需要考察的实践技能;

2) 实现方案论证:列举两种以上实现频率计的方案,并根据指标要求选择系统实现方案;

3) 理论推导计算:根据等精度测量原理计算被测信号的频率、占空比以及测量误差;

4) 模块设计与仿真: 利用 Primace 软件的 IP Wizard 生成 ARM Cortex-M3 内核、锁相环模块和 AHB 接口 FIFO 模块;Verilog HDL 编写设计频率占空比一体化测量模块、FPGA 写 FIFO控制模块;

5) 系统测试方法:在实验平台上构建完整的频率计系统,并对待测信号的频率和占空比进行测量;

6) 实验数据记录: 自行设计表格,对测量数据进行记录;

7) 数据处理分析: 根据设计方案和测量结果的误差值,分析误差来源和影响因素;

8)实验结果总结:撰写实验总结报告,提出进一步减小误差、提高精度的方案。

10.考核要求与方法(限 300 字)

考核的节点、时间、标准及考核方法。

1)实物验收:功能与性能指标的完成程度(如频率测量精度、测量范围、显示器刷新时间等),完成时间。

2)实验质量:系统搭建的稳定程度(如结果显示是否稳定,系统是否存在崩溃、死机等情况)、设计方案的合理性。

3)自主创新:功能构思、电路设计的创新性,自主思考与独立实践能力。

4)实验成本:是否充分利用实验室已有条件,材料与元器件选择合理性,成本核算与损耗。

5) 实验数据:系统测量数据的记录是否合理,对测试数据和测量误差的分析与总结。

6)实验报告:实验报告的规范性与完整性。

11.项目特色或创新(可空缺,限 150 字)

1)该项目以解决现实生活和工程实际问题为出发点,具有较强的工程性背景;

2)该项目将 ARM Cortex-M3 内核与 FPGA 相结合,运用频率测量、Verilog HDL、FPGA 设计与仿真、时序分析、SOPC、嵌入式系统、数据处理与显示、参数设定与调整等相关理论知识和技术方法,并涉及到测量仪器精度、测量数据处理与分析、系统改进与优化等工程概念和方法,达到了知识应用的综合性之目的。

实验案例信息表

| 案例提供单位 | 山东科技大学 | 相关专业 | 电子系统(含单片机及微机系统) | |||

| 设计者姓名 | 王立华 | 电子邮箱 | 13730917192@163.com | |||

| 移动电话 | 13730917192 | 通讯地址(含邮编) | 山东省青岛经济技术开发区前湾港路579号邮编266590 | |||

| 设计者姓名 | 电子邮箱 | |||||

| 移动电话 | 通讯地址(含邮编) | |||||

| 设计者姓名 | 电子邮箱 | |||||

| 移动电话 | 通讯地址(含邮编) | |||||

| 相关课程名称 | SoPC系统设计 | 学生年级 | 大学三年级 | 学时(课内+课外) | 6 | |

| 支撑条件 | 仪器设备 | 计算机,示波器,FPGA开发板 | ||||

| 软件工具 | ModelSim,Keil,Primace,Quartus Il | |||||

| 主要器件 | FPGA 芯片 CME-M7A12N0F484C7,LCD12864 | |||||