基于波形发生器设计与实现的渐进性实验

课程名称:专业综合实训

实验题目:基于波形发生器设计与实现的渐进性实验

课程简要信息

课程名称,课程学时,适用专业,学生年级

课程名称:专业综合实训

课程学时:16学时

适用专业:电子信息工程、测控技术与仪器等

学生年级:一、二、三年级

实验内容与任务(限500字)

项目需要完成的任务(如需要观察的现象,分析某种现象的成因、需要解决的问题等);是否设计有不同层次的任务。

波形发生器是电子技术相关专业中常见的仪器设备,是调试电路必备的助手。在波形发生器中,DAC(数字到模拟转换器)和微处理器(如MCU/FPGA)是核心器件,同时模拟后端的信号调理和波形重建电路对设备的性能也有着至关重要的决定因数。本实验将配合学生学习电路原理、模拟电路、数字电路、信号与系统、单片机原理、FPGA应用与实践等各课程的不同阶段及不同层次,充分利用“硬木课堂”个人多功能实验平台的灵活性及趣味性,渐进性地完成以下实验内容,充分体验电子系统设计的流程及乐趣。本实验作为一次完整的专业综合实训实验项目,也可拆分为各自独立的实验,作为面向不同需求层面的开放实验项目。

第一阶段(2学时)

-

运用电路原理基本知识,分析R-2R电阻网络型DAC的基本原理;

-

运用模拟电路基本知识,分析R-2R型DAC输出信号调理的基本原理;

-

学习了解DAC和运算放大器的指标,运用信号与系统课程知识分析在不同的刷新率下波形重建电路的设计;

-

在仿真软件中设计、搭建电路并对电路进行仿真。

第二阶段(2学时)

-

设计目标:在面包板上搭建一个刷新率不低于1MHz,输出信号带宽100KHz,输出信号幅度范围-10V到+10V的R-2R型DAC;

-

根据设计目标挑选合适的运放,并设计信号调理和波形重建电路;

-

在仿真软件中设计、搭建后端信号调理和波形重建电路;

-

实际搭建电路并使用个人多功能实验平台刷新R-2R型DAC电路,并对整体电路进行调试。

第三阶段(4学时)

-

选择合适的MCU/FPGA最小系统,替代个人多功能实验平台,控制R-2R DAC系统;

-

学习DDS信号发生器原理和实现方法,在MCU/FPGA中实现数控正弦信号源的基本功能;能够设定输出频率,输出直流偏移,和输出信号幅度。

第四阶段(4学时)(拓展)

-

进阶目标:提高DAC系统的位数至12位,提高刷新率至50MHz,提高输出信号带宽至5MHz;

-

根据新的设计目标,选择合适的运放、设计新的模拟信号调理和波形重建电路;

-

为了实现高速信号刷新,绘制、制作PCB图并焊接,与MCU/FPGA最小系统板相连进行电路联调。

第五阶段(4学时)(拓展)

-

加入蓝牙模块,通过手机控制信号源;

-

实现任意波形发生器功能。

实验过程及要求(限300字)

如对学生在实验过程中在需求分析、资料查询、自学预习、思考讨论、方法设计、进程规划、软件仿真、平台构建、器件选择、表格设计、现象观察、数据测试、问题分析、总结报告、验收答辩、演讲交流等各方面的要求。

学生以两人一组的形式进行实验,密切配合,充分理解题目要求,利用所学电路、模电、数电、信号与系统、单片机/FPGA等相关知识,认真设计,用心制作,完成调试。第一到第三阶段分别在各自课内的2学时内完成,第四到第五阶段由学生自由选择在课外进行拓展训练。

- 原理及仿真

查阅R-2R型电阻网络相关文献,了解R-2R电阻网络的工作原理,推导R-2R型DAC的输出电压及输入码元、参考电压之间的数学关系;

复习运算放大器原理及其相关应用电路;

熟悉DA转换的工作原理,了解并熟悉ARM Cortex-M4或FPGA的开发流程。

- 电路设计

自选电阻在面包板上完成R-2R电路;

根据设计目标选择运算放大器,设计运算放大器电路完成R-2R电路输出信号的调理;

根据所用运放特性及DAC刷新率及带宽要求,计算滤波电路并选择合适的电阻和电容;

在个人实验平台上完成系统布线、制作、测试,要求布局合理,布线美观,留有测试点。上电测试之前需用万用表检测是否错接或短路。

- 作品验收与报告总结

作品验收与报告总结同时进行。每组在完成实验后可申请验收,验收同时提交报告,包括理论分析、电路设计、软件流程、数据表格等相关信息。验收过程中将同时针对报告内容进行提问和质疑。

- 申优答辩

申优作品需要申请公开答辩,公开答辩面向全体同学进行,包括10分钟PPT报告与实物演示,5分钟答辩时间。

相关知识及背景(限150字)

项目涉及的知识方法、实践技能、应用背景、工程案例。

这是一个运用电子技术专业知识解决工程实际问题的典型案例,需要运用电路原理、模拟电路、数字电路、单片机原理、FPGA应用与实践、嵌入式处理器或EDA技术等多门课程的相关知识来完成一个设计项目。根据学生层次、学时数的不同,可以裁减实验内容,核心在于巩固和运用多门基础课程的知识来完成一个实际有用的电路。同时包括了运算放大器选择、信号调理、滤波器设计、数模信号转换、FPGA设计、人机交互、参数设定、反馈控制相关知识与技术方法,并涉及测量仪器精度、线性度,硬件及软件协同和这种,仪器设备标定及抗干扰等工程概念与方法。

本项目的设计构思是来自于一次淘宝经历,因教学科研需要购置波形发生器,在淘宝上的波形发生器动辄上千元,但经过对其电路的剖析发现其电路组成非常简单,完全可以低成本自制,并且其电路各组成部分非常适合学生在不同的专业课程学习阶段进行渐进性实践训练,最后可形成一个完整的电子产品。这样既可满足课程实验要求,又能让学生体验电子产品的研发过程,有利于学生的创新能力的培养。

教学目标与目的(限100字)

如学习、运用知识、技术、方法;培养、提升能力、素质。

本实验案例通过应用电子类综合实验技能解决工程实际问题,一方面让学生掌握小信号放大、功率放大、滤波、模数数模转换等知识以及电子系统设计的方法,同时通过工程实际培养学生的自学能力、综合应用能力、交流沟通能力以及协作创新能力。

教学设计与引导

如预习要求及检查;课堂知识讲解、方法引导、背景解释;实验中的方法指导,问题设置、思路引导等。研讨主题、观察节点、验收重点、质询问题的设计等。

本实验是一个典型的解决电子系统工程实际问题的应用案例,从设计过程来看是一个比较完整的小系统设计工程,从实验准备上需要进行充分的知识储备,经历学习研究、方案论证、系统设计、电路焊接、单元电路调试、整体电路联调测试、设计总结、申优答辩等过程。在实验教学中,应注意以下几个方面:

-

充分重视工程实际相关问题的学习和文献查阅,了解模拟信号发生器的应用领域及重要性,了解模拟信号发生器的常用实现方案及基本原理。

-

熟悉R-2R电阻网络的工作原理,推导R-2R型DAC的输出电压及输入码元、参考电压之间的数学关系。

-

熟悉运算放大器原理及其相关应用电路。

-

熟悉DA转换的工作原理,了解并熟悉ARM Cortex-M4或FPGA的开发流程。

-

在实验完成后,学生以项目演讲、答辩、评讲的形式进行交流,了解不同解决方案及其特点,拓宽知识面。在进行作品测试时要求学生一起观看,了解其他学生作品的特点。

作品验收时,要注意学生设计的规范性;如系统结构与模块构成,模块间的接口方式与参数要求,测试点的预留,电路工作的稳定性与可靠性,在报告的在测试分析中,要分析系统的误差来源并加以验证。

实验原理及方案

实验的基本原理、完成实验任务的思路方法,可能采用的方法、技术、电路、器件。

(1)实施方案

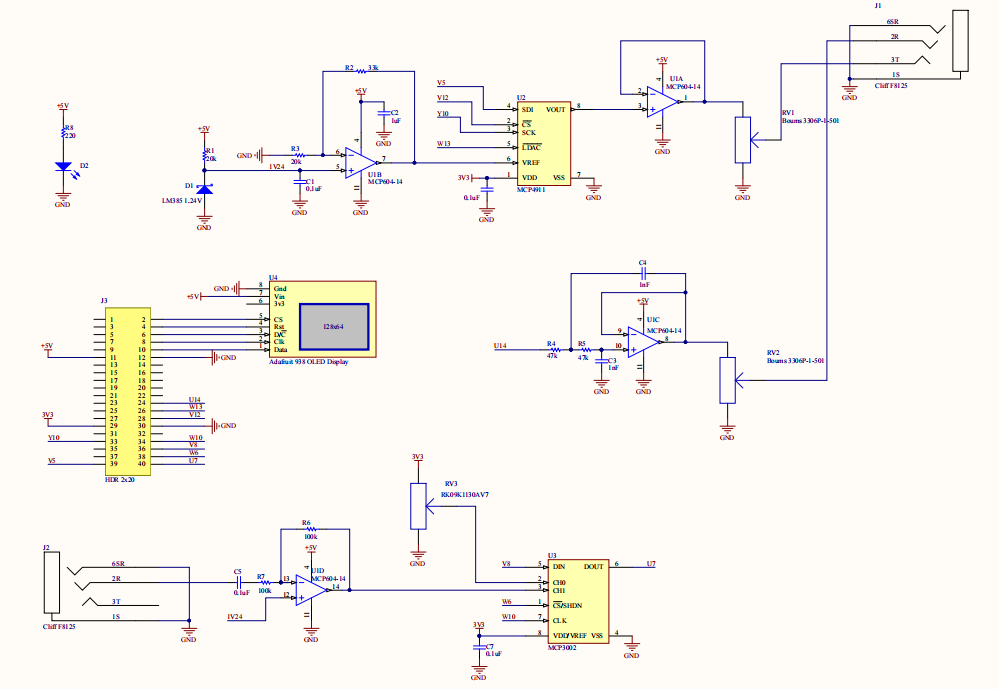

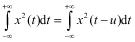

图1 实施方案

第一步,利用电路原理的知识分析R-2R电阻网络中各个输入电压对输出的贡献,并对电路仿真。

第二步,利用模拟电路的知识设计R-2R DAC的后端电路,包括电路中运放的选择(根据输出信号的频率和电压范围选择运放),和低通滤波器设计(借助信号与系统的知识介绍DAC输出信号的频谱从而告诉学生滤波器的截止频率设计在fout, 用RC电路或运放有源滤波器进行滤波),设计,并在面包板上搭建电路,用实验平台的DIGITAL OUT来刷新自制的R-2R型DAC(给定刷新率,导入不同的波形表来输出不同幅度和频率的正弦波),实测时对比滤波前后的波形;用实验平台的信号源输出直流电平来改变输出信号的直流分量;

第三步,用FPGA或单片机最小系统来替代实验平台,完成R-2R电阻网络的刷新。

(2)DAC实验方案

方案一:二进制权电阻网络DAC

图2 二进制权电阻网络DAC

如图为一个8bit权电阻网络DAC,二进制输入D0-D7,每一位的输出电压均为0或者Vref,使用运算放大器的求和电路,将参考电压或地通过不同位权的电阻连接到加法电路输入端。由于加法器运放的输出是反向的,后面还需一级反相器,而且需要大量不同阻值的电阻,还要求均为2倍关系,标准阻值很难满足要求。

方案二:R2R电阻网络DAC

图3 R2R电阻网络DAC

如图为8bit的R2R电阻网络DAC的原理图,二进制输入D0-D7,每一位的输出电压均为0或者Vref。R2R电阻网络DAC是单纯的电阻网络,不需要运放的辅助,一个n位的R2R电阻网络DAC只需要n-1个R电阻和n+1个2R电阻,且只需要两种阻值,方便手工制作,在精度要求不高的应用中,可以直接使用电阻搭建,避免使用集成DAC,从而降低成本。这个电路最神奇的地方在于,无论从哪个位置断开,向内看阻抗均为R。输出阻抗固定为R,由于输出阻抗恒定且容易计算,因此在输出做阻抗匹配时候比较方便。

本实验选用R2R电阻网络作为DAC电路。

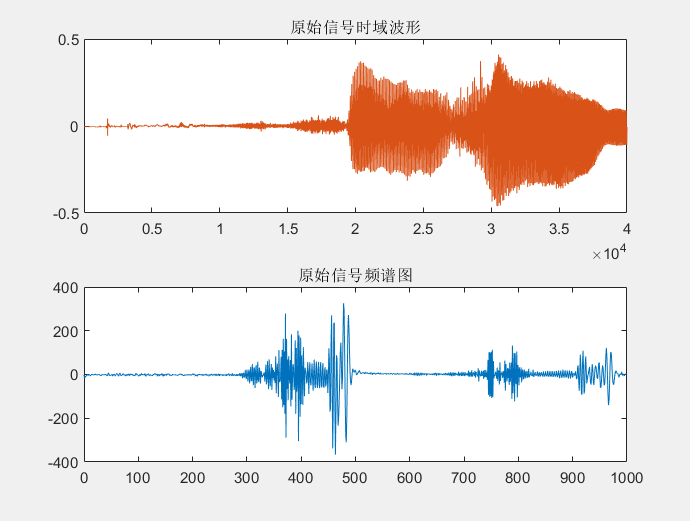

3bit的R-2R型电阻网络DAC电路原理仿真如下:

图4 3bit的R-2R型DAC电路仿真

量化前的正弦波:

图5 量化前的正弦波

3bit二进制进行量化:

图6 3bit量化后的正弦波

正弦波表:

图7 正弦波表

在“硬木课堂”个人多功能实验平台上搭建实验电路:

图8 实验电路

正弦波数据导入:

图9 正弦波数据导入

点击开始发送数据,Digout上就会产生电平:

图10 Digout输出

用示波器观察DA输出波形:

图11 DA输出波形

黄色是RC滤波前的信号,蓝色是RC滤波后的信号。

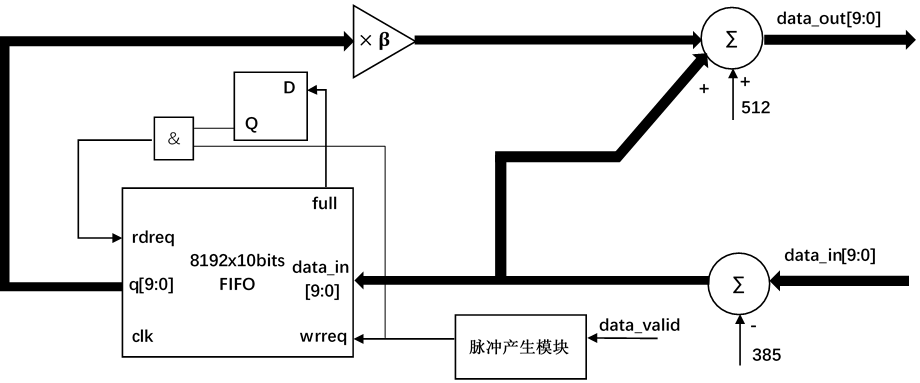

(3)信号调理电路实验方案

电路原理仿真如图。

图12 信号调理电路

运用集成运放构成信号调理电路,主要实现阻抗变换以及双极性变换作用。其运算关系为Vo=2Vi-Vref。

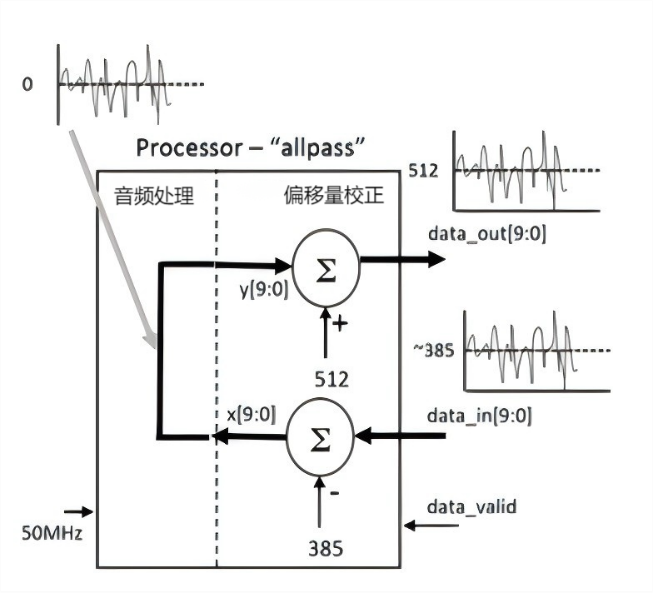

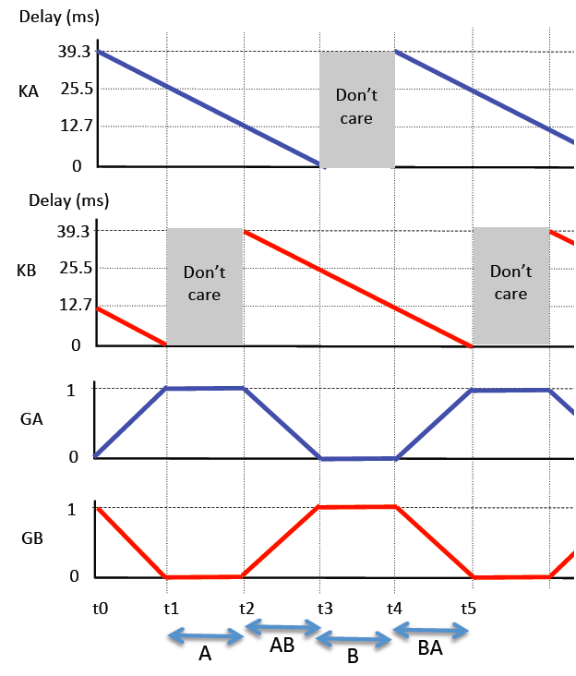

(4)滤波重建电路实验方案

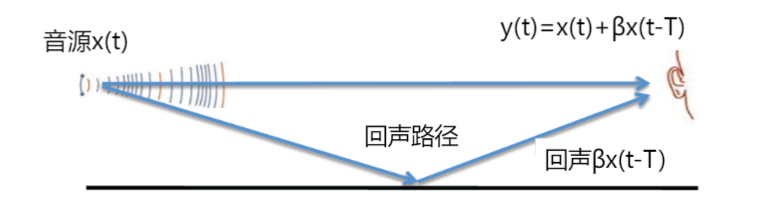

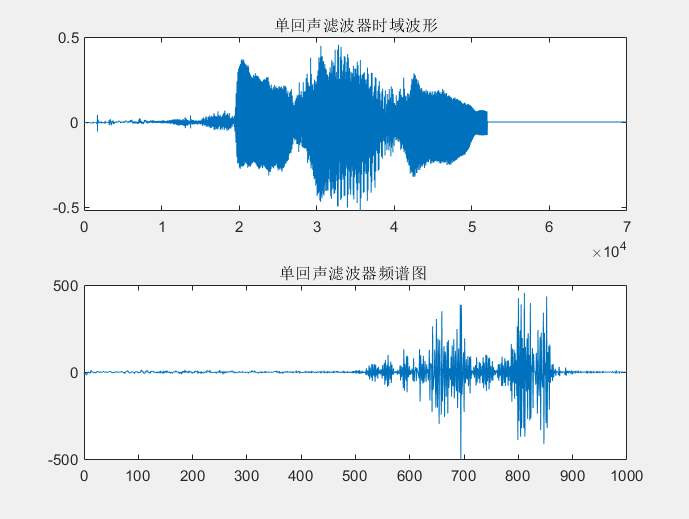

当DDS时钟频率为fc、输出频率为

,DA输出的正弦信号的频谱特性如图。

图13 DDS输出的正弦信号的频谱特性

输出频谱中除主频

外,还存在分布在

,

,…两边

处的非谐波分量,幅值包络为Sa函数,即其频谱被Sa函数加权,输出频率较大的时候,幅度会衰减。为了得到所需要频段内的信号,需要在DDS输出端加一低通滤波器,将D/A输出的台阶信号经低通滤波器平滑滤波,滤除不需要的频率分量,以便输出频谱纯净的波形信号。

设计的低通滤波器电路及其频率特性如图。

图14 低通滤波器电路仿真

图15 低通滤波器电路的频率特性

运用集成运放构成滤波重建电路,由两节RC滤波电路和同相比例放大电路组成二阶低通滤波器。其特点是,输入阻抗高,输出阻抗低。

滤波前后的信号:黄色是滤波前的信号,蓝色是滤波后的信号。

图16 滤波前后的信号

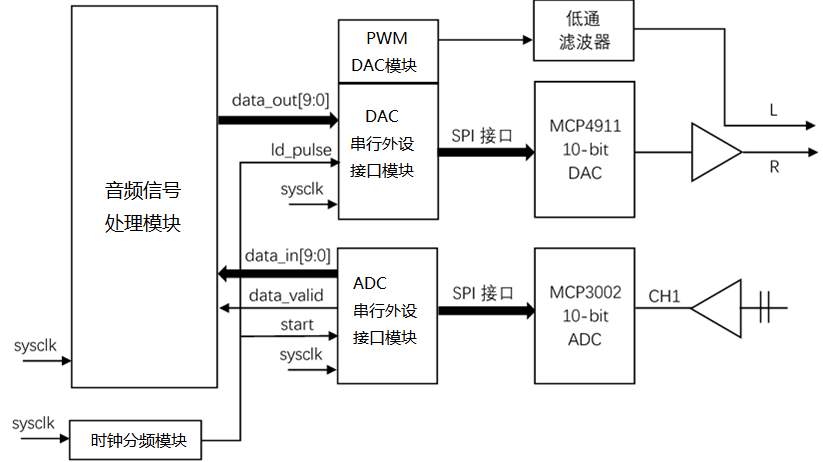

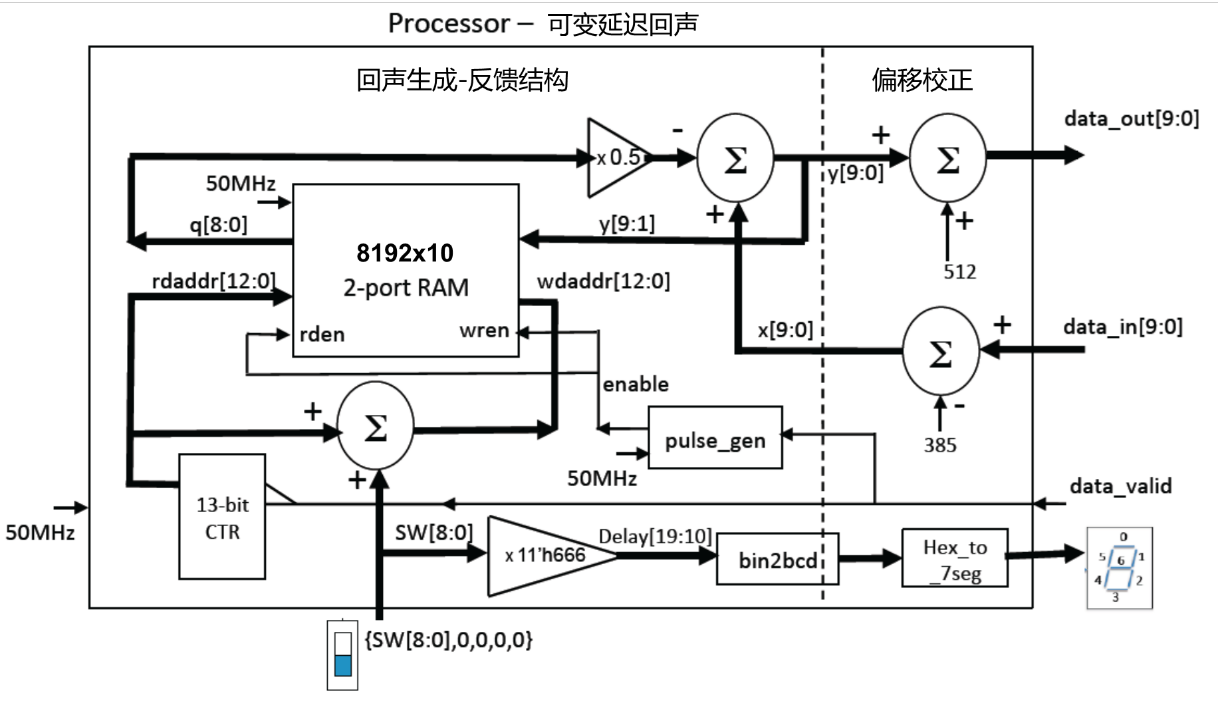

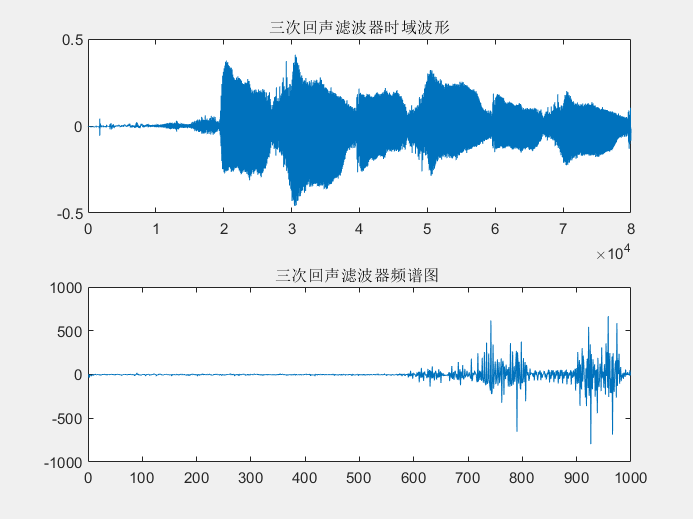

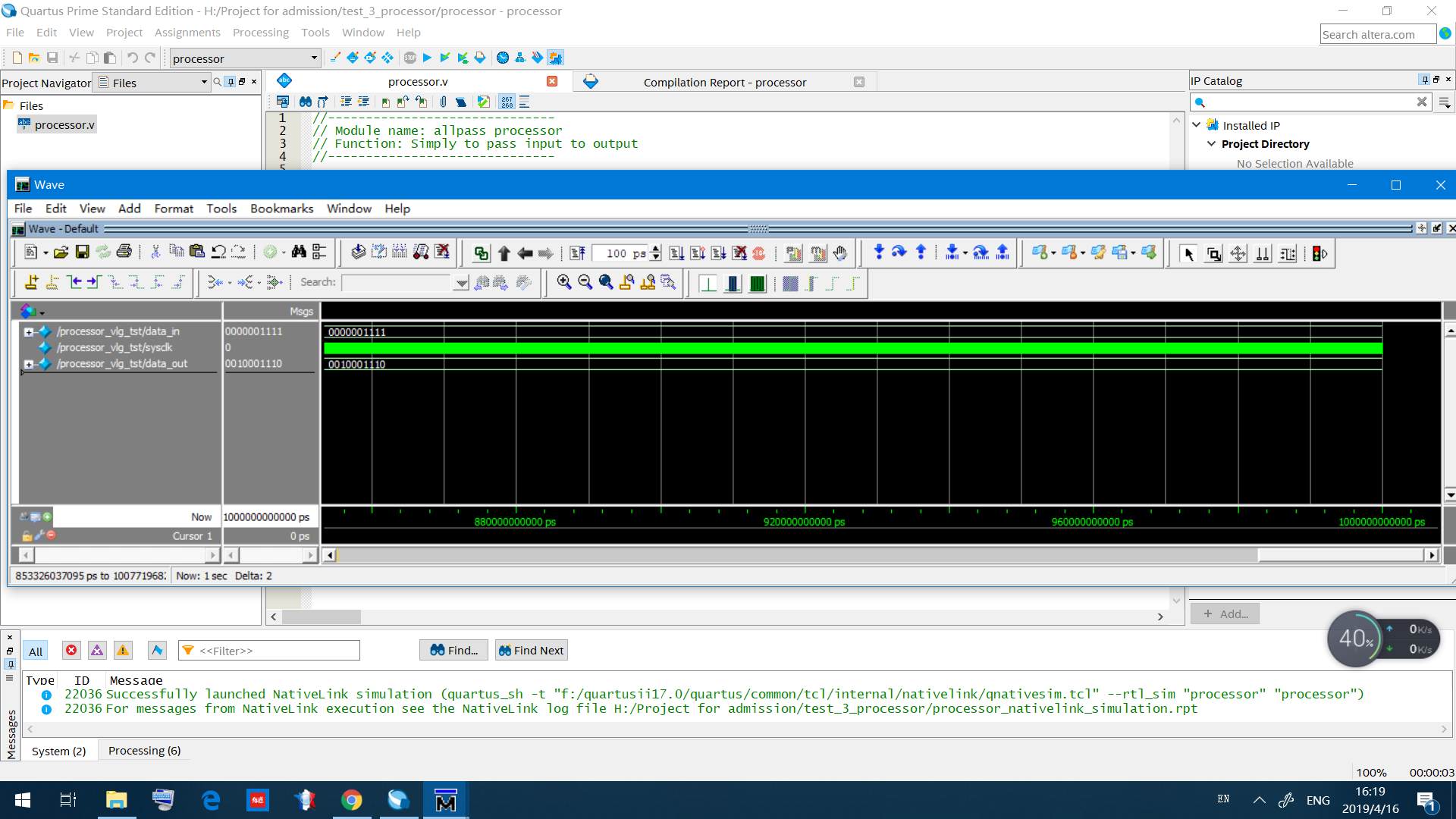

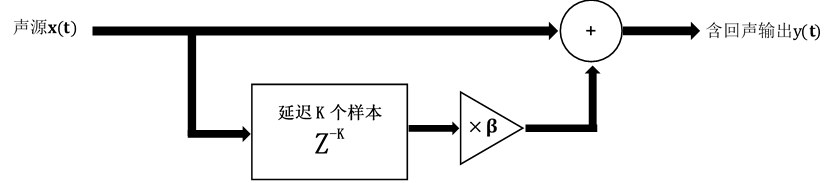

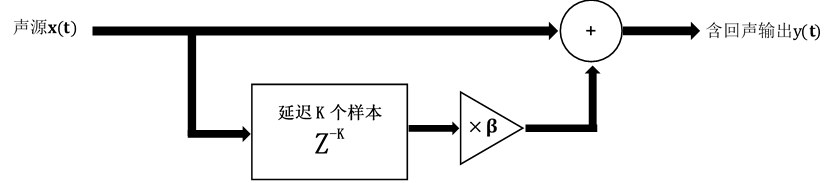

(5)基于FPGA的DDS设计

DDS即直接数字频率合成( Direct Digital Synthesis) ,是基于数值计算信号波形的抽样值来实现频率合成的。DDS的工作原理是基于相位和幅度的对应关系, 通过改变频率控制字来改变相位累加器的累加速度, 然后在固定时钟的控制下取样, 取样得到的相位值通过相位幅度转换得到与相位值对应的幅度序列, 幅度序列通过数模转换得到模拟形式量化的波形输出。

下图是DDS的结构组成。

图17 DDS的结构

DDS的核心就是相位累加器,利用它来产生信号递增的相位信息,整个DDS系统在统一的参考时钟下工作,从而保证所合成信号的精确。每个时钟周期相位累加器作加法运算一次,相位累加器在参考时钟的作用下,进行线性相位累加,当相位累加器累加满量时就会产生一次溢出,完成一个周期性的动作,这个周期就是DDS合成信号的一个频率周期,累加器的溢出频率就是DDS输出的信号频率。加法运算的步进越大,相应合成的相位值变化越快,输出信号的频率也就越高。

波形存储器将累加器相位信息转换为幅值信息的功能。用相位累加器输出的数据作为波形存储器的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。

波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。D/A输出的台阶信号再经低通滤波器平滑滤波,滤除不需要的取样分量,以便输出频谱纯净的波形信号。

DDS的输出频率为

,DDS输出的频率步进间隔

。其中相位累加器字长为N,fc为DDS控制时钟频率,频率控制字为K。

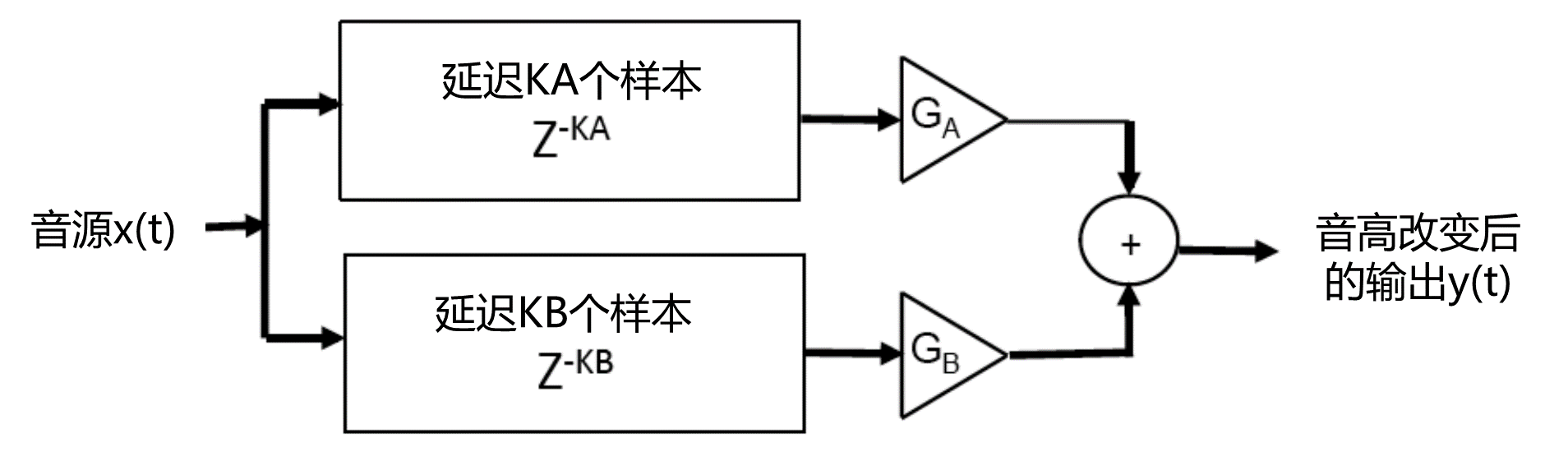

任意波形发生器的FPGA的电路设计主要是用FPGA设计DDS的核心部分即相位累加器、相位加法器、相位寄存器、控制字输入寄存器、波形ROM、波形RAM、任意波形数据寄存器。基于FPGA的任意波形发生器的电路组成框图如图所示。

图18 基于FPGA的任意波形发生器的电路组成

该系统可实现常规固定波形输出和任意波形输出。其中相位累加器是一个带有累加功能的32位加法器,它以设定的频率控制字k作为步长来进行加法运算,当其和满时清零,并进行重新运算。相位寄存器是一个10位寄存器,它接收单片机送来的频率和相位控制字数据并进行寄存,当下一个时钟到来时,输入寄存的数据,对输出波形的频率和相位进行控制。波形查找表ROM及RAM是DDS的关键部分,设计时首先需对时域波形进行采样,将采样的波形数据储存到波形查找表ROM及RAM中,每一位地址对应一个波形点的数值,任意波形数据寄存器接收单片机送来的任意波形数据数据。整个系统各模块是在同步时钟信号CLK的控制下协调工作的。

教学实施进程

简要介绍实验实施进程的各个环节(如任务安排、预习自学、现场教学、分组研讨、现场操作、结果验收、总结演讲、报告批改等)中,教学设计的思路、目的,教师、学生各自需要完成的工作任务,需要关注的重点与细节。

- 任务安排

波形信号发生器的设计与实现作为工程实际项目,任务安排不仅要让学生明白设计的内容,而且要理解设计要点、实验方法、实验流程等各项要素。尤其作为工程实际项目,如何从知识背景中提炼出技术指标,这是学生以往没有遇到的。因此通过任务安排,将后面的各个环节清晰、明确的传达给学生是首要之重。

- 现场教学

分析R-2R电阻网络的工作原理,推导R-2R型DAC的输出电压及输入码元、参考电压之间的数学关系,复习运算放大器原理及其相关应用电路,回顾DA转换的工作原理,了解并熟悉ARM Cortex-M4或FPGA的开发流程。要点,让学生对电路原理、模拟电路、数字电路、EDA技术等多门课程的相关知识与之间信号发生器的设计形成清晰的关联关系,并对其中的核心模块进行重点讲解,以克服同学的畏难情绪。

- 现场操作

学生动手,教师答疑。此环节旨在锻炼学生的动手操作能力。渐进式分步进行。

- 结果验收

此环节旨在查验学生完成实验的情况以及对实验内容的理解。

第一阶段的验收:对R-2R电阻网络型DAC及DAC输出信号调理电路的基本原理的分析和相关推导是否正确;对电路的仿真结果进行验收及评讲;

第二阶段的验收:

设计目标:对在个人多功能实验平台上搭建的R-2R电阻网络型DAC及DAC输出信号调理电路进行测试验收及调试,基本满足设计要求;

第三阶段的验收:对基于FPGA的DDS电路的基本功能进行评测验收,基本满足设计要求;

第四阶段(选做)的验收:对PCB图的绘制、制作及焊接等工艺进行验收及展示,根据设计目标对输出波形形状、频率和相位及稳定度、幅度等进行测量验收;

第五阶段(选做)的验收:对任意波形发生器的手机控制功能进行评测验收。

5)总结答辩

在实验完成后,申优作品需要申请公开答辩,公开答辩面向全体同学进行,以项目演讲、答辩、评讲的形式进行交流,了解不同解决方案及其特点,拓宽知识面。在进行作品测试时要求学生一起观看,了解其他学生作品的特点。

实验报告要求

需要学生在实验报告中反映的工作(如:实验需求分析、实现方案论证、理论推导计算、设计仿真分析、电路参数选择、实验过程设计、数据测量记录、数据处理分析、实验结果总结等等)

实验报告需要反映以下工作:

-

实验需求分析

-

实现方案论证

-

理论推导计算

-

电路设计与参数选择

-

电路测试方法

-

实验数据记录

-

数据处理分析

-

实验结果总结

考核要求与方法(限300字)

考核的节点、时间、标准及考核方法。

-

实物验收:功能与性能指标的完成程度(如输出频率准确度与稳定度、输出幅度稳定度等),完成时间。

-

实验质量:电路方案的合理性,焊接质量、组装工艺。

-

自主创新:功能构思、电路设计的创新性,自主思考与独立实践能力。

-

实验成本:是否充分利用实验室已有条件,材料与元器件选择合理性,成本核算与损耗。

-

实验数据:测试数据和测量误差。

-

实验报告:实验报告的规范性与完整性。

项目特色或创新(可空缺,限150字)

项目的特色在于:项目背景的工程性,知识应用的综合性,实现方法的多样性,实验项目的渐进性,理论与实践的紧密性。

参赛选手信息表

| 案例提供单位 | 攀枝花学院 | 相关专业 | 电子信息工程、测控技术与仪器等 | |||

|---|---|---|---|---|---|---|

| 设计者姓名 | 周登荣 | 电子邮箱 | 494982494@qq.com | |||

| 移动电话 | 13096096239 | 通讯地址 (含邮编) |

四川省攀枝花市东区机场路10号电信学院电工电子教研室(617000) | |||

| 设计者姓名 | 郭筱瑛 | 电子邮箱 | 25971025@qq.com | |||

| 移动电话 | 18081726968 | 通讯地址 (含邮编) |

四川省攀枝花市机场路10号攀枝花学院电信学院办公室(617000) | |||

| 设计者姓名 | 黄昆 | 电子邮箱 | 39827453 qq.com | |||

| 移动电话 | 13882374618 | 通讯地址 (含邮编) |

四川省攀枝花市机场路10号攀枝花学院电信学院办公室(617000) | |||

| 相关x课程名称 | 电路原理、模拟电路、数字电路、单片机原理、FPGA应用与实践 | 学生年级 | 一、二、三年级 | 学时(课内+课外) | 16 | |

支撑 条件 |

仪器设备 | “硬木课堂”个人实验平台 | ||||

| 软件工具 | Electronics Pioneer、QuartusII、keil 4、protel99、multisim10 | |||||

| 主要器件 | NE5532、TL082、Altera FPGA微模块、STM32F407微模块 | |||||