嵌入式多核处理器开发环境的信号采集与实时处理

实验题目:嵌入式多核处理器开发环境的信号采集与实时处理

高永婵西安电子科技大学

1. 课程简要信息

课程名称: 专业课程设计课程性质: 集中实践教学课程学时: 36 学时适用专业: 电子信息工程学生年级: 大三学生、大四学生

2. 实验内容与任务(限 500 字)

结合数字信号处理的实际需求, 要求设计基于嵌入式多核处理器开发环境的信号采集与实时处理的课程案例,能加深对调制过程的理解,可以牢固掌握对直接数字频率合成技术(DDFS)生成信号的学习,可以有效通过窗函数法设计滤波器,观察到信号处理的结果,实现对数字信号处理中数字滤波的有效认识和理解,为复杂的信号处理算法的实时处理奠定基础。

基本任务:

(1) 熟悉 CCES 的开发环境。针对 BF609 DSP,利用几个用 C 语言写成的简单例子来描述 CCES 编程环境和调试器的主要特征和功能;

(2) 掌握信号的幅度调制原理;

(3) 了解信号调制过程中波形和频谱的变化,加深对调制的理解;

(4) 了解并学习通过直接数字频率合成技术生成信号的原理;

(5) 学习如何通过编程,使用 BF609 实现直接数字频率合成技术(DDFS);

(6)通过窗函数法来设计滤波器,滤波效果可以直接在开发环境(plot)上看到,通过这个实验来加深对数字滤波信号处理方法的理解。

拓展任务:

(7)考虑其他信号处理方法,进行创新性设计。

3. 实验过程及要求(限 300 字)

(1)理论知识: 学习数字信号的幅度调制原理、2ASK 调制原理,直接数字频率合成技术(DDFS),FIR 滤波器的原理、结构和特点;

(2)需求分析: 查阅资料, 充分了解系统的功能及要求, 并分组讨论;(3)方案设计: 将系统划分为若干个相对独立的模块, 得到完整的系统处理框图;

(4)硬件连接; 根据实现的功能,按步骤有序进连接开发板、仿真器、信号发生器和电脑,最后给开发板上供电;

(5)软件程序设计: 画出程序流程图, 进行软件编程,并编译、链接和调试程序;

(6)输出结果记录与分析:用 plot 画出输入的信号和输出信号,记录输出结果,并做好实验记录,并进行初步分析;

(7)设计总结: 撰写课程设计报告, 分组进行实验演示和验收答辩。

4. 相关知识及背景(限 150 字)

该课程设计是将《数字信号处理》课程知识进行综合性设计应用的一个典型实例。 整个项目实验过程需要运用信号调制技术、 直接数字频率合成技术、滤波器设计、数据显示、 参数设定等相关知识, 并涉及相关工程概念, 实验项目在电子信息工程专业领域具有较强的应用背景。

5. 教学目标与目的(限 100 字)

在项目实践过程中引导学生了解 CCES 的开发环境、数字信号处理等相关知识,培养学生知识应用能力和实践动手能力, 同时培养学生的基本工程素养, 提高学生分析和解决问题能力, 为后续专业课程学习和工作实践奠定基础。

6. 教学设计与引导

本课程设计是一个比较完整的工程实践项目, 以“工程项目为驱动” 需要经历资料查询、 方案论证、 系统设计与仿真、 单片机最小系统板焊接, 实现调试、 设计总结等过程。 在实验教学中, 应在以下几个方面加强对学生的引导:

(1)实验前, 以学生自主预习“学在西电” 平台资料 $^ +$ 教师讲解为主

1)在实验开始前两周, 教师在学校“学在西电” 平台下发本课程所需学习资料、软件, 要求学生登录“学在西电” 平台提前学习所需知识, 掌握开发软

件, 了解实验工具及仪器;

- 实验开始时, 教师讲解本次实验项目背景、 实验目的、 实验内容;3)教师检查学生自主预习情况, 通过提问的方式进行抽查, 并对所用到的基本仪器进行概述介绍;

4)引导学生建立工程实践的概念, 讲解实践与理论课程的差异, 强调实验中的注意事项等;

5)对实验所用到的数字信号处理模块进行详细原理讲解;

6)介绍常用文献资料查阅方法;

7)讲解本次课程设计最终要求, 包括实物演示系统的具体功能, 报告撰写要求,验收标准等;

(2)实验中, 以学生为主, 教师指导为辅

1)学生按照 5 人/组进行分组, 以小组为单位查阅资料, 进行算法建模,确定设计方案, 教师检查每组学生设计方案, 给出设计方案的可行性等指导;

2)学生根据需求, 进行硬件连接;

3)学生建立工程文件,画出主要算法的流程图;

4)学生编写软件程序,并编译、链接和调试;

5)记录输出结果,并分析;

6)系统基本功能完成后, 引导学有余力的学生进行系统算法功能拓展和创新,比如:卷积的实现,图像滤波的实现等。

(3)实验后, 以学生为主,教师指导为辅

1)学生撰写设计报告,报告格式规范,图表清晰,内容完整;

2)学生每组进行系统实物演示、验收;

3)学生采用 PPT 形式进行项目汇报, 阐述课程设计的内容和在设计过程中遇到的问题, 以及是如何解决的。接下来其他组同学和教师进行现场提问,考察学生知识掌握情况;

4)学生对实验操作台进行整理,保持实验台整洁,安全,关闭各种调试设备电源,养成良好的工程习惯。

7. 实验原理及方案

本实验室基于嵌入式多核处理器开发环境的信号采集与实时处理的课程案例,能加深对调制过程的理解,可以牢固掌握对直接数字频率合成技术生成信号的学习,可以有效通过窗函数法设计滤波器。实验环境为:安装有 CCES 软件的计算机、 BF609 教学板、信号发生器、示波器。整体的实验方案如下:

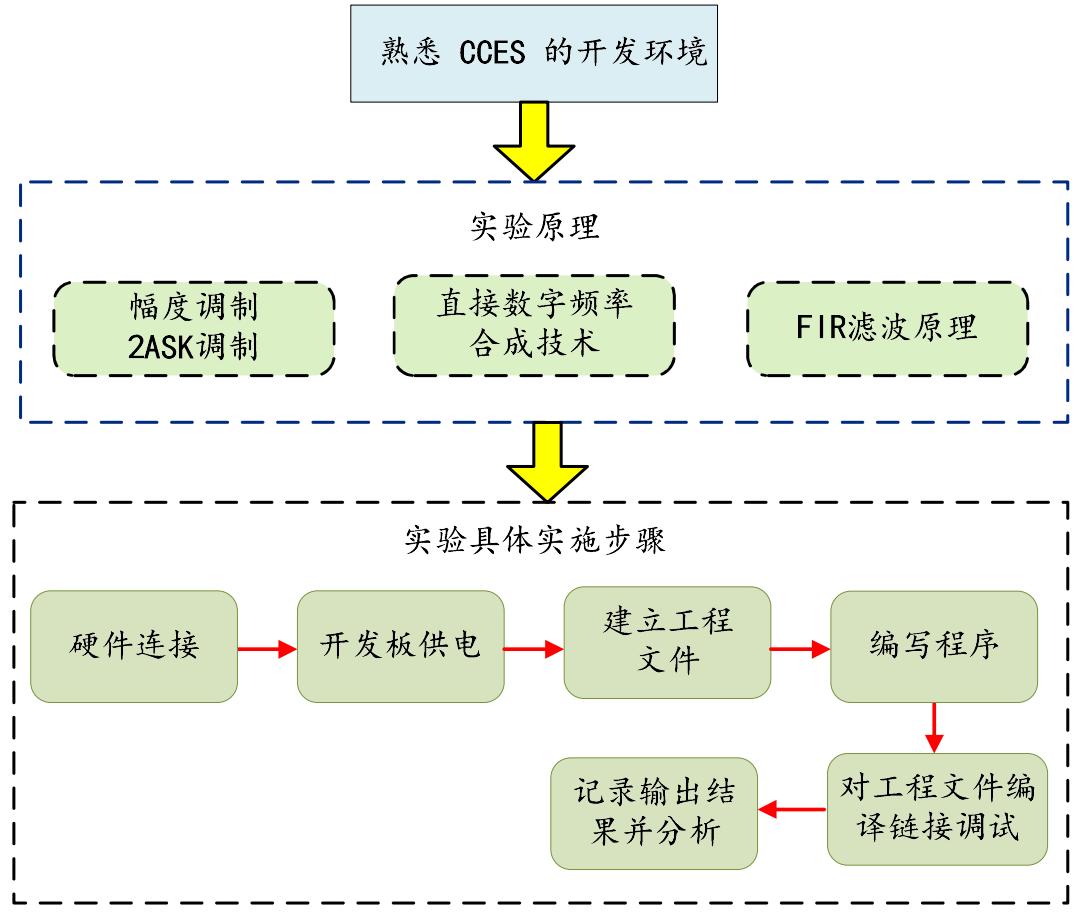

图 1 整体的实验方案

主要实验原理如下:

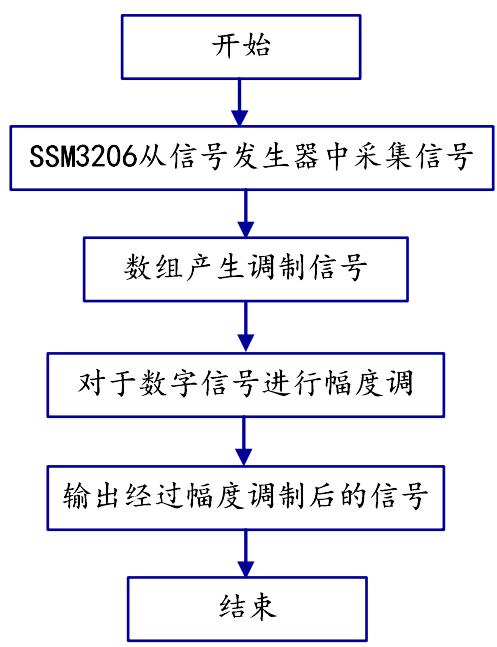

(1)幅度调制流程如下图所示,进入主程序后,首先先对程序进行采样,然后产生调制信号,然后进行 2ASK(二进制幅值键控调制),然后输出调制结果。

图 2 幅度调制流程

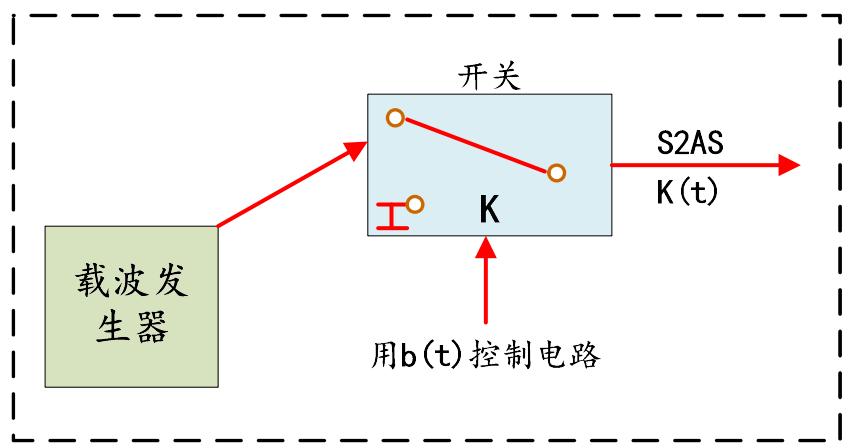

2ASK 调制原理是先将接收到的数据用空指针的方式拼接成 16 位的数据后,然后将其与pw信号进行相乘。2ASK 信号的产生方法如下图所示:

图3 2ASK 信号的产生方法

该方式为键控方法,这里的开关电路受 b(t)控制,b(t)为单极性 NRZ 矩形脉冲序列。

(2)直接数字频率合成技术(DDFS)生成信号

DDFS 可以用来产生任意波形的周期信号,其原理即是查表法,内部用于一个储存一个周期的波形。那么这个查找表其实就是给出了相位到函数值的一个映射关系 $y = f ( \omega )$ 。 这里相位 $\omega$ 又是时间 t 的线性函数:

$$ \omega = \omega ( t ) = \omega ( \Delta n ) = k \cdot \Delta \cdot n . $$

而调整输出频率实际上就是调整相位函数的系数 $\mathsf { k } ^ { \star } \Delta$ 。

(3)FIR 基本原理

FIR 滤波器是非递归型滤波器的简称,又叫有限长单位冲激响应滤波器。输入序列为 $\mathrm { X } ( n )$ ,输出序列 $y ( n )$ ,滤波器系数为 $h ( n )$ 的 FIR 滤波器的实现基于序列的卷积算法,其数学表达式为:

FIR 滤波器的系统函数为:

$$ y \left( n \right) = h \left( n \right) * x \left( n \right) = \sum _ { k = 0 } ^ { N - 1 } x \left( k \right) h \left( n - k \right) $$

$$ H \left( z \right) = \sum _ { n = 0 } ^ { N - 1 } h \left( n \right) z ^ { - n } $$

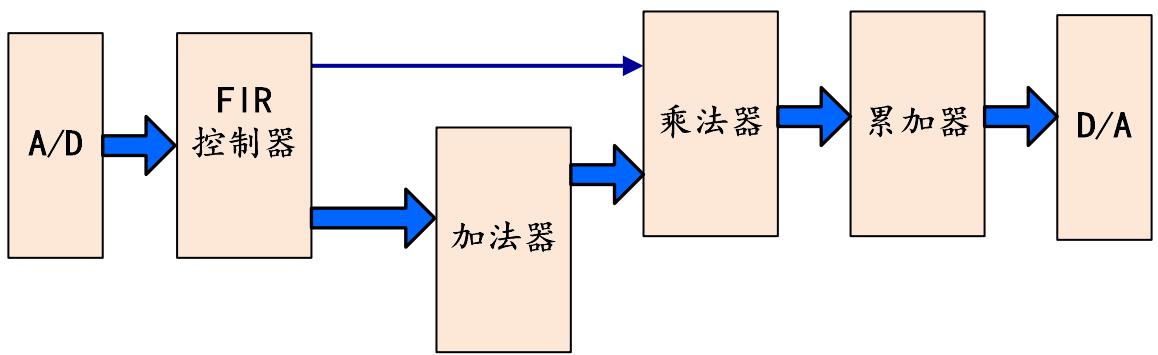

FIR 滤波硬件工作原理如下图所示:

图4 FIR 滤波器原理工作图

在信号进入 FIR 滤波器前,首先要将信号通过 A/D 器件进行模数转换,使之成为 8bit 的数字信号,一般可用速度较高的逐次逼进式 A/D 转换器,不论采用乘累加方法还是分布式算法设计 FIR 滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由 FPGA 构成的 FIR滤波器的输出须外接 D/A 模块。FPGA 有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用 DSP 芯片来说,其并行性和可扩展性更好,利用 FPGA 乘累加的快速算法,可以设计出高速的 FIR 数字滤波器。

主要实验实施步骤为:

信号调制的实验步骤:

-

硬件连接:连接开发板和仿真器,并将信号发生器(方波功能)与开发板进行连接,通过USB 线将电脑与开发板进行连接。

-

待硬件全部连接好后,再给开发板上供电。

-

建立工程文件,对工程进行编译、链接、debug 调试。

-

记录输出结果并进行分析。

-

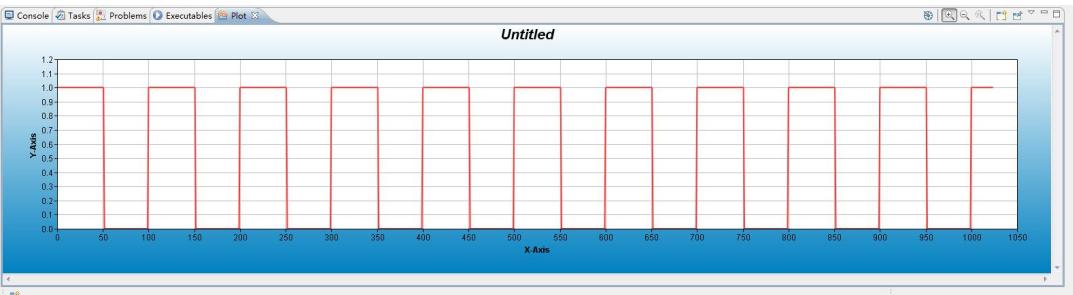

在 plot 上选择 pw 进行输出,步进步数选择 1,输出数据类型选择 16 位有符号整型数据。

-

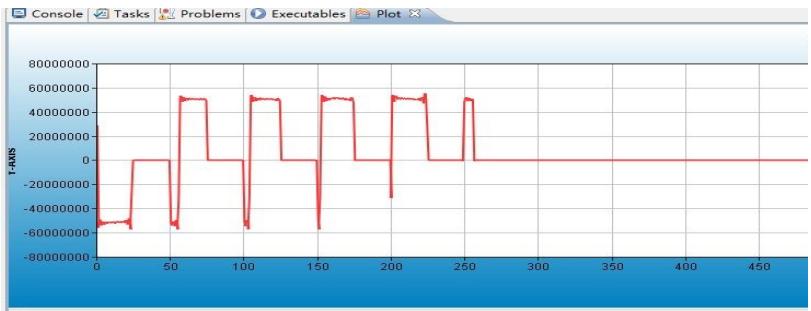

在 plot 上选择 out3 进行输出,步进步数选择 1,输出数据类型选择 32位有符号整型数据。

-

观察输出波形,并对输出结果进行记录,并将结果记录保存。

DDFS 生成信号的实验步骤:

- 通过音频线将 BF609 教学板的音频输出和示波器相连接。

- 对 BF609 教学板上电,并打开示波器。

- 打开CCES 开发环境,并打开工程文件。

- 编译工程文件,并下载程序到开发板,运行程序并根据示波器显示结果验证实验结果。并做好实验记录。

- 通过修改两个子函数的输入参数来修改输出频率的波形和频率,并做好实验记录。(注:每人最少需修改 3 次数据,并进行程序下载、验证以及结果记录)

滤波器设计主要步骤:

-

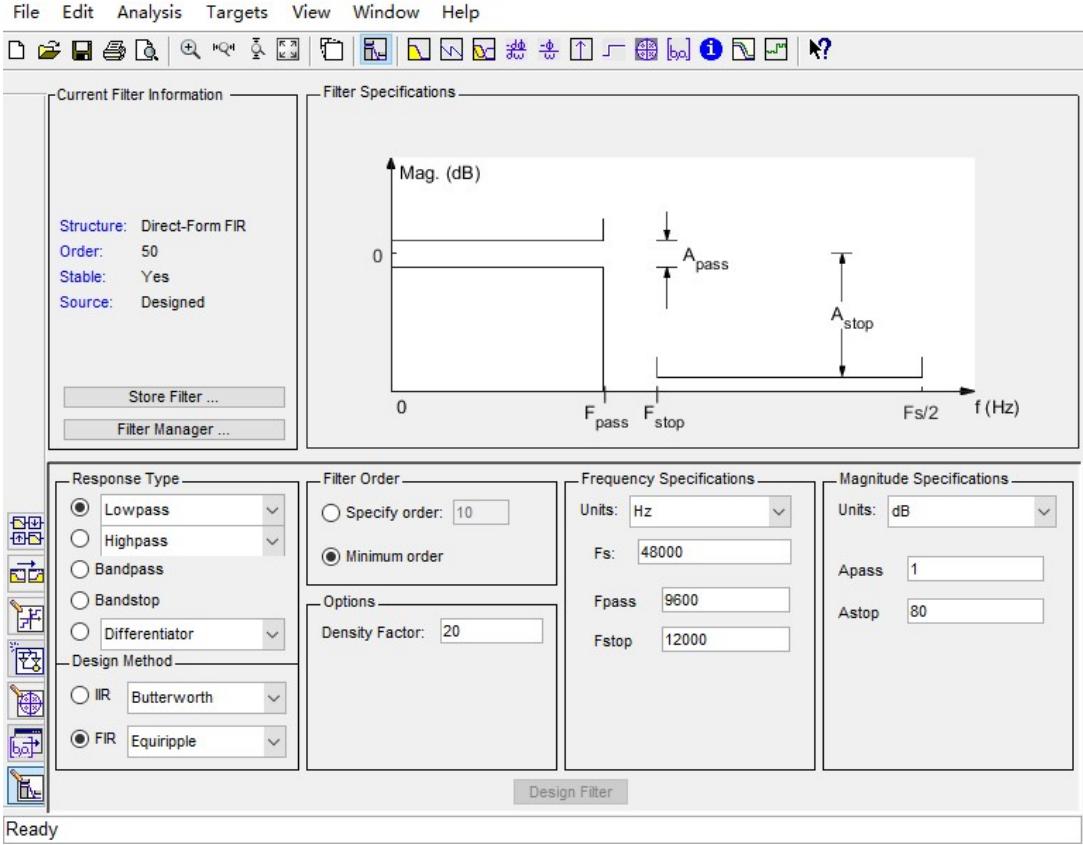

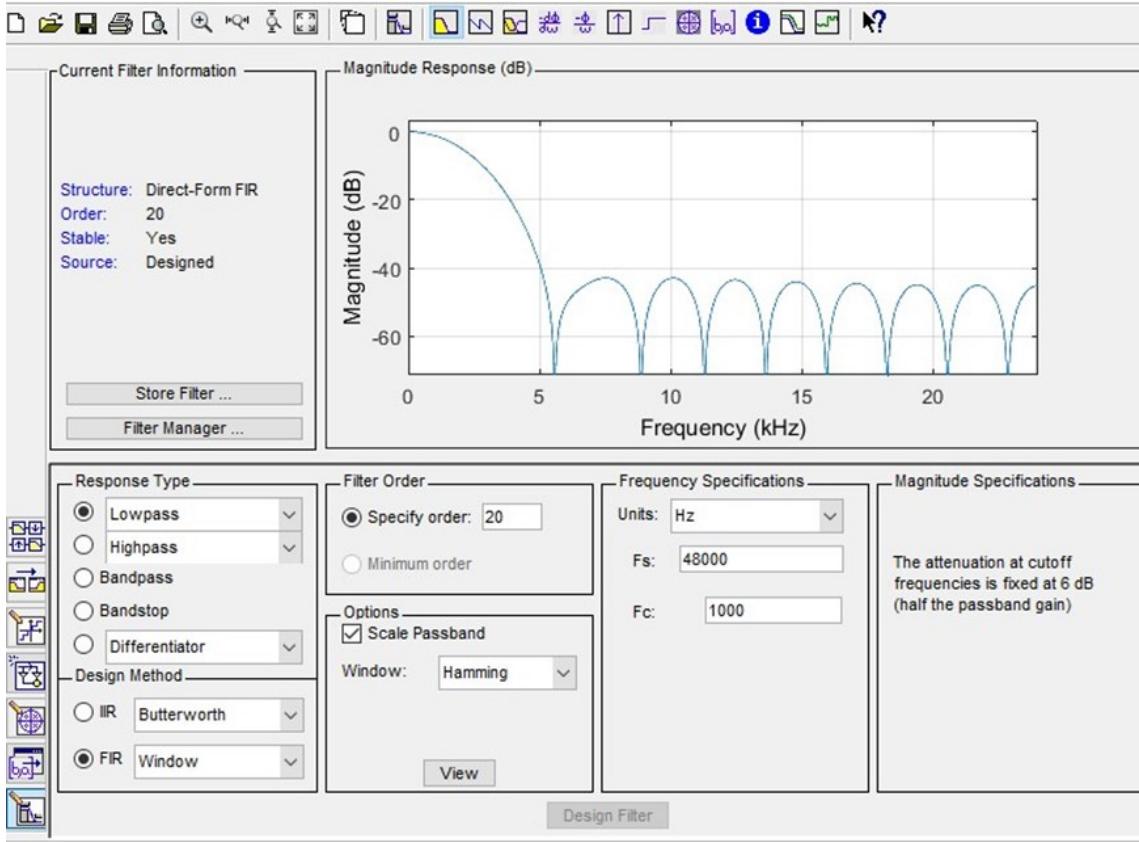

在 matlab 的命窗口输入 fdatool 打开 Filter Designer 工具箱;

-

选择滤波器设计的参数,如低通、fir、窗函数设计法,选择为 hamming窗,采样率 48000Hz,截止频率 1000Hz,阶数 30 阶,点击 Designer Filter进行滤波器设计;

-

设计完后,再导出滤波器系数;

-

选择类型为 Single-precision float,再导出文件。

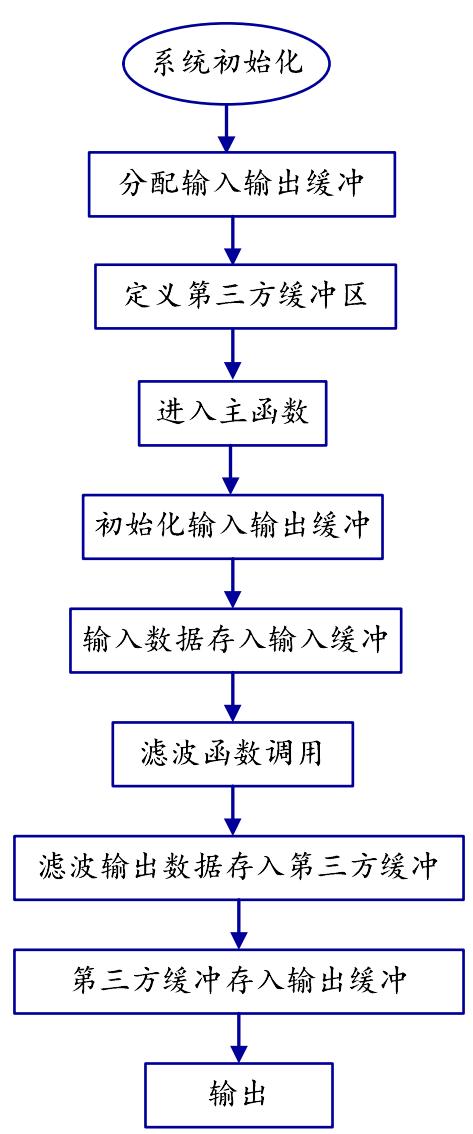

FIR滤波器的程序编写的流程图如下所示:

图5 FIR滤波器编程流程图

在信号实时处理实验中,主函数 Audioloopback.c()中,先用 fir_init ()对滤波函器进行初始化设置,再对输入输出缓冲进行初始化,然后通过偏移地址将输入输出缓冲区的内容清空,再把输入信号存储在输入缓冲区,直到填充满整个输入缓冲区,再将噪声与输入信号叠加存放在缓冲 IN 中,接着调用 fir_fr16 ( )滤波函数对 IN 缓冲区内的信号进行处理,将处理好的数据存入第三方数组 OUT[]中,最后将 OUT[]内的值放入输出缓冲区,再输出。

实验效果:

由于该课程设计能将数字信号处理所学知识点直接通过动手在示波器直观地看到信号变化的过程,对学生的实验设计、 工程开发能力能够进行非常有效的培养。 本课程的实验效果如下:

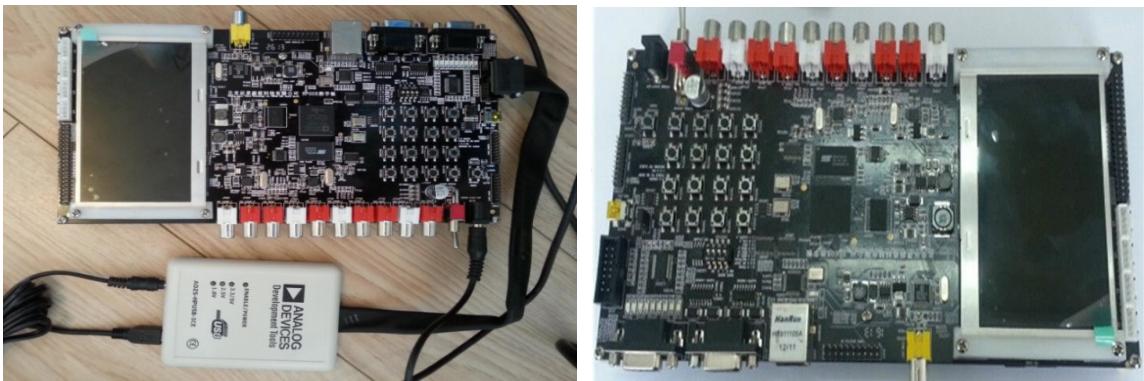

图 6 实验所用的 BF609 教学板

图7 信号发生器与接线口的图

图8信号发生器与实验板连接图

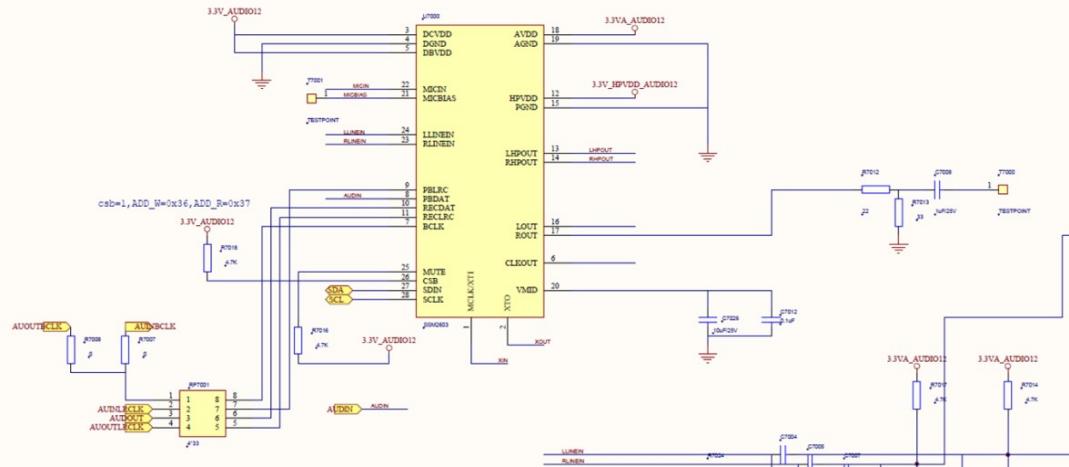

图 9 BF609 教学板上 SSM2603 电路连接图

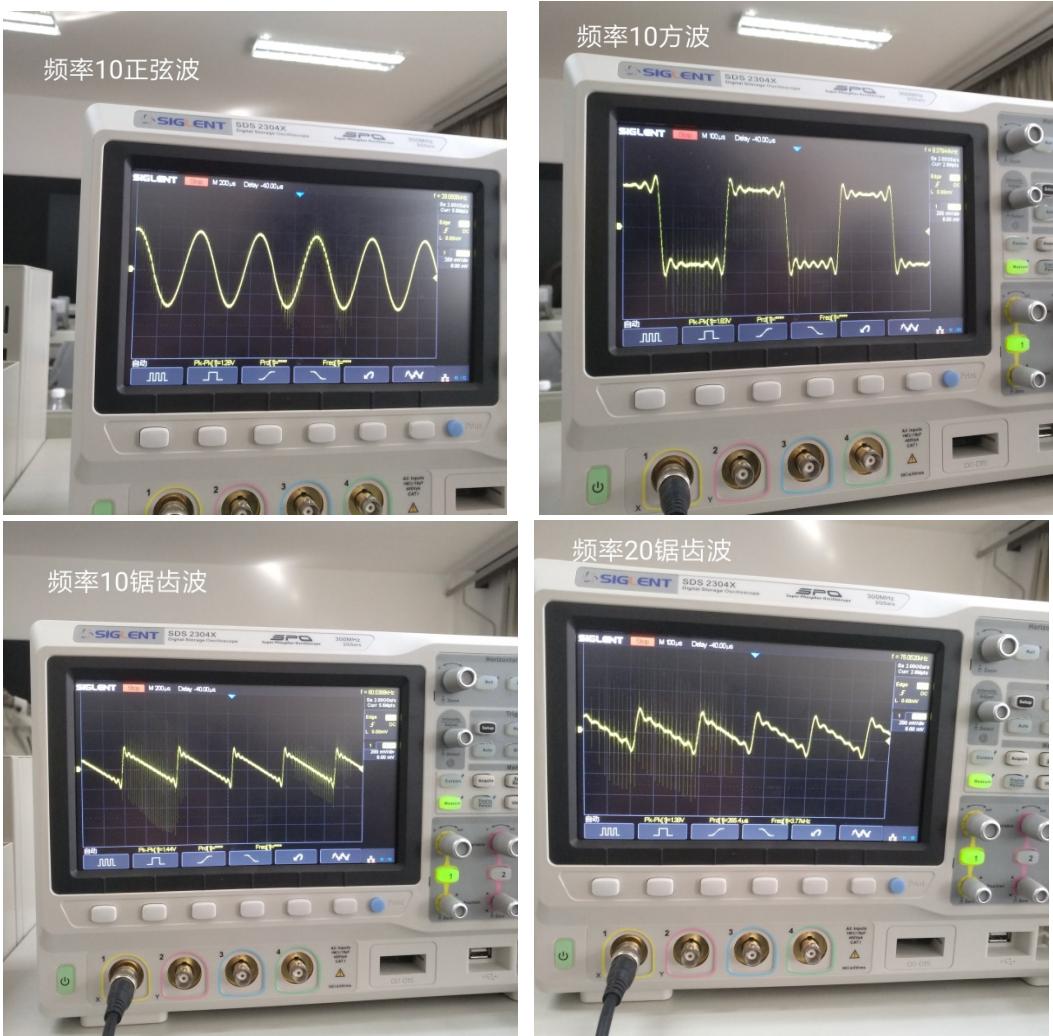

图 10 示波器上显示的各种信号

图 11 输入正弦波信号:5kHz、86mV

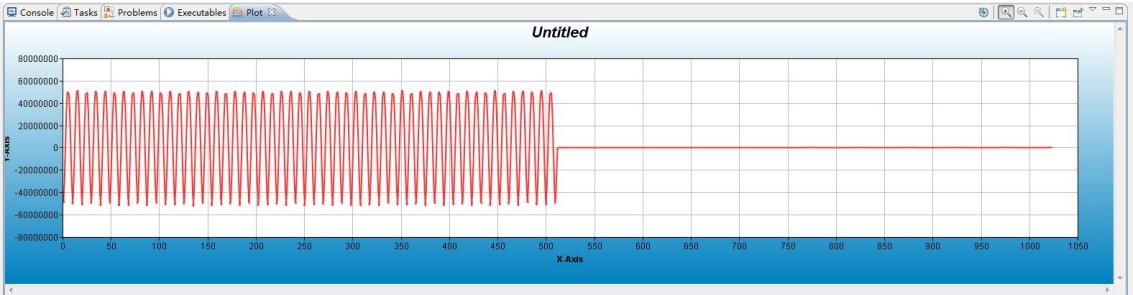

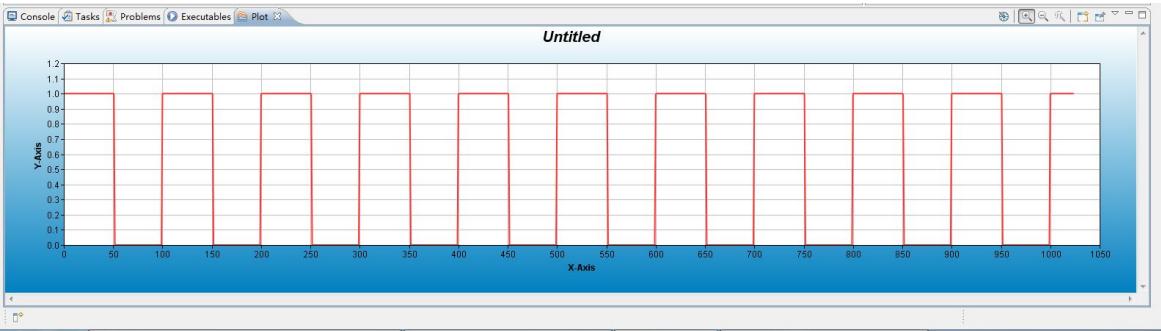

图 12 pw 调制波形:占空比为 $5 0 %$

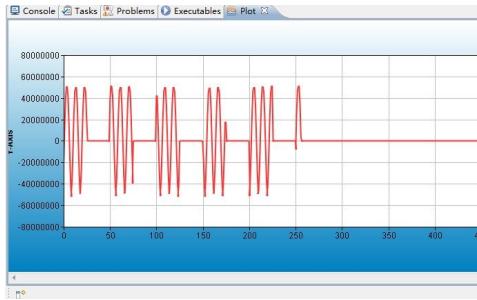

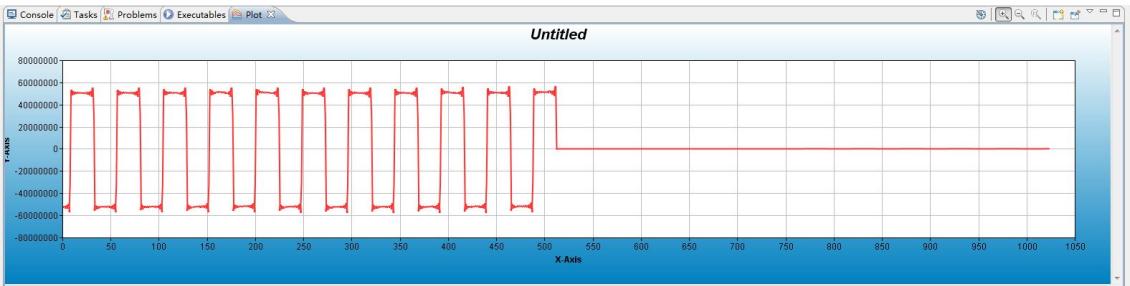

图 13 调制输出波形

图 14 输入方波:1kHz、 $8 6 \mathrm { m V }$

图 15 pw 调制波形:占空比为 $5 0 %$

图 16 调制输出波形

图 17 滤波器设计软件界面

一、实验目的

二、实验所用仪器(或实验环境)

二、实验基本原理及步骤(或方案设计及理论计算)

四、实验数据记录(或仿真及软件设计)

五、实验结果分析及回答问题(或测试环境及测述纯用)

一、实验目的

本实验利用ADI-BF609实验板的硬件资源,完成了对信号的采样和滤波公析验中提供了基本的FIR滤波器程序,通过窗函数法来设计滤波器,清冲义一直接在开发坏境(plot)上看到。通过这个实验来加深对数字滤波这种信目可以方法的理解。