虚实结合的组合逻辑电路实验黑盒设计

实验题目:虚实结合的组合逻辑电路实验黑盒设计

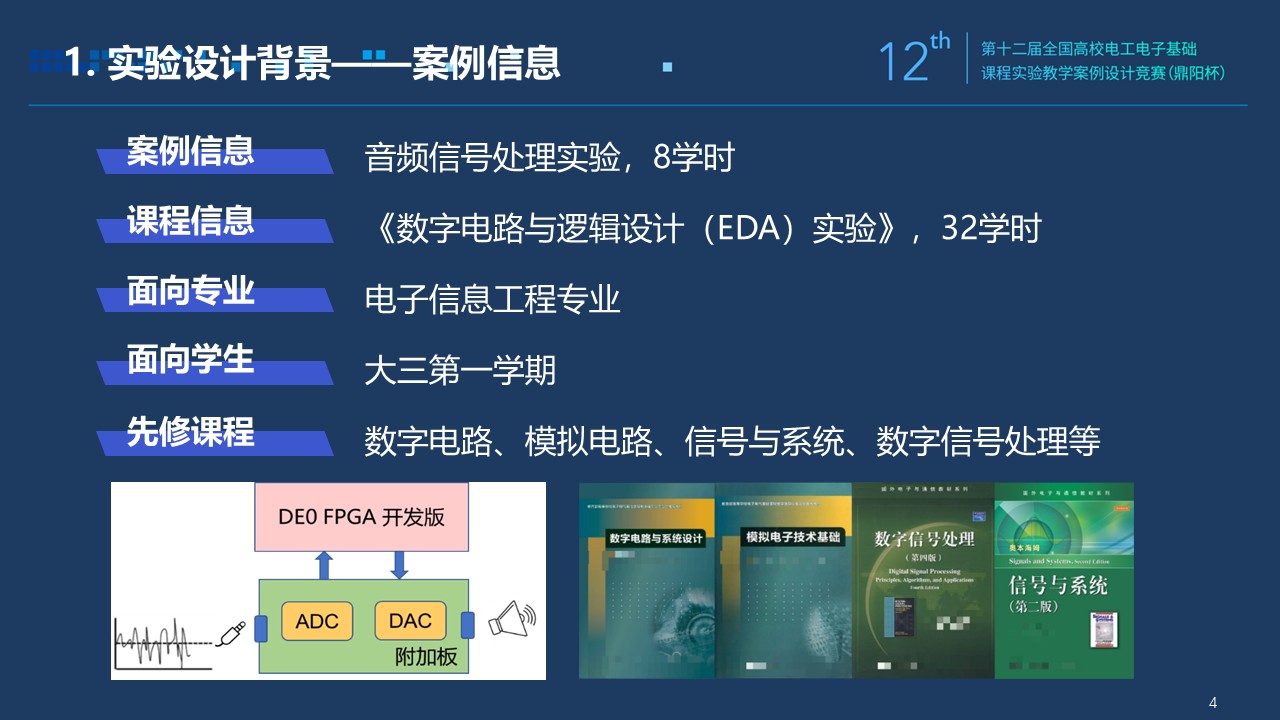

1. 课程简要信息

课程名称:虚实结合的组合逻辑电路实验黑盒设计

课程学时: 32

项目学时:(课内 4、课外2)

适用专业:(电子类)

学生年级:(二年级、第一学期)

2. 实验内容与任务(限 500 字,可与“实验过程及要求”合并)

项目需要完成的任务(如需要观察的现象,分析某种现象的成因、需要解决的问题等);是否设计有不同层次的任务。

1)以FPGA综合实验板为实验平台,装载定制的组合逻辑黑盒码流文件,通过输入不同的逻辑变量组合,观察LED或示波器显示结果,进而分析黑盒文件中设置电路的真值表及逻辑函数式;

2) 根据分析出的逻辑函数式,以中小规模集成电路模型为基础,设计实现相同功能的逻辑电路;

3. 实验过程及要求(限 300 字)

如对学生在实验过程中在需求分析、资料查询、自学预习、思考讨论、方法设计、进程规划、软件仿真、平台构建、器件选择、表格设计、现象观察、数据测试、问题分析、总结报告、验收答辩、演讲交流等各方面的要求。

1)登录实验黑盒文件管理网络平台,下载网络平台随机抽取并分发的组合逻辑码流文件 A,内置一个逻辑门(与、或、非、与非、异或等 8种常用基础组合逻辑之一),作为被测试电路;

2) 学生通过电脑将文件 A 装载到 FPGA 综合实验板,构成黑盒电路 A,通过板上的开关输入和LED 指示灯,进行数字电路的静态测量,记录真值表,分析被测电路的逻辑功能;

3) 再次登录网络平台,下载内置 3 输入组合逻辑的码流文件 B,并装载到 FPGA 实验板,实现黑盒电路B;

4) 通过FPGA的扩展端口代替逻辑电路的LED显示,再由示波器以“多路信号的波形测量”规则观察黑盒电路B 输入输出波形,完成数字电路的动态测量,记录真值表,分析逻辑函数;

5) 黑盒电路 A 和 B 的测试结果上传网络平台,网络平台自动验证判断正确性,提高实验反馈效率;

6) 文件A一共设定10种,文件B一共100多种,网络平台随机抽取并分发,以促使实验学生独立完成实验测试与分析;

7) 根据分析获得的黑盒电路 B 逻辑函数,基于 Multisim 仿真软件平台,以与非门或译码器,数据选择器等中小规模常用组合逻辑器件的模型为基础构件,设计实现完成相应功能的电路。

4. 相关知识及背景(限 150 字)

项目涉及所需的知识方法、实践技能、应用背景、工程案例。

这是由传统数字电路验证实验改进而来的实验设置,面向刚上手数字电路的学生,需要学生掌握基本逻辑函数的各种表达形式,学习数字电路中的动态及静态测量手段,通过仿制电路

来学习数字电路设计。通过未知的黑盒功能探索,增强枯燥的传统验证实验的趣味性,可探索性。

电路设计以中小规模模块的原理图方式建于 Multisim 平台,并后台调用 vivado 完成综合至装载全过程。

5. 实验环境条件

项目实施需要实验资源,包括实验装置功能、实验仪器设备、设计软件工具、主要电子元器件等。

网络平台,提供黑盒文件的存储,分发,实验结果的收集与判断;

Basys3 或其他 FPGA 综合实验板;

示波器,万用表;

计算机,Multisim14.X 教育版,vivado2014~ vivado2018,digilent adapt;

6. 教学目标与目的(限 150 字)

如学习、运用知识、技术、方法等;培养、提升技能、能力、素质等。

在探索场景下,完成验证型实验的提升实验;掌握静态、动态等数字电路实验基本测量手段;熟练运用数字电路理论中的各种逻辑表达方式,运用卡诺图化简,以及组合逻辑电路的设计方法。培养组合逻辑电路测量,分析及设计能力。

7. 教学设计与实施进程

课堂知识讲解、方法引导、背景解释;实验中的方法指导,问题设置、思路引导等。教学模式、实验渠道、研讨主题、观察节点、验收重点、质询问题等方面设计等。实验实施进程的各个环节(如任务安排、预习自学、现场教学、分组研讨、现场操作、结果验收、总结演讲、报告批改等)中教学设计的思路、目的,教师、学生各自需要完成的工作任务,需要关注的重点与细节。

本实验是数字电路实验的第一步,是对传统的验证实验的提升,同时不会过度拔高实验要求。

实验过程是一个比较完整的从分析到设计的过程,为完成如此的实验过程,实验实施由基于阅读资料和演示视频的课前预习、实验技术要点的课堂强调、静态动态测量与结果验收、同功能电路设计及验收几部分构成。

由于是数字电路实验的首次实验,有大量的实验背景与实验技术涉及,而本实验配置的学时数为4学时,因此需要采取课前预习与课堂讲授相结合。相关内容描述及课前课上的分配如下:

知识要点:

1) 软件使用环境介绍,需要介绍的软件环境包括 Multisim14 和 Digilent adept system。其中 Digilent adept system 是一个编程器软件,黑盒文件装载到 FPGA 综合实验板以完成实验的重要工具。课堂上需作 Adept 操作演示。

2)作为一个优秀的仿真软件,同时 Multisim14教育版提供了使用方便的,原理图式的 FPGA设计实现功能。Multisim 提供了百余种带有 HDL 代码的 74 系列和 4000 系列集成电路的原理图模块,用以实现原理图设计模式下的 FPGA电路设计。由于前序课程已经使用过 Multisim软件,所以此处仅介绍如何进入 PLD设计模式,已经简单介绍逻辑门与常用组合逻辑模块,以及后台调用 vivado 实现向 FPGA 综合实验板导出电路的向导操作流程。该部分介绍通过预习资料及视频方式提供预习自学。

3)FPGA综合实验板 basys3提供了黑盒测试,以及设计原理图导出,电路功能具现的平台。较详细的资料通过预习资料提供,课堂仅提及测试及设计必须的部件。

4)黑盒电路 A 采取静态测量,实验讲解除说明电路涉及的外设资源,还简述 LED 和万用表电平测量,填表格式。

5) 黑盒电路 B 采取动态测量,常规双踪示波器无法同时显示输入输出 4 路信号,因此需要着重介绍示波器触发在多路信号测量中的使用技术,及波形绘制规范。

6)在理论课学习完成的基础上,设计阶段的任务难度并不高,因此讲解时更注重有利于故障排除的设计规范性:如布线是否美观不凌乱,布线时是否采取线色含义化。

7) 即使再简单的电路,设计实现时都有可能出现故障导致失败。常见易导致设计失败的故障,以及排查错误的一般方法,在预习资料中一并给出,以作为备查的技术资料。实验完成要点讲解约使用50分钟。考核节点:整个实验一共有 3 个考核节点:

1) 静态测试一般占用 30分钟,教师手工考核仅涉及记录数据的格式规范,静态测试结果的逻辑判定正确性由计算机平台自动判定,。

2)静态测试一般占用 50分钟,教师手工考核以动态测试的示波器操作过程及波形记录规范性为主,逻辑式正确性由计算机平台自动判定。

3) 设计电路一般占用 70 分钟,考核以设计电路实现逻辑是否与分配电路一致,以及原理图布线质量为验收内容。

8. 实验原理及方案

实验的基本原理、设计依据、完成任务的思路方法,可能采用的方法、技术、电路、器件。

1) 静态测试

静态测试硬码文件群一共约 10个文件,分别内置同相缓冲器,非,与,或,与非,或非,同或,异或八种常用逻辑模块中一种,输入端不超过 2。装载网络平台随机分发的测试文件至 FPGA,进行静态测试,并判断模块内包含的是哪一种常用逻辑模块。

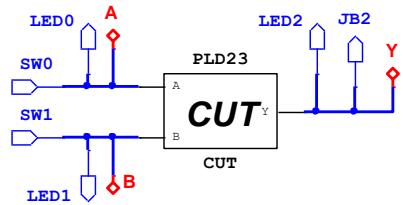

静态测试的电路原理图如图:

被测模块置于黑盒 CUT(circuit under test)之中;

逻辑点3个,分别对应信号 A、B 和输出Y;

输入设备2个,SW0和 SW1,接逻辑点A和B;

测试端口4个,分别对应3个逻辑点,每个逻辑点连接 1个 LED,输出逻辑点连接线路输出;

3 个 LED $\left( 0 ^ { \sim } 2 \right)$ 可直接观察逻辑状态,对应关系于图中可见;

Pmod中JB2线路输出,用于万用表电压测试。

电路特点:拨码开关只能提供静态逻辑 0 和逻辑 1 电平,只需用万用表即可测量判断逻辑。

2) 动态测试

动态测试硬码文件群一共约 100 多个文件,分别内置一个 3 输入组合逻辑电路。根据网络平台分发,装载文件至FPGA,进行动态测试,并判断其逻辑式。

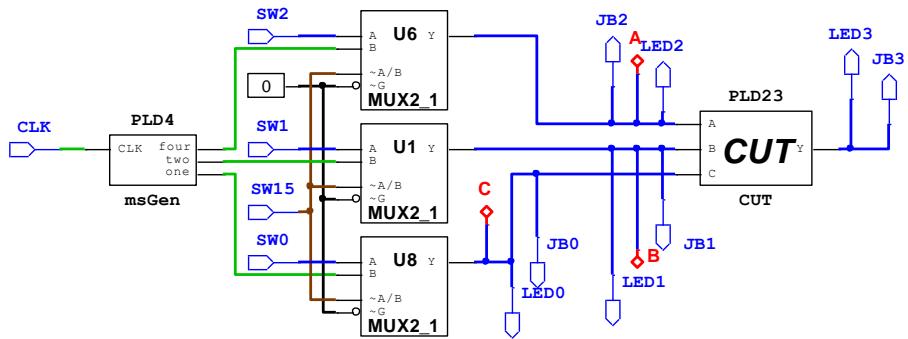

动态测试的电路原理图如图:

逻辑点 4 个,分别对应信号 A,B,C 和输出 Y;

输入设备4个,SW0,SW1和SW2,经数据选择器接逻辑点 A,B,C,SW15控制端 S,确定静态测试状态 $\mathrm { S } { = } \mathrm { L } ,$ )和动态测试状态 $( \mathrm { S } { = } \mathrm { H } )$ ;

测试端口 8 个,分别对应 4 个逻辑点,每个逻辑点连接 1 个 LED 和 1 个线路输出;

4 个 LED $\left( 0 ^ { \sim } 3 \right)$ 可在静态测试直接观察逻辑状态,对应关系于图中可见;

Pmod 中 JB $\left( 0 ^ { \sim } 3 \right)$ 线路输出,用于动态测量时,示波器观察波形,对应关系于图中可见。

动态测试时,A,B,C端输入中频(大于kHz数量级)。

电路特点:静态测量时,所有输入逻辑值需要通过手动拨码开关设置,效率低下;动态测量时,输出信号不断在逻辑 0 和逻辑 1 之间切换,由于视觉暂存现象,无法通过 LED 观察电平变化,必须使用示波器类设备观察波形。

3) 电路设计

根据已分析得到的 3 输入逻辑函数,在 Multisim 软件中设计相应的逻辑电路,并装载到 FPGA综合实验板中,验证其正确性。

实验过程举例:

1) 已获取码流文件 A,打开软件 adpet,如图:

2) 检查右上角 connect 右侧下拉框,是否显示 Basys3 字样,如果没有,表示硬件未连接,或硬件电源未开等硬件故障。如正常显示,继续下一步。

3) 点击中间 Browse…,找到从硬盘上找到码流文件 A

4) 点击 program…,等待进度条滚动结束,即可观察实验板。

5) 拨动 SW0,SW1,依次为“下下”、“下上”、“上下”、“上上”,观察 LED0~LED2(其中 LED0和 LED1 对应 SW0 和 SW1),亮为 1,灭为 0,记录结果如下表:

| LEDO | LED1 | LED2 |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

6)由此判定,电路逻辑为异或逻辑。

7) 根据平台抽取获得文件 B,进行 $1 ^ { \sim } 4$ 步,装载黑盒电路 B;

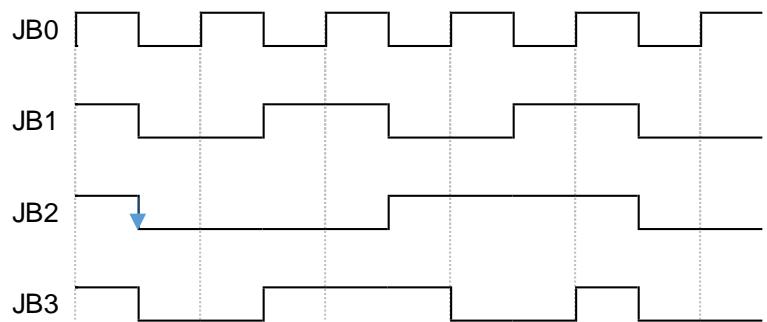

8) 依次测量 PMOD 扩展端口 $\mathrm { J B 0 } ^ { \sim } \mathrm { J B 2 }$ ,频率分别为 $1 0 \mathrm { k H z }$ ,5kHz, $2 , 5 \mathrm { k H z }$ 时钟方波,根据多信号示波器测量技术,选择 $2 , 5 \mathrm { k H z }$ 的JB2连接示波器触发通道 CH1,再用CH2依次测量JB0,JB1和JB3,对齐时序,绘制出波形组。

9) 标定逻辑值,转换真值表,并做化简可得最简逻辑式 $\mathrm { B } 3 =$ JB2 ∙ JB1 ̅̅̅̅̅ ∙ JB0 ̅̅̅̅̅ + JB2 ̅̅̅̅̅ ∙ JB1 + JB1 ∙JB0;

10)创建新“设计”,菜单 $\twoheadrightarrow$ 文件 $\twoheadrightarrow$ 新建,弹出新设计对话框,选择空设计,再点击创建,准备PLD 设计;

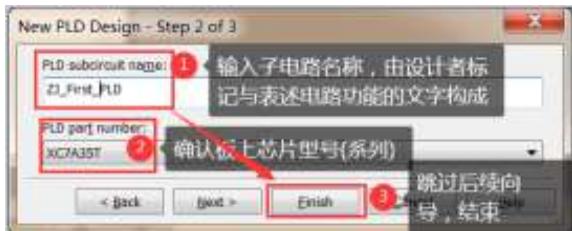

11)新建PLD 模块,菜单 $\twoheadrightarrow$ 添置 $\twoheadrightarrow$ 新建PLD 子电路,这是新建PLD 模块的唯一入口;

12)进入向导第一页,单选标准版配置,下拉框选 Digilent Basys3 板,点下一步;

13)进入向导第二页,给 PLD 电路起个名字;

14)跳过端口设定直接完成(端口设定可以在编辑时直接添加、删除);

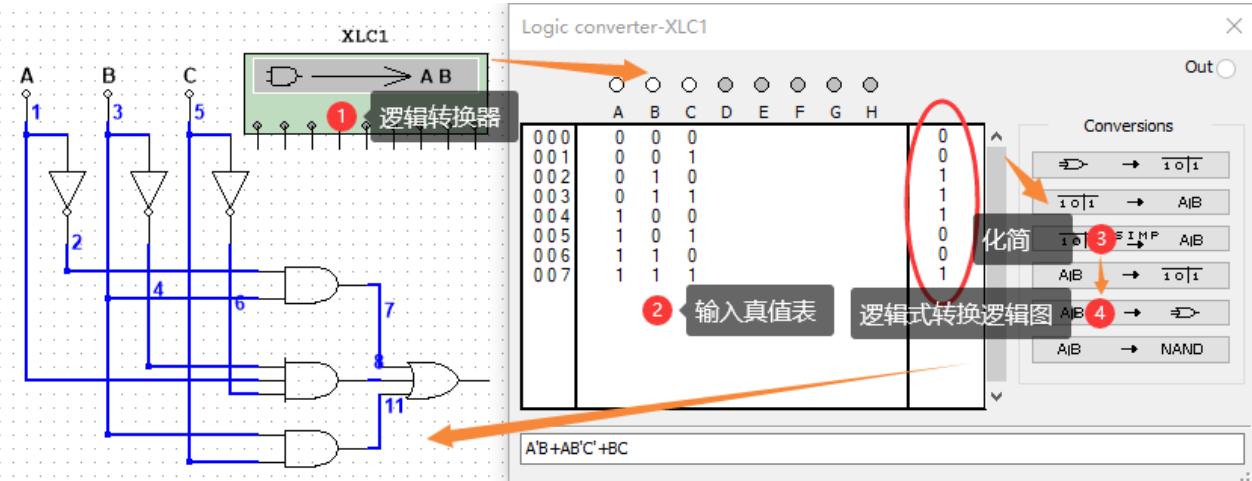

15)电路图区新添了模块,在模块内,通过逻辑转换器自动生成目标任务原理图。

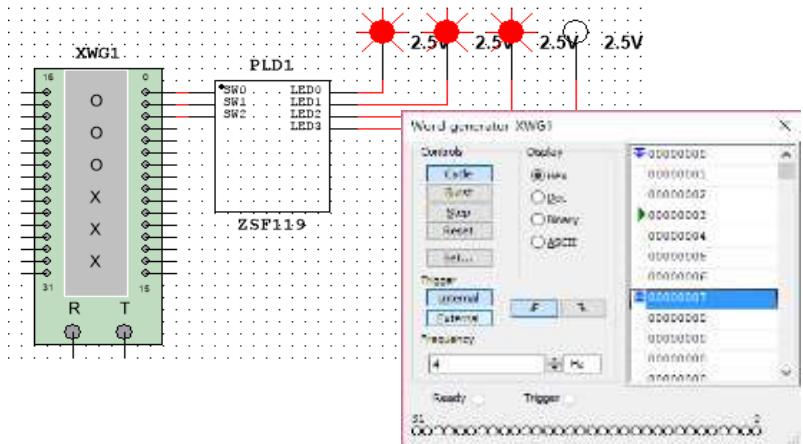

16)通过图纸下方选卡或设计工具栏导航,切换至顶层电路页面,添加仿真测试用的字发生器与测试球,设置合适的字发生器循环内容,保存。

17)点击交互仿真按钮。

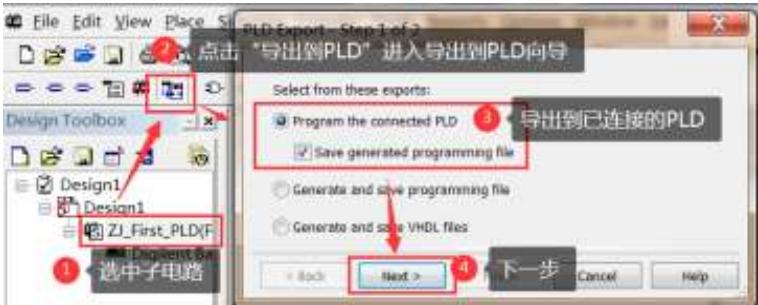

18)选中子电路图纸,在工具栏找到并点击“导出到PLD”的图标,进入下载向导,见图右侧。

19)选择对已连接的PLD 设备进行编程,并保持勾选住保存生成的硬码文件的选项。点击下一步,进入向导步骤二。

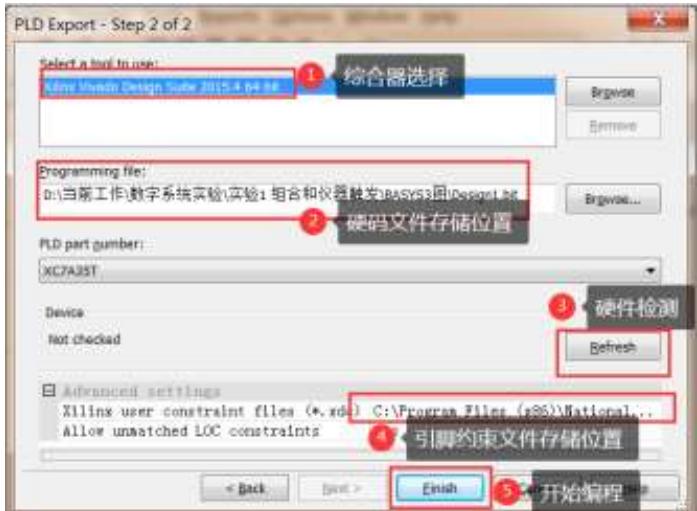

20)下载向导步骤 2 里,完成几个参数的确认后点击完成,开始后台的编译、综合、具现及装载:

21)经过Multisim后台调用vivado,完成综合、具现、装载全过程,即可在综合实验板上个验证设计。

9. 实验报告要求

需要学生在实验报告中反映的工作(如:实验需求分析、实现方案论证、理论推导计算、设计仿真分析、电路参数选择、实验过程设计、数据测量记录、数据处理分析、实验结果总结等等),如:

实验报告需要反映以下工作:

1) 逻辑门测试真值表

2) 逻辑门功能判断

3) 组合逻辑电路测试波形图

4) 组合逻辑电路真值表

5) 组合逻辑电路逻辑式判定

6) 同功能逻辑电路设计原理图

7) 电路设计过程故障排除方法(如有)

8) 设计电路验证方法。

9) 实验结果总结

10.考核要求与方法(限 300 字)

考核的节点、时间、标准及考核方法。1)实物验收 $( 2 5 % )$ :波形测量操作规范性,设计电路功能验证,完成时间。

2)实验质量 $( 2 0 % )$ :电路设计方案的合理性,电路原理图设计规范性,包括布线美观度,线色配置。

3)自主创新 $( 5 % )$ :功能构思、电路设计的创新性,自主思考与独立实践能力。

4)实验数据 $( 3 0 % )$ ):真值表,波形图等实验记录的完整性,规范性,正确性。

5)实验报告 $( 2 0 % )$ :实验报告的规范性与完整性。

11.项目特色或创新(可空缺,限 150 字)

项目的特色在于:项目背景的工程性,知识应用的综合性,实现方法的多样性。

《虚实结合的组合逻辑电路实验黑盒设计》实验项目,利用FPGA 的可重复编程等特点,将传统基础验证型实验改造成具有未知探索属性的探究实验,而且人人电路都不同,提高了学生实验完成独立性。

同时也将传统的没有设计性可言的初级设计实验(如投票电路),改造成仿制电路设计,让不同学生领取不同的设计任务,且鼓励多种方式实现电路设计。