通信系统中抗干扰格雷码的设计

实验题目:通信系统中抗干扰格雷码的设计

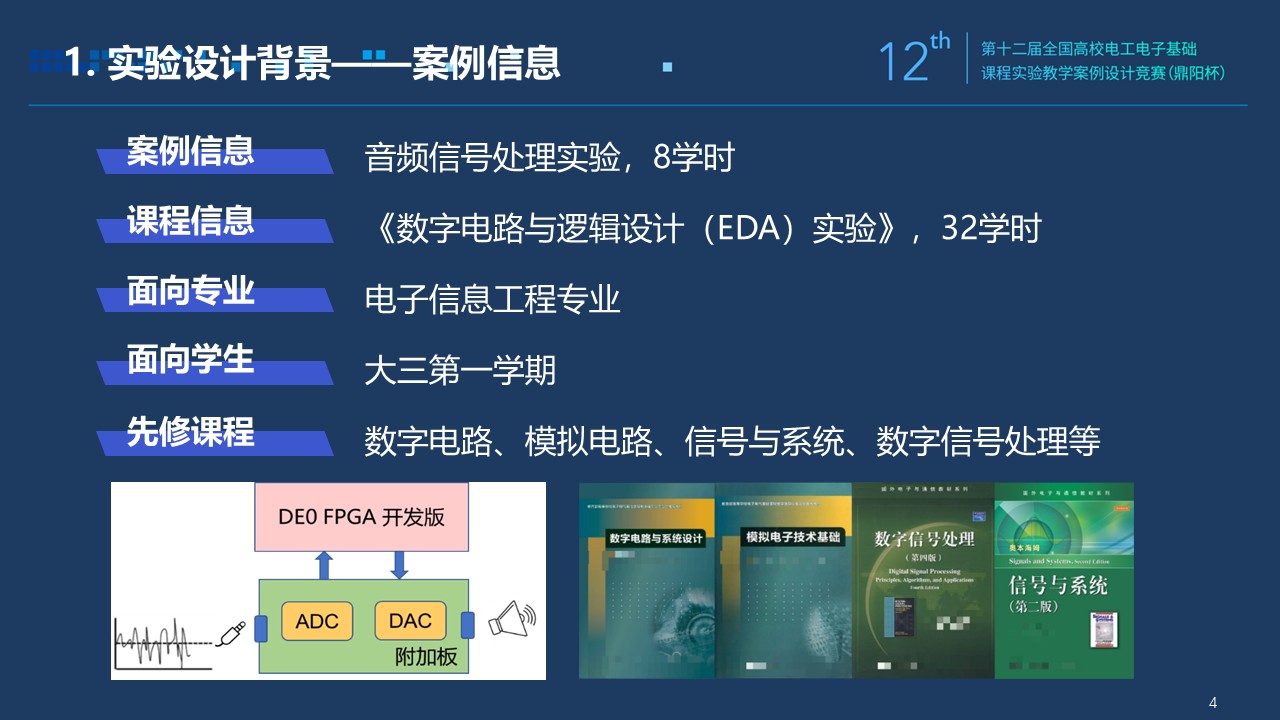

课程简要信息

课程名称:数字电路与逻辑设计

课程学时:56学时/实验6学时

适用专业:电子信息工程、通信工程等

学生年级:大学本科二年级第二学期

实验内容与任务(限500字,可与“实验过程及要求”合并)

实验内容:

1)利用扭环型编码原理进行抗干扰格雷码的设计;

2)对所设计的数字电路进行Multisim仿真测试;

3)在实验箱上进行电路搭建,并进行功能调试;

4)利用VHDL电路设计语言对所设计编码进行编程和仿真。

实验任务:

1)使用4位单向移位寄存器74LS195设计一个M=8的循环格雷码编码;使用Multisim仿真软件设计电路并进行仿真测试,实验箱搭建电路。

2)根据以上分析方法,独立设计能自启动扭环型格雷码的电路接线图;使用Multisim仿真软件设计电路并进行仿真测试,实验箱搭建电路。

3)根据编码特点,画出无效循环的所有编码只变化一位,进入有效循环之内;利用VHDL语言,对所设计编码进行程序设计并仿真,验证结果正确性;

实验过程及要求(限300字)

本实验项目为设计性实验,按照设计流程包括以下几个主要过程:

1)根据设计任务,分析功能要求,确定系统的设计框图;

2)查询相关资料,根据所要求的器件设计满足要求的各功能模块电路;

3)用Multisim仿真软件对各功能模块电路进行仿真测试;

4)把单元电路合理连接成整体电路,对整体电路进行功能仿真;

5)在实验箱上进行电路搭建,并进行结果演示;

6)利用VHDL语言对所设计编码进行程序设计,并进行结果仿真;

7)功能演示,汇报交流;

8)总结设计过程,撰写实验设计报告。

相关知识及背景(限150字)

通过此设计实验,引导学生提升解决实际问题的能力,深入理解基本组合电路、基本时序电路的工作原理及应用方法;提升学生独立设计数字电路、使用Multisim仿真软件、VHDL语言描述电路、改善电路性能等实践能力;引导学生逐步掌握数字电子系统的设计方法,并用工程思想考虑问题并解决问题。

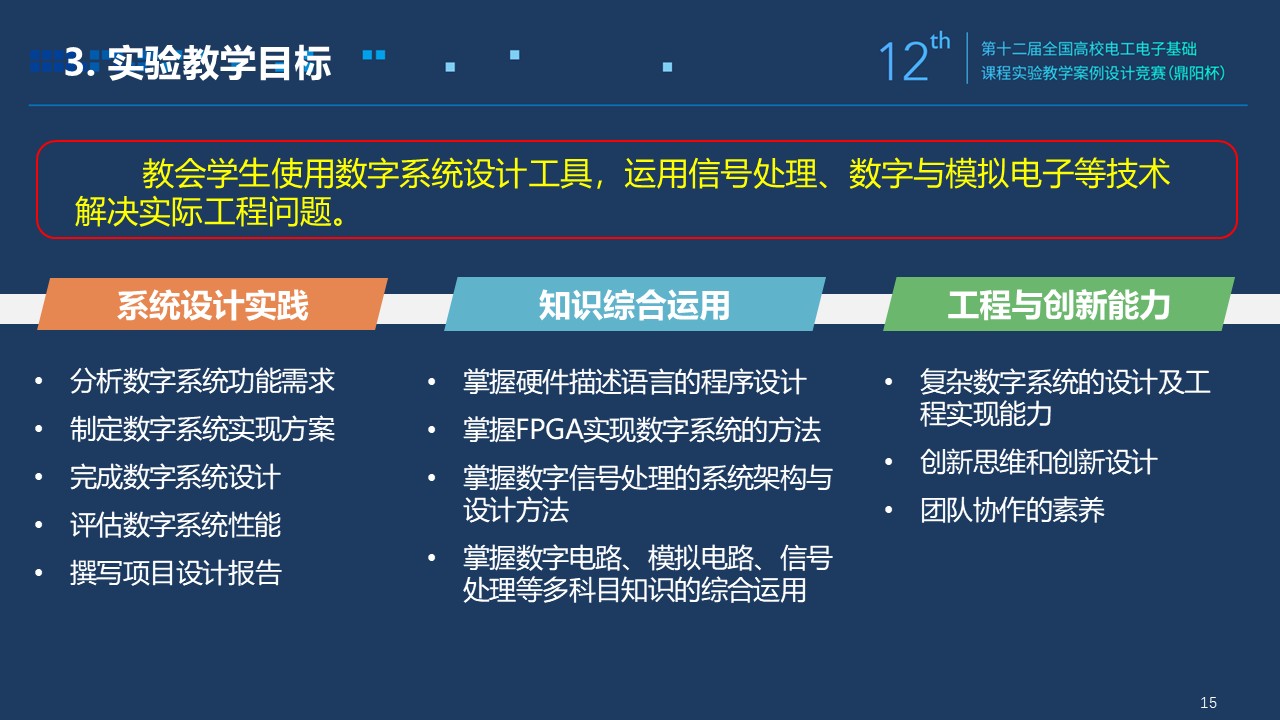

教学目标与目的(限100字)

通过此综合性设计实验,引导学生综合运用所学知识解决实际问题的能力,深入理解基本组合电路,基本时序电路的工作原理及应用方法;提升学生分析电路特性、使用仿真软件及调试故障电路等实践能力;引导学生逐步掌握电子系统的设计方法。

教学设计与引导

本实验是一个综合完整的数字电路应用工程实践项目,需要经历功能分析、系统设计、电路仿真、电路搭建、电路调试以及设计总结等过程。在实验教学中,应在以下几个方面加强对学生的引导:

1)常用组合逻辑电路和时序逻辑电路设计的基本流程;

2)各功能模块所用到的典型芯片及测试和使用方法;

3)各功能模块的设计方法;

4)各功能模块的连接方法;

5)电路设计的弊端和可能出现的错误;

6)Multisim仿真软件的使用方法及注意事项;

7)实验箱的使用方法及注意事项;

8) VHDL电路设计语言的常见问题及排错方法;

8)实验中常见故障的成因及排除方法;

9)实验完成后设计报告写作思路及答辩流程;

10)后续可能使用本设计的典型应用,做到学习结果闭环的方法。

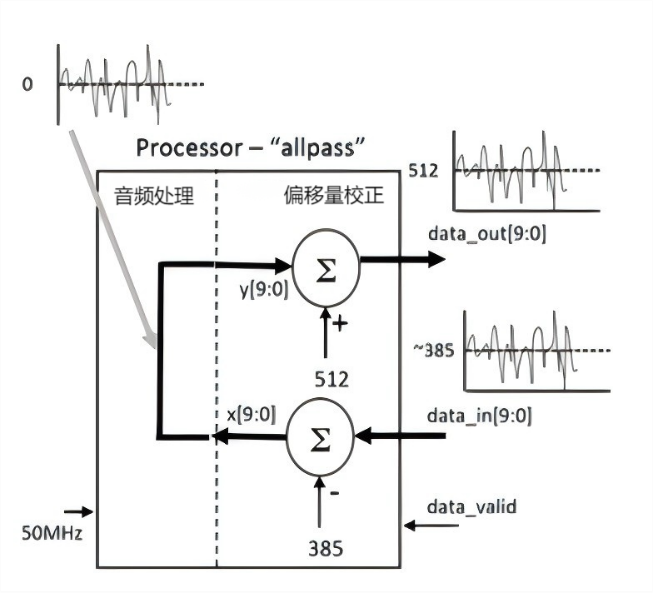

实验原理及方案

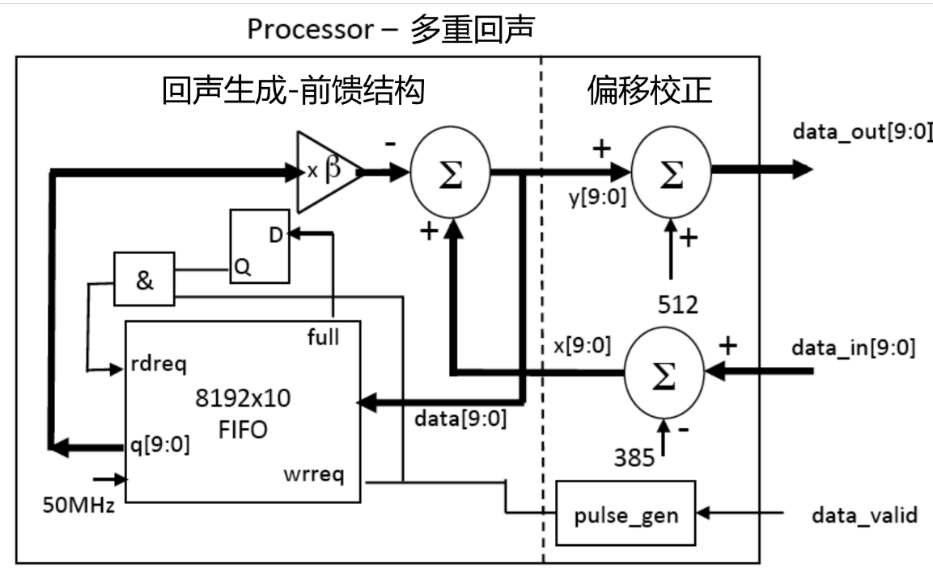

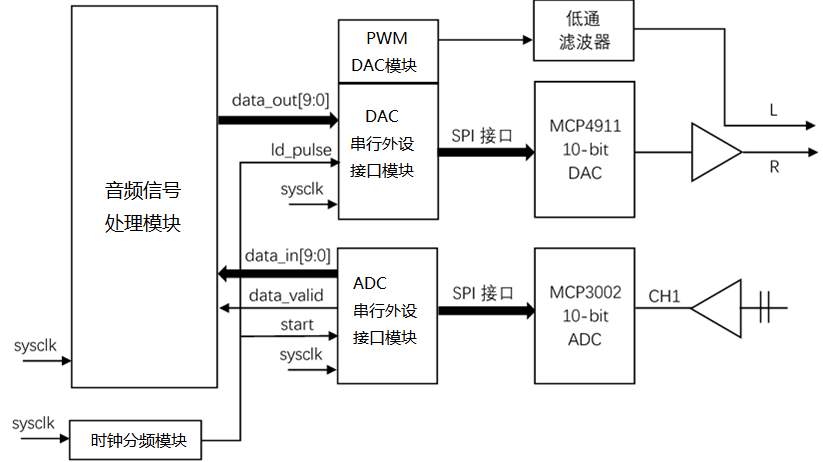

(1)电路的总体设计方案框图

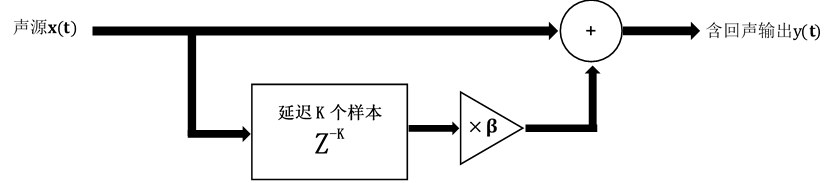

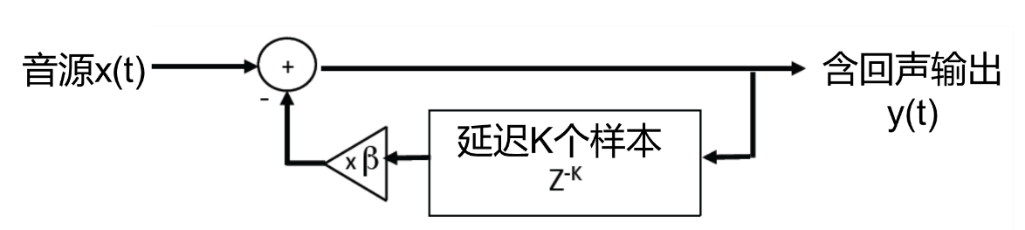

采用工程设计思想,从通信系统的可靠性考虑,设计一个脉冲/只变化一位就可以进入主循环的扭循环格雷码,设计电路可以有效防止干扰,无效编码以高效率、高可靠性进入主循环。

图1 抗干扰雷码的状态转换图

(2)实验方案

给出实验任务:设计产生通信系统中抗干扰性强的格雷码;引导学生得出实验方案:

-

格雷码前后两个状态只差一位,编码后可以提高系统的效率和抗干扰性;

-

数字电路设计较简单,可提供更高的性能,故采用扭环型编码进行格雷码设计。

1)基本实验:不能自启动的扭环型格雷码电路

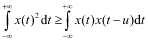

实验原理:4位右移寄存器74LS195,它将移位寄存器的最后一级输出 反馈到第一级的J、

反馈到第一级的J、 输入端,并且J、

输入端,并且J、 输入端连接在一起,构成扭环形移位寄存器电路,可以产生格雷码。产生的格雷码有两个循环状态,不能自启动。

输入端连接在一起,构成扭环形移位寄存器电路,可以产生格雷码。产生的格雷码有两个循环状态,不能自启动。

任务1:使用4位单向移位寄存器74LS195设计一个M=8的循环格雷码编码;

图2 格雷码初步设计接线图和状态转换图

任务2:使用Multisim仿真软件设计电路并进行仿真测试,实验箱搭建电路。

图3 Multisim仿真和实验箱接线

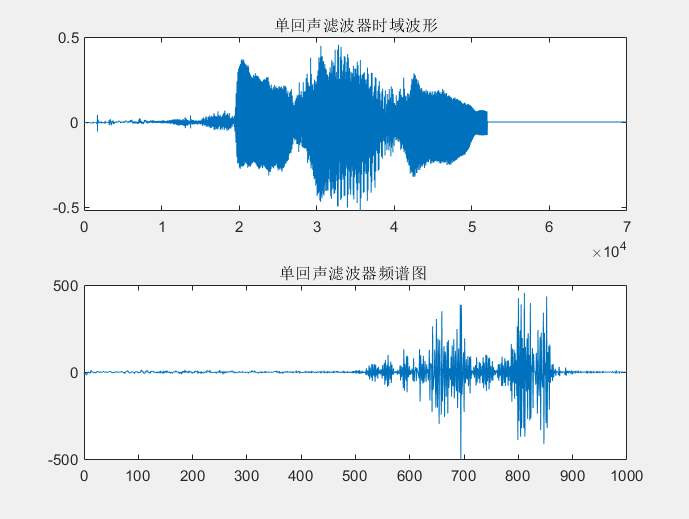

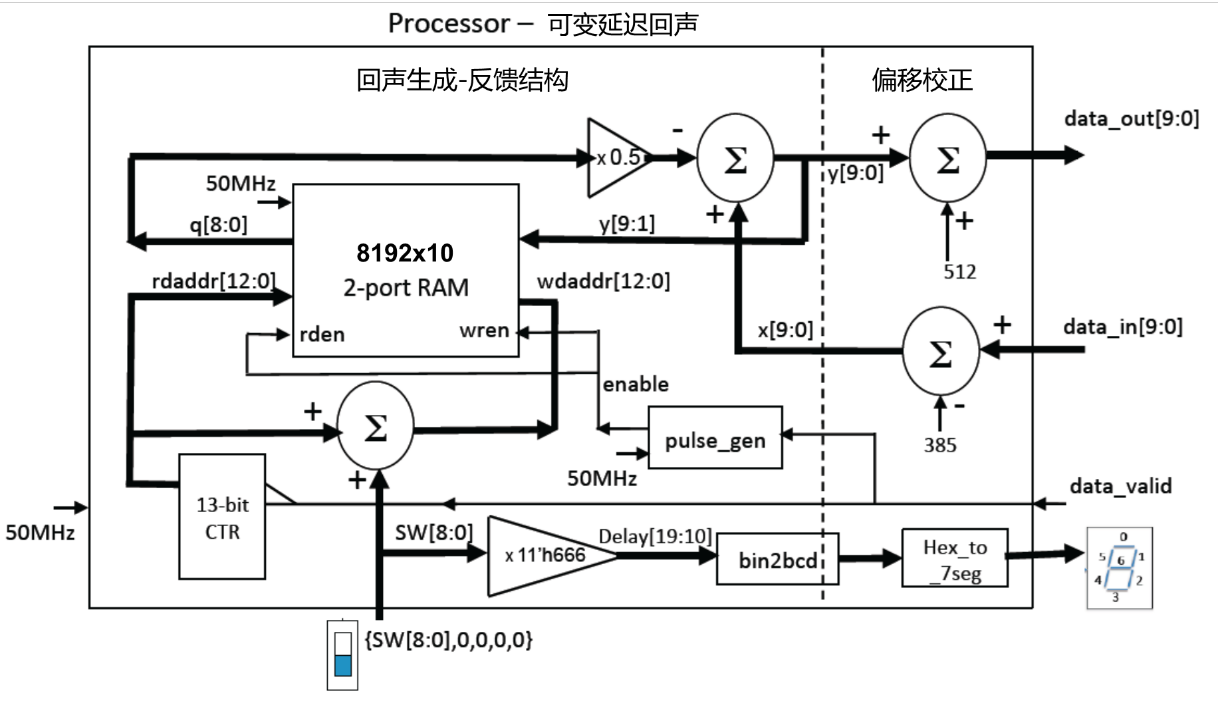

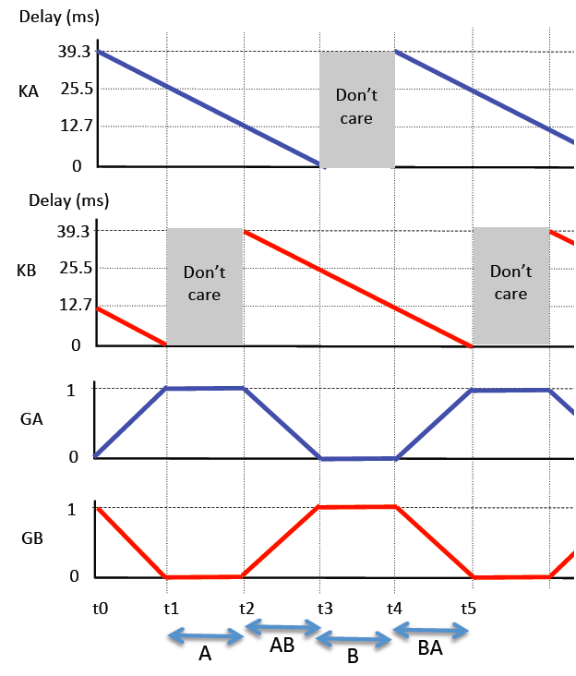

- 拓展实验:自启动扭环型格雷码电路设计

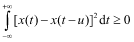

实验原理:在复杂的通信环境下,以上编码有可能进入无效循环的编码状态;

若F

= 是两个循环,一个是正常状态的主循环,另一个是非工作状态的循环。需要修改非工作状态的反馈F的值,使其中至少一个状态进入主循环。但主循环的反馈F不能改变。

是两个循环,一个是正常状态的主循环,另一个是非工作状态的循环。需要修改非工作状态的反馈F的值,使其中至少一个状态进入主循环。但主循环的反馈F不能改变。

| 表1 自启动扭环型态序表 | |||||

| Q0 Q1 Q2 Q3 | F | Q0 Q1 Q2 Q3 | F | ||

| 正常状态 | 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 1 1 0 0 0 1 |

1 1 1 1 0 0 0 0 |

非工作状态 | 0 0 1 0 1 0 0 1 0 1 0 0 1 0 1 0 1 1 0 1 0 1 1 0 1 0 1 1 0 1 0 1 |

1 0(1) 1 1 0(1) 1 0 0 |

根据状态转换表,画出卡诺图和状态转换图。

图4 卡诺图、状态转换图和电路图

任务一:根据以上分析方法,独立设计能自启动扭环型格雷码的电路。

因为更改反馈的状态位置不同,学生设计出多种能够自启动的扭环型格雷码电路:

图5 学生对自启动格雷码的设计图

任务2:使用Multisim仿真软件设计电路并进行仿真测试,实验箱搭建电路。

图6 Multisim仿真和实验箱接线

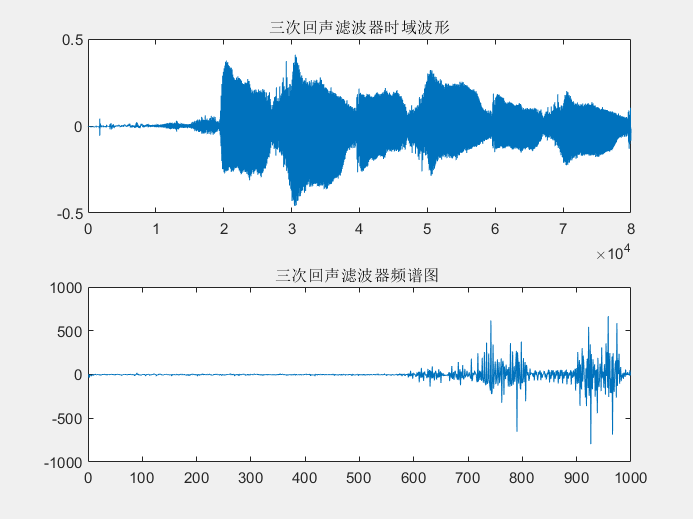

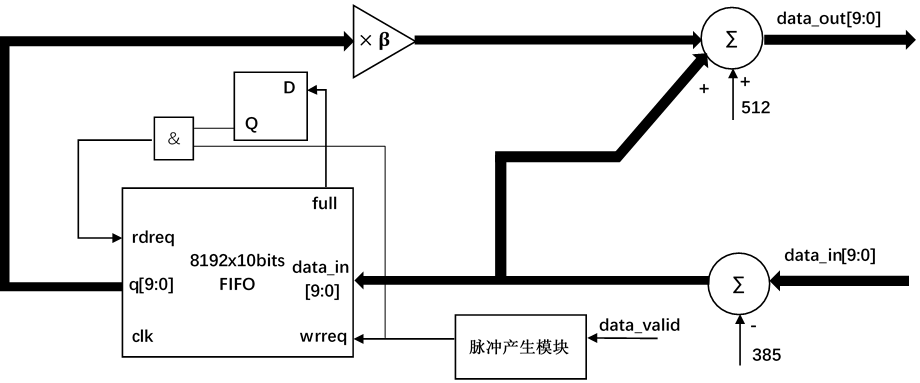

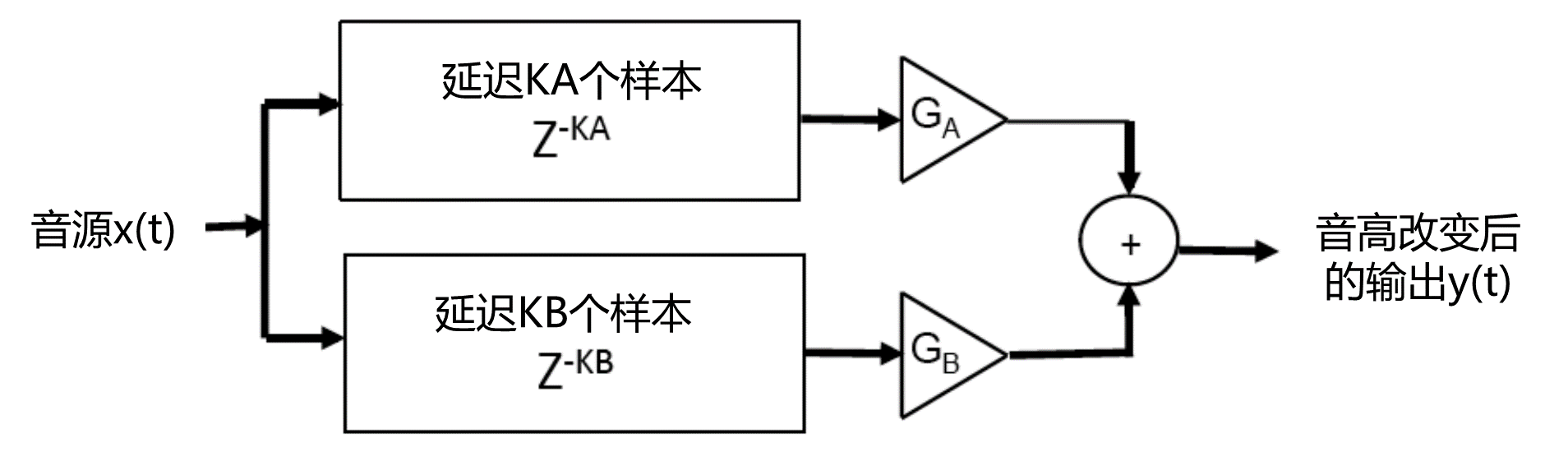

3)创意实验:

实验原理:将无效循环的状态对应的反馈改到最佳,也可能需要多个脉冲才能进入主循环;而在复杂的通信环境下,为使无效编码以高效率、高可靠性进入主循环,最好经历一个脉冲、且只变化一位就可实现。这时一个脉冲就是高效性,只变化一位是高可靠性。

再用卡诺图的方法,使得电路设计非常繁琐,可以考虑VHDL电路设计语言进行实现,这样设计更加简单和灵活。

任务1:根据编码特点,画出无效循环的所有编码只变化一位,进入有效循环之内。

图7 高效/抗干扰强的格雷码状态转换图

任务2:根据自己的状态转换图,进行VHDL程序设计。

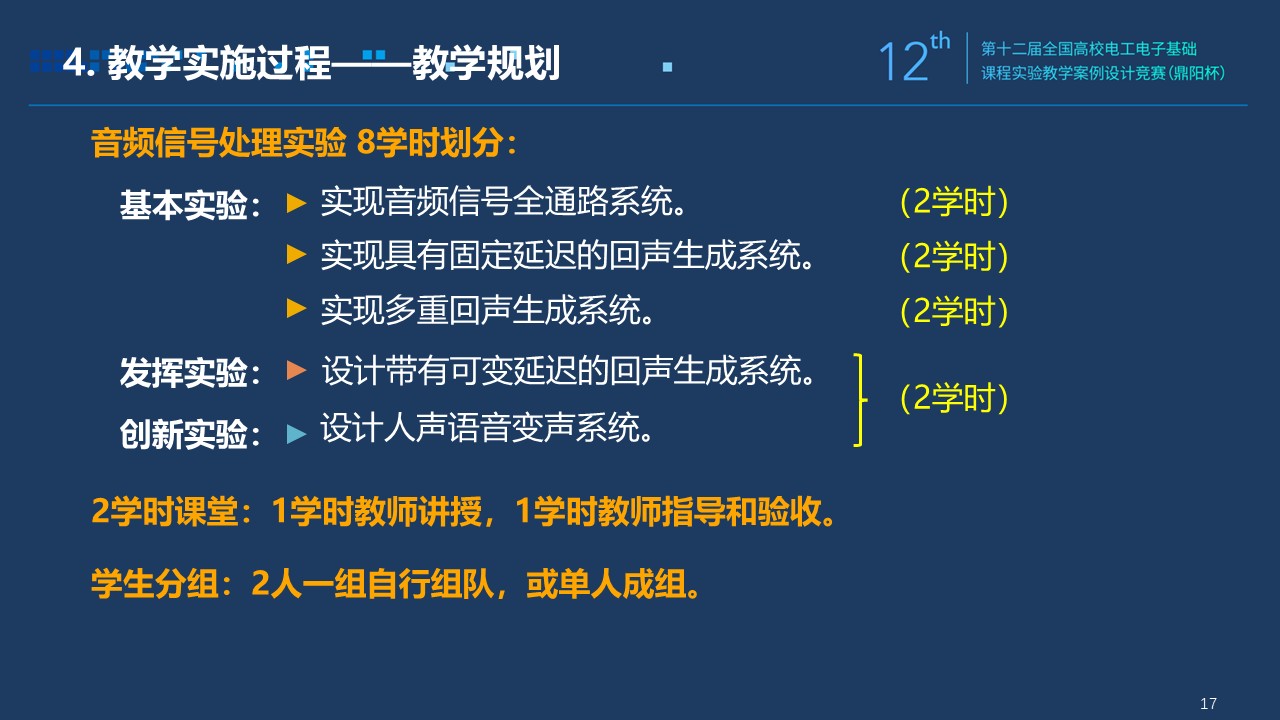

教学实施进程

本实验学时为6学时,具体实施进程如下表所示。

表3 教学实施进程

| 实验阶段 | 教学安排 | 具体内容 |

| 实验准备 | 任务发布 | 1)发放实验任务书,使学生明确实验任务及目标; 2)主要电路设计的原理讲解与设计思路引导。 |

| 资料查找 | 熟悉通信系统模型、组合逻辑电路和时序逻辑电路相关基础知识,学习扭环型序列编码电路的工作原理与设计步骤,学习Multisim仿真软件和VHDL语言的使用。 | |

| 实验过程 | 教学引导 | 1)带领学生回顾与实验有关的理论知识; 2)引导学生对各模块电路进行设计; 3)讲解仿真软件Multisim和VHDL的使用注意事项。 |

| 实践操作 | 1)画出扭环型格雷码的状态转换图和整体设计图; 2)用Multisim 仿真软件对设计电路进行仿真测试; 3)用VHDL语言对设计编码进行程序设计和仿真; 4)在实验箱上进行电路的搭建测试。 |

|

| 问题总结 | 学生分组讨论,说出主要问题,老师引导学生解决,提高学生解决实际问题的能力,增加实践经验。 | |

| 结果验收 | 最后,教师依次测试学生的软件电路和硬件连接结果,学生做答辩讲解并回答问题。 | |

| 课后总结 | 报告总结 | 按照实验要求完成相应的实验任务,总结本次实验结果,按照实验报告格式要求,书写实验报告。 |

| 成绩评定 | 教师对学生实验报告进行批改评分及实验成绩评定。 |

- 实验报告要求

实验报告需要包括以下内容:

1)实验需求分析

描述系统功能,明确实验实现的目标要求及设计任务内容。

2)实现方案论证

画出总电路框图,描述框图中各电路功能模块的实现方案,对方案进行可行性分析。

3)电路设计思路

描述电路设计思路。

4)电路测试及调试方法

介绍电路测试及调试方法。

5)实验数据记录

记录各模块电路的完成情况及整体联调情况。

6)数据处理分析

实验结果分析,记录实验过程中所遇到的各种实际问题及解决办法。

7)实验结果总结

总结本次实验的心得与收获。总结电路设计思路,电路仿真、硬件描述语言和硬线连接与调试的经验。找出本次设计的不足与改进之处。

- 考核要求与方法(限300字)

考核成绩采用分阶段多维度方式,过程性评价与终结性评价相结合最后得出实验成绩。总成绩由各部分成绩的总和构成,同时根据实际情况适当调整部分评分项目。

四个维度分别是:课前/课后的线上作业、课中实践表现、分组答辩展示和实验报告的撰写。

项目特色或创新(可空缺,限150字)

1)在具体电路设计上,通过“以问题为中心”启发式引导学生回顾所学知识并进行设计思考,设计满足要求的电路;

2)循序渐进的设计理念、全面的设计方法和工程应用思想,使学生深入到课堂当中,从思考中获得成长;

3)由浅入深的设计过程,学生能够沉下心来,耐心认真做事,将精益求精的工匠精神潜移默化的融入教学过程。

附:Multisim仿真电路图,实验箱接线图和VHDL程序。

图1 不能自启动格雷码设计电路

图2 能自启动格雷码设计电路

图3 不能自启动格雷码实验箱接线电路

图4 能自启动格雷码实验箱接线电路

VHDL电路设计程序:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_arith.all;

ENTITY count IS

PORT (CP:IN STD_LOGIC;

B:IN STD_LOGIC_VECTOR (3 DOWNTO 0);

Q:OUT STD_LOGIC_VECTOR (3 DOWNTO 0));

END count;

ARCHITECTURE count_arch OF count IS

BEGIN

PROCESS

VARIABLE IQ: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

WAIT UNTIL CP'EVENT AND CP='1' ;

IF B ="1111" THEN IQ :="0111" ;

END IF;

IF B ="0111" THEN IQ :="0011" ;

END IF;

IF B ="0011" THEN IQ :="0001" ;

END IF;

IF B ="0001" THEN IQ :="0000" ;

END IF;

IF B ="0000" THEN IQ :="1000" ;

END IF;

IF B ="1000" THEN IQ :="1100" ;

END IF;

IF B ="1100" THEN IQ :="1110" ;

END IF;

IF B ="1110" THEN IQ :="1111" ;

END IF;

IF B ="1010" THEN IQ :="1110" ;

END IF;

IF B ="1101" THEN IQ :="1111" ;

END IF;

IF B ="0110" THEN IQ :="0111" ;

END IF;

IF B ="1011" THEN IQ :="0011" ;

END IF;

IF B ="1001" THEN IQ :="0001" ;

END IF;

IF B ="0101" THEN IQ :="0001" ;

END IF;

IF B ="0010" THEN IQ :="0000" ;

END IF;

IF B ="0100" THEN IQ :="1100" ;

END IF;

Q <= IQ;

END PROCESS;

END count_arch;