频率合成器的设计

实验题目:锁相频率合成器的设计

1. 课程简要信息

课程名称:电路与电子线路课程设计

课程学时:64学时

项目学时:课内 32学时

适用专业:电子信息类

学生年级:大三第一学期

2. 实验内容与任务(限 500 字,可与“实验过程及要求”合并)

项目需要完成的任务(如需要观察的现象,分析某种现象的成因、需要解决的问题等);是否设计有不同层次的任务。

实验内容:

综合模拟、数字和高频电路等课程的理论知识,设计一款锁相频率合成器,完成电路设计、装配制作和调试测试等实践环节。具体内容包括晶体振荡器、分频器、锁相环路及环路滤波器等内容,要求学生通过查阅资料,设计、安装并调试实现特定功能。

实验任务:

- 查阅相关资料,设计各功能电路,并进行参数计算、电路分析;

- 根据电路图在面包板上进行装配;

- 根据技术指标要求和测试要求,使用仪器仪表对设计电路进行调试;

- 对最终作品进行测试、演示汇报。

3. 实验过程及要求(限 300 字)

如对学生在实验过程中在需求分析、资料查询、自学预习、思考讨论、方法设计、进程规划、软件仿真、平台构建、器件选择、表格设计、现象观察、数据测试、问题分析、总结报告、验收答辩、演讲交流等各方面的要求。

-

学习掌握晶体振荡电路、分频电路、锁相环路及环路滤波电路等相关电路的工作原理;

-

查阅相关资料,结合实验项目的技术指标,设计电路模块及参数计算;

-

按照电路图,在面包板上完成电路的搭建;

-

根据测试要求,对电路进行调试;

-

通过作品测试进行验收,并进行分组演示汇报;

-

整理相关资料,撰写设计报告,总结实验过程的经验和心得体会。

4. 相关知识及背景(限 150 字)

项目涉及所需的知识方法、实践技能、应用背景、工程案例。

这是一个运用数字电路和高频电路等理论知识应用工程实际问题的典型案例,涉及运用振荡器、分频、鉴相、环路滤波及压控振荡等相关知识与技术方法。并涉及仪器设备的测量及电源干扰等工程概念与方法。

5. 实验环境条件

项目实施需要实验资源,包括实验装置功能、实验仪器设备、设计软件工具、主要电子元器件等。

- 实验仪器设备:直流稳压电源、函数信号发生器、数字示波器、数字万用表等;2) 主要元器件及耗材:面包板、晶振、数字锁相环、同步计数器、反相器、电阻、电容和导线等。

6. 教学目标与目的(限 150 字)

如学习、运用知识、技术、方法等;培养、提升技能、能力、素质等。

通过较为完整的工程项目实现过程中引导学生了解现代测量方案、频率合成技术,实现方法的多样性及根据指标要求比较选择技术方案;引导学生根据需要设计电路、选择元器件,通过测试与分析优化设计方案,并对项目作出技术评价。

7. 教学设计与实施进程

课堂知识讲解、方法引导、背景解释;实验中的方法指导,问题设置、思路引导等。教学模式、实验渠道、研讨主题、观察节点、验收重点、质询问题等方面设计等。实验实施进程的各个环节(如任务安排、预习自学、现场教学、分组研讨、现场操作、结果验收、总结演讲、报告批改等)中教学设计的思路、目的,教师、学生各自需要完成的工作任务,需要关注的重点与细节。

本实验过程是一个比较完整的工程实践工程,需要经历学习研究、方案论证、系统设计、实现调试、测试验收、设计总结等过程。在实验教学中,侧重在以下几个方面加强对学生的引导:

-

学习晶体振荡器、分频器、鉴相器、环路滤波器及压控振荡器电路的设计方法,研读芯片的数据手册,根据指标要求调整参数;

-

应用同步计数器实现固定分频和可变分频的分频器;

-

了解频率转换时间的工作原理,根据指标优化设计参数;

-

在电路设计搭建、调试完成后,通过不同的仪器设备进行实际测量,获取更稳定的频率输出;

-

在实验完成后,组织学生以项目演讲、答辩、评讲的形式进行交流,了解不同解决方案及其特点,拓宽知识面。

8. 实验原理及方案

实验的基本原理、设计依据、完成任务的思路方法,可能采用的方法、技术、电路、器件。

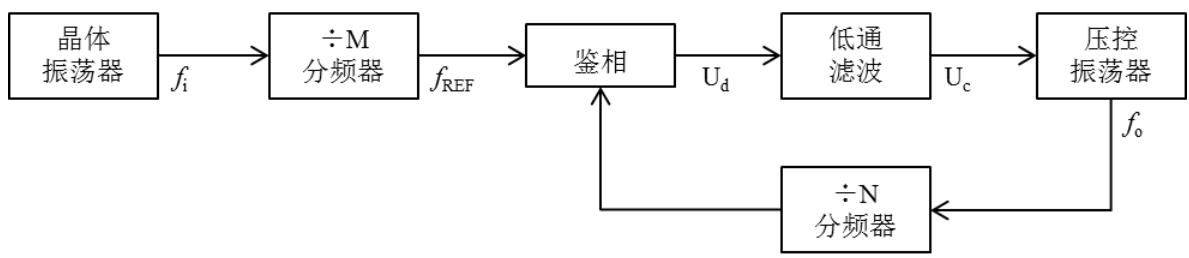

锁相频率合成器的总体框图如下:

图 1 锁相合成器原理框图

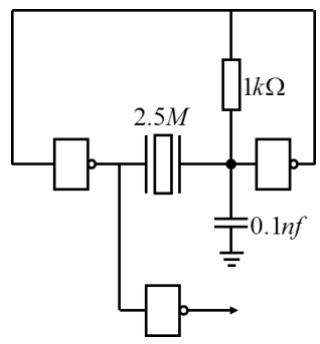

1) 晶体振荡器

石英晶体振荡器是高精度和高稳定度的振荡器,一般将其基准振荡信号作为时间基准来使用。

图 2 晶体振荡电路

图 3 74HC163 真值表

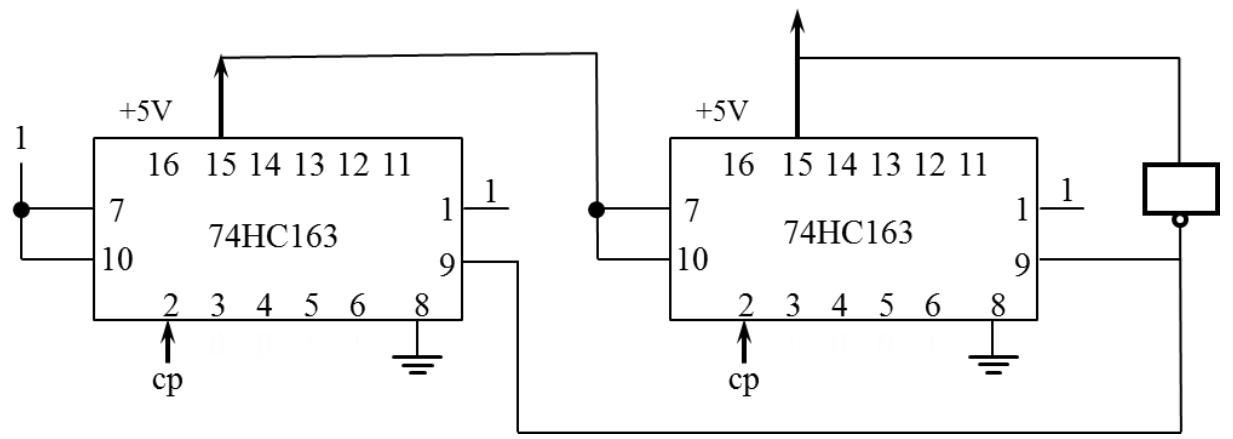

2) 分频器

分频器可以采用计数器 74LS163。

74HC163 是(模 16)四位二进制同步计数器。该计数器能同步并行预置数据,同步清零,具有清零、置数、计数和保持四种功能,并且具有进位信号输出,可串接计数使用。

| OPERATING MODE | INPUTS | OUTPUTS | ||||||

| MR | CP | CEP | CET | PE | Dn | Qn | TC | |

| reset (clear) | 1 | ↑ | × | × | × | × | L | L |

| parallel load | hh | 个 | X | X | 1h | LH | L1 | |

| count | h | 个 | h | h | h | × | count | ① |

| hold(do nothing) | P | 区 | 区 | 区 | hh | X | qnqn | 1L |

当采用两片74LS163 组成N分频器时,每片的预置端(ABCD)要置入数码。设计方案可参考图 4。

图4 可变分频器设计

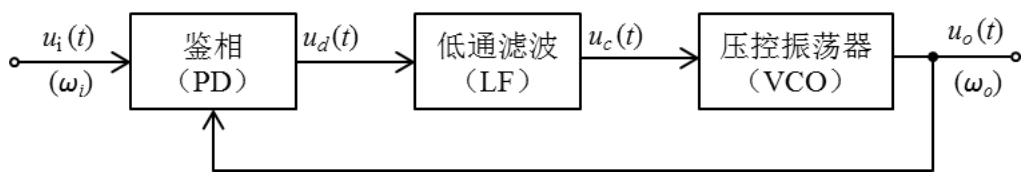

3) 锁相环路和环路滤波器

锁相环路(Phase Lock Loop,PLL)是一种自动相位控制系统,是现代电子系统中应用广泛的一个基本部件。它的基本作用是在环路中产生一个振荡信号,这个信号的频率受控制电压的作用,当环路锁定时,振荡信号的输出频率与输入信号的频率完全相等,两个信号的相位差保持恒定。

图 5 锁相环路组成框图

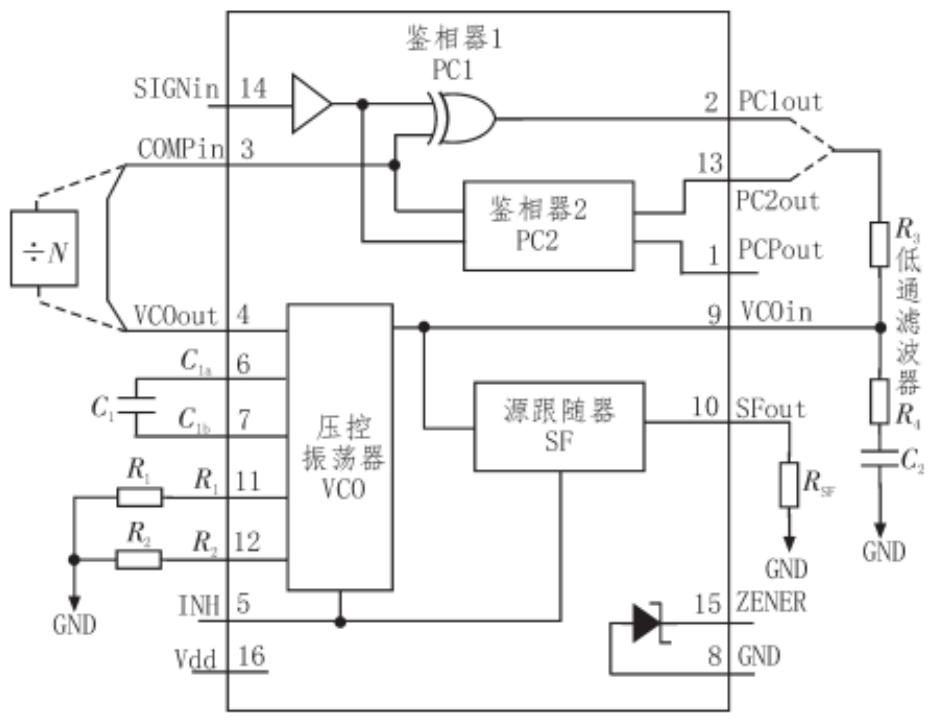

数字锁相环CD4046 由两个鉴相器、一个压控振荡器、一个源极跟随器和一个齐纳二极管组成。

鉴相器有两个共用输入端 PCAIN 和 PCBIN,输入端 PCAIN 既可以与大信号直接匹配,又可间接与小信号相接。自偏置电路可在放大器的线性区调整小信号电压增益。鉴相器Ⅰ为异或门,鉴相器Ⅱ为四组边沿触发器。由于 CD4046的两个鉴相器输入信号均为数字信号,所以称 CD4046 为数字锁相环。

压控振荡器的输出除受输入电压的控制外,还受禁止端 INH的控制,当禁止端 INH为高电平时,禁止 VCO 和源极跟随器工作,当禁止端 INH 为低电平时,允许 VCO 和源极跟随器输出。齐纳二极管用来辅助电源电压的调整。

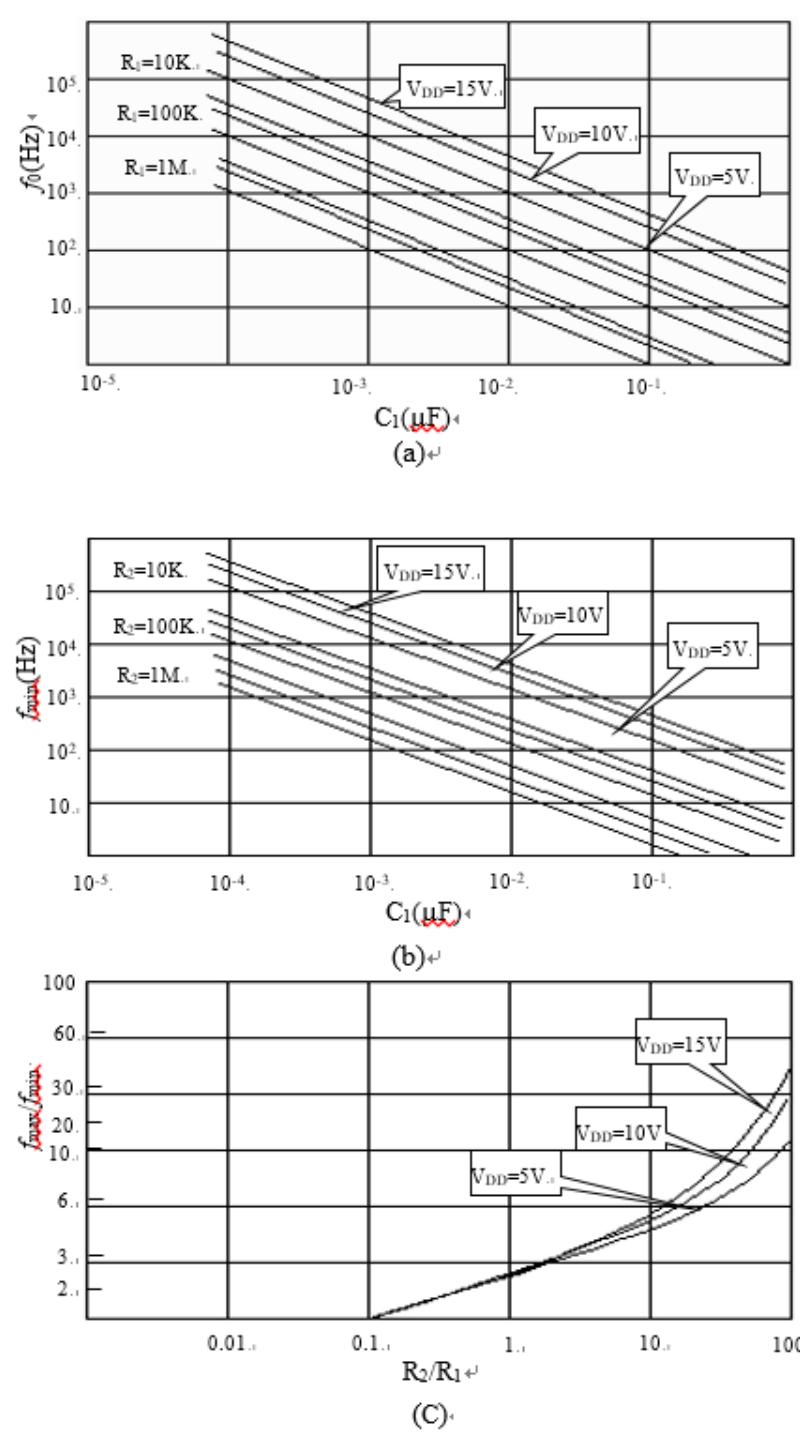

VCO的输出频率最高不超过 1.5MHz,决定振荡频率的不仅和电源电压有关,而且与外接阻容元件有关。振荡频率的定时元件有 R1、R2和电容C1,无信号输入时,VCO将振荡在最低频率上。当使用不同电源时, $\mathrm { C } _ { 1 }$ 与 $f _ { 0 }$ 的关系、 $\mathrm { C } _ { 1 }$ 与 $f _ { \mathrm { m i n } }$ 的关系、 $\mathbf { R } _ { 1 } / \mathbf { R } _ { 2 }$ 和$f _ { \mathrm { m a x } } / f _ { \mathrm { m i n } }$ 的关系如图 6(a)(b)(c)所示。

图 6 VCO 的频率特性参数

(1)VCO 的压控灵敏度 $\mathrm { K } _ { 0 }$ 与线性度 $\boldsymbol { \eta }$

VCO的压控灵敏度是单位电压控制下,VCO输出角频率的变化量,记作 $\mathrm { K _ { 0 } ( r a d / s . v ) }$ ,它的平均压控灵敏度定义为

$$ K _ { \mathrm { 0 } } = ( \omega _ { \mathrm { m a x } } - \omega _ { \mathrm { m i n } } ) / ( U _ { \mathrm { { c m a x } } } - U _ { \mathrm { { c m i n } } } ) $$

理想的压控灵敏度 $\mathrm { K } _ { 0 }$ 应是不变的,但实际中的 $\mathrm { K } _ { 0 }$ 是变化的,这样压控特性是非线性的,通常用线性度 $\boldsymbol { \eta }$ 参量来描述线性程度, $\boldsymbol { \eta }$ 越接近 1 越好, $\boldsymbol { \eta }$ 的定义为

$$ \eta = K _ { \mathrm { o m ~ a ~ x ~ } } / K _ { \mathfrak { 0 } \mathrm { m } \mathrm { ~ i ~ r ~ } } $$

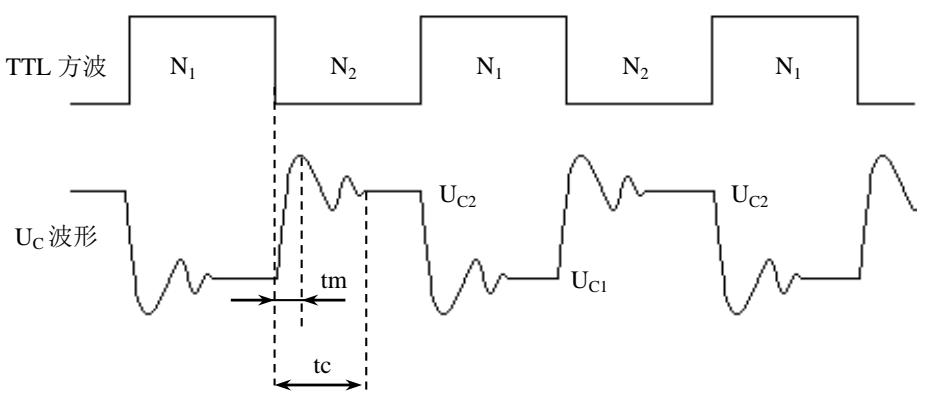

$( 2 ) t _ { \mathrm { c } }$ 的测量与计算

$t _ { \mathrm { c } }$ 为频率转换时间,即频合器输出从某一频率跳变到另一频率的时间。

环路锁定后,相位差 $\theta _ { \mathrm { e } }$ 为一常量,鉴相器输出电压 $\mathrm { U _ { d } }$ 是一直流电压,环路滤波器输出 $\mathrm { U _ { c } }$ 也为一直流电压,用示波器可观测 $\mathrm { U _ { c } }$ 的状态变化,判定环路是否入锁。改变分频比 $_ \mathrm { N }$ 的数值,环路即刻失锁,若频差在捕捉带内,经短时间频率的牵引,又进入锁定状态。频合器从失锁到入锁的时间,称为频率转换时间 $\mathbf { t } _ { \mathrm { c } }$ 。实际测量时,可用一 TTL信号源接到 N 分频器预置码的某一位上。利用信号源的高低电平,取代对应的两个可预置码,再用示波器同时观测信号源波形和 $\mathrm { U _ { c } }$ 点的波形,从示波器上读出峰值时间 $\mathbf { t } _ { \mathrm { m } }$ 和频率转换时间 $\mathbf { t } _ { \mathrm { c } }$ 的特征参数。对应波形如图 7所示。

图7 N改变时的波形

图 8 CD4046 的内部结构图及外部连接简图

9. 实验报告要求

需要学生在实验报告中反映的工作(如:实验需求分析、实现方案论证、理论推导计算、设计仿真分析、电路参数选择、实验过程设计、数据测量记录、数据处理分析、实验结果总结等等),如:

实验报告需要反映以下工作:

- 实验需求分析:明确实验目的、实验内容、实验任务以及最终需要达到的实验功能与技术指标等;

- 实验原理分析:结合实验需求分析,阐述晶体振荡电路、分频电路、锁相环路及环路滤波电路等工作原理;

- 设计方案介绍:描述设计方案论证,给出设计电路思路和电路设计功能框图;

- 系统调试过程:电路调试中所遇到的问题,对问题的分析、解决、处理的结果;

- 实验结果分析:观察并记录电路的测试结果,结合原理进行分析;

- 实验报告总结:结合实验过程中遇到的问题和解决方法,对所设计的系统进行综合评价,并提出实验课改进的地方或可扩展功能的意见。

10.考核要求与方法(限 300 字)

考核的节点、时间、标准及考核方法。

-

设计方案:电路设计方案合理,并绘制总体电路原理图,此环节占总分的 $1 0 %$ ;

-

实物验收:面包板的布局和布线工艺,功能与性能指标的完成度,及完成时间,此环节占总分的 $5 0 %$ ;

-

现场提问:对照学生的实验结果,对实验现象、实验原理等环节进行提问,此环节占总分的 $1 0 %$ ;

-

汇报答辩:讲述设计思路及实验过程,此环节占总分的 $1 0 %$ ;

-

实验报告:实验报告要求内容完整,格式规范,能根据实验现象独立思考做出总结,此环节占总分的 $2 0 %$ 。

11.项目特色或创新(可空缺,限 150 字)

项目的特色在于:项目背景的工程性,知识应用的综合性,实现方法的多样性。

项目的特色在于:

- 锁相频率合成技术具有广泛的应用性,实验项目具备工程性;

- 实验过程涵盖了电路设计的完整流程,培养学生系统设计的能力,及认真钻研的精神;

- 实验设计方案可选性及功能可拓展性,分层次灵活教学,有助于充分调动学生的积极性。