基于FPGA和Simulink的虚拟示波器

实验题目:基于FPGA和Simulink的虚拟示波器

课程简要信息

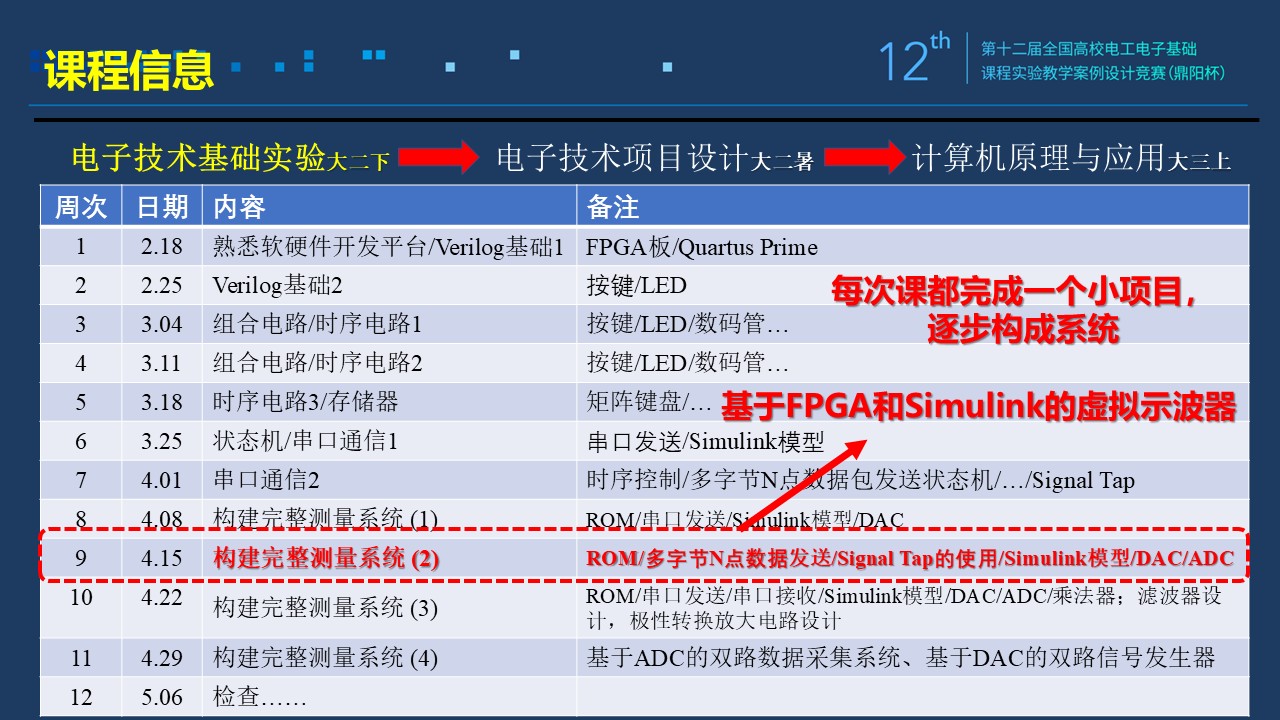

课程名称:电子技术基础实验

课程学时:课内32学时、课外32学时

适用专业:电气工程

学生年级:大二下学期

教学目标与目的

- 深入理解时序图、时序分析等基本概念,加深对时序电路核心知识点的掌握;

2)掌握时序电路的设计方法,具备根据时序图设计数字电路模块的能力;

3)掌握Verilog HDL结构化建模方法以及复杂时序电路的设计方法;

4)了解使用MATLAB/Simulink编写串口通信模型的方法;

5)通过基于FPGA和Simulink的虚拟示波器的设计与调试,提高解决实际问题的能力。

实验内容与任务

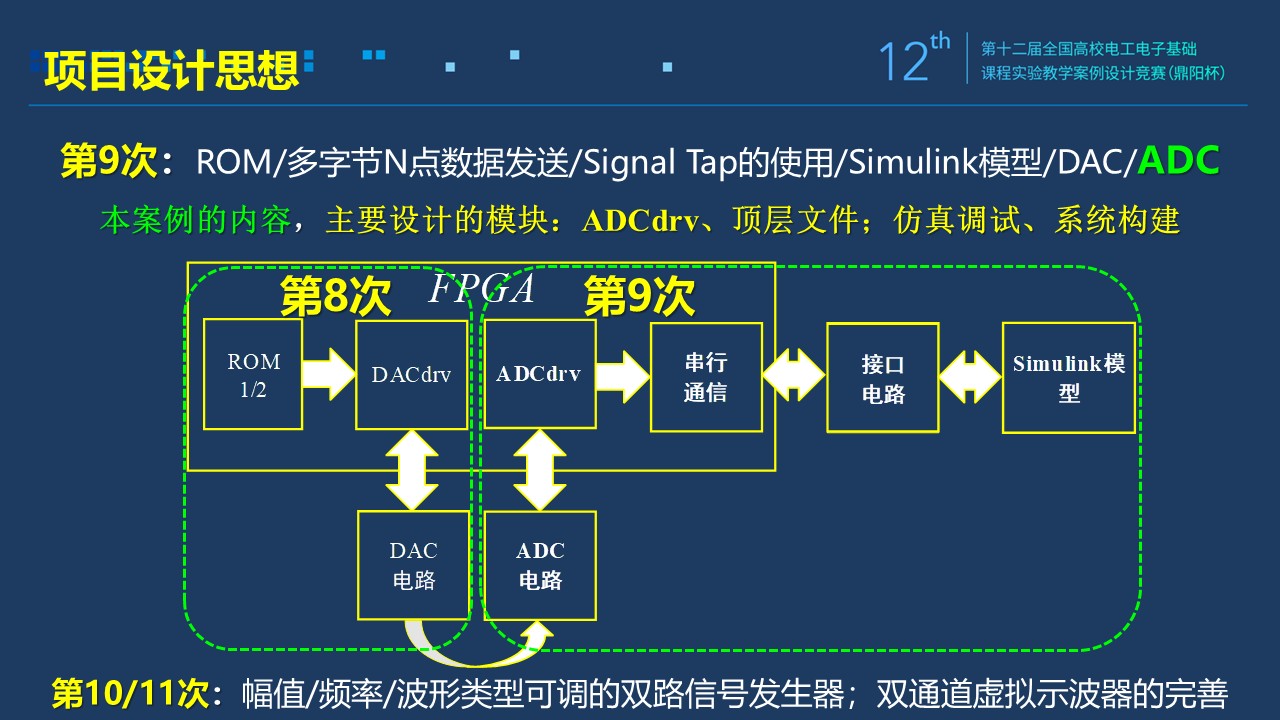

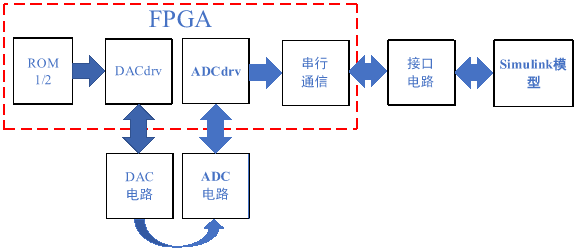

《电子技术基础实验》课程主要的任务是基于FPGA实现一种简易信号发生器和示波器。FPGA通过USB线(虚拟串口)与上位机通信,接收命令并控制DAC的波形输出;FPGA从ADC读入波形采样数据,将数据打包后发送到上位机;在上位机上使用MATLAB/Simulink编写模型,实现与FPGA的双向通信:(1)数据包解码和波形显示;(2)命令发送(波形发生器的输出波形类型、幅值和频率等控制命令)。系统框图如图1所示。

图1 系统框图

本案例是课程中的一个环节,前面已经完成针对DAC波形产生(双通道)、串行通信接口和基本simulink模型的设计。本案例主要是在前面课程已完成设计的基础上,加入ADC模块,通过编写ADC接口电路逻辑,实现ADC对DAC输出波形的采样,并通过simulink模型来查看波形,DIY一种简易示波器。

本案例的实验内容与任务如下:

1)在已完成设计的基础上,用FPGA控制DAC产生两路信号,并用示波器进行测试,确认波形输出正常。

2)设计ADC模块的接口逻辑电路,实现对DAC输出波形信号的采集,通过Signal Tap逻辑分析仪查看控制信号时序图和采样值波形;

3)用示波器测量ADC控制信号的时序图;

4)用simulink接收ADC采样数据,并显示波形。

实验过程及要求

3.1 预习任务: {#预习任务}

1)基于已完成的设计,用示波器查看DAC输出的两路波形信号,确保波形输出正常。

2)仔细阅读ADC芯片(CS5343)文档,了解其I^2^S接口规范以及SDOUT、SCLK、LRCK和MCLK的时序要求。

3)给出ADC接口电路的初步实现方案(包括工作模式及各控制信号之间的关系和参数选择),画出实现框图。

3.2 课堂任务: {#课堂任务}

1)用Verilog HDL编写ADC芯片的接口电路,通过SignalTap查看SDOUT、SCLK、LRCK和MCLK的时序图,与芯片文档中的时序图进行对比分析;

2)用示波器实际测量SDOUT、SCLK、LRCK和MCLK的时序图,检查各信号是否满足时序约束条件。

3)通过SignalTap监测ADC采样值数据,查看波形是否与DAC输出波形一致。如果不一致,返回上述步骤1)和2)。

4)修改simulink模型,实现对一路ADC波形的显示(两路同时显示的任务,留作课后作业)。

3.3 课后任务: {#课后任务}

1)用FPGA控制DAC产生两路正弦波形,一路信号是频率为50Hz的基波,另一路为基波50Hz、带有3/5/7次谐波分量的波形(3次谐波占20%,5次占10%,7次占5%)。

2)用双通道ADC同时采样DAC输出的两路波形信号,并通过simulink模型显示。

3)回答讲义中的思考题并提交实验报告。

相关知识及背景

通过阅读ADC芯片文档,读懂时序图,总结关键的时序约束参数;用HDL实现接口电路模块设计的方法。

了解Quartus Prime中SignalTap逻辑分析仪的工作原理和使用步骤,了解其触发、采样深度等参数,熟悉各类中间变量(信号)的监测方法。

用示波器测量FPGA输出的控制信号,通过测量时钟与数据的波形图,结合数字电路中时序信号的建立时间和保持时间等参数,能通过时序波形图判断其是否满足时序约束要求。

教学设计与引导

6.1 本次课难点 {#本次课难点}

本次课实现的难点是ADC芯片接口电路的时序逻辑设计,这是一个双通道24位ADC,通过4个数字IO(SDOUT、SCLK、LRCK和MCLK)与FPGA相连,并且这4个信号相互间有严格的时序要求。

6.2 讲解开始时,深化对核心知识点的理解 {#讲解开始时深化对核心知识点的理解}

虽然有预习要求,但在课堂知识讲解中,还必须对ADC芯片的工作模式(主模式/从模式;单速模式/倍速模式)和时序逻辑进行详细的阐述和分解。课堂讲解之初,应通过提问的方式与学生进行互动。譬如提问:ADC几种工作模式之间的区别何在?工作模式的选择是不是任意的?时序图中,为什么要求SCLK的上升沿要与SDATA的中间位置对齐?通过一系列的互动,可以进一步启发学生的思考,使其在预习中可能没有深入理解的地方能够得到进一步深化,同时还通过这些非常具体的问题,教会学生代码的编写应与实际电路严格保持一致,以及加强对理论课中针对时序电路的建立时间、保持时间等时序约束条件的理论知识的理解。因为这些问题对随后的电路设计和硬件调试过程也是非常重要的。只有透彻地理解了这些问题,才能确定各个信号之间的约束关系,譬如LRCK不但用于通道控制,而且可以决定ADC的采样频率,MCLK与LRCK以及SCLK与LRCK之间都有固定比例关系的要求等等。

6.3 讲解过程中,指导关键点设计 {#讲解过程中指导关键点设计}

基于FPGA使用Verilog HDL来进行复杂数字电路设计,关键点是掌握结构化的建模方法以及调试方法。在讲解中应重点强调一个电路对应一个module,一个module对应一个文件,以及在顶层文件中实例化模块、完成模块间连线,尽量不在顶层文件中写逻辑等结构化建模的基本要求。此外,还应强调顶层文件设计中的常见错误,譬如忘记声明中间信号等低级但又很难发现的错误(特别是在复杂的设计中)。此外,在实验指导中,应逐步引导学生使用逻辑分析仪进行调试,因为很多学生急于任务的完成,通常是进行盲调(直接下载看结果),这种只关注结果的方式是不利于知识的系统把握的,很多时候只能是知其然而不知其所以然。在调试中,还要指导学生如何使用示波器抓时序图,结合SCLK和SDATA来分析数字信号的采样窗口,强化时序电路的时序约束概念。

6.4 辅导过程中,组织专题讨论 {#辅导过程中组织专题讨论}

在课程进展过程中,应随时针对学生出现的问题,进行专题讨论。譬如,有学生在使用逻辑分析仪时,触发源选择的是系统时钟,结果只能捕捉到有限的波形数据,看不到想要观察的时序图。此时,就可以通过组织讨论的方式,跟学生讲解逻辑分析仪的基本原理、存储深度及其与触发条件的关系,引导学生制定解决这个问题的方案。

6.5 课程进展过程中,明确重点和要点,进行正向引导 {#课程进展过程中明确重点和要点进行正向引导}

此外,在课堂上还要明确任务的验收重点和考核要点,重对核心概念的理解、重实现细节、重解决问题的过程而非最终结果。以这种方式来正向引导,就可以避免只看结果而导致的抄袭等现象。

实验原理及方案

7.1 硬件接口电路原理 {#硬件接口电路原理}

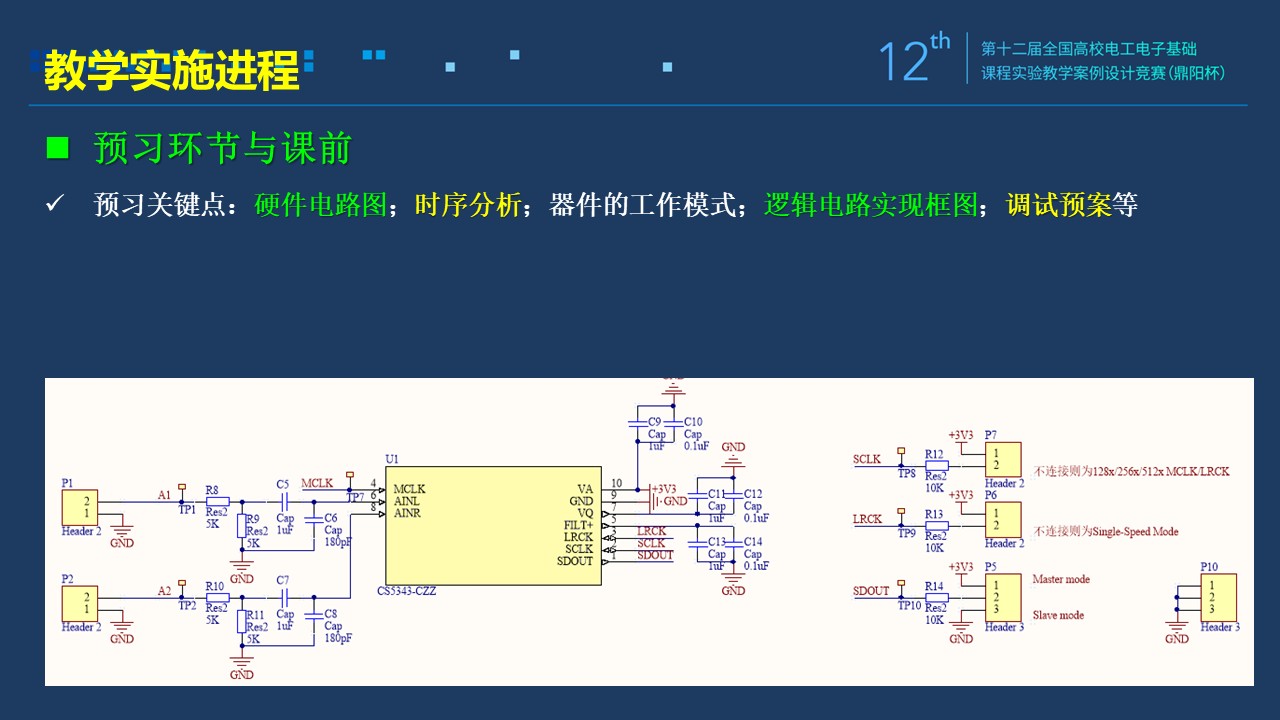

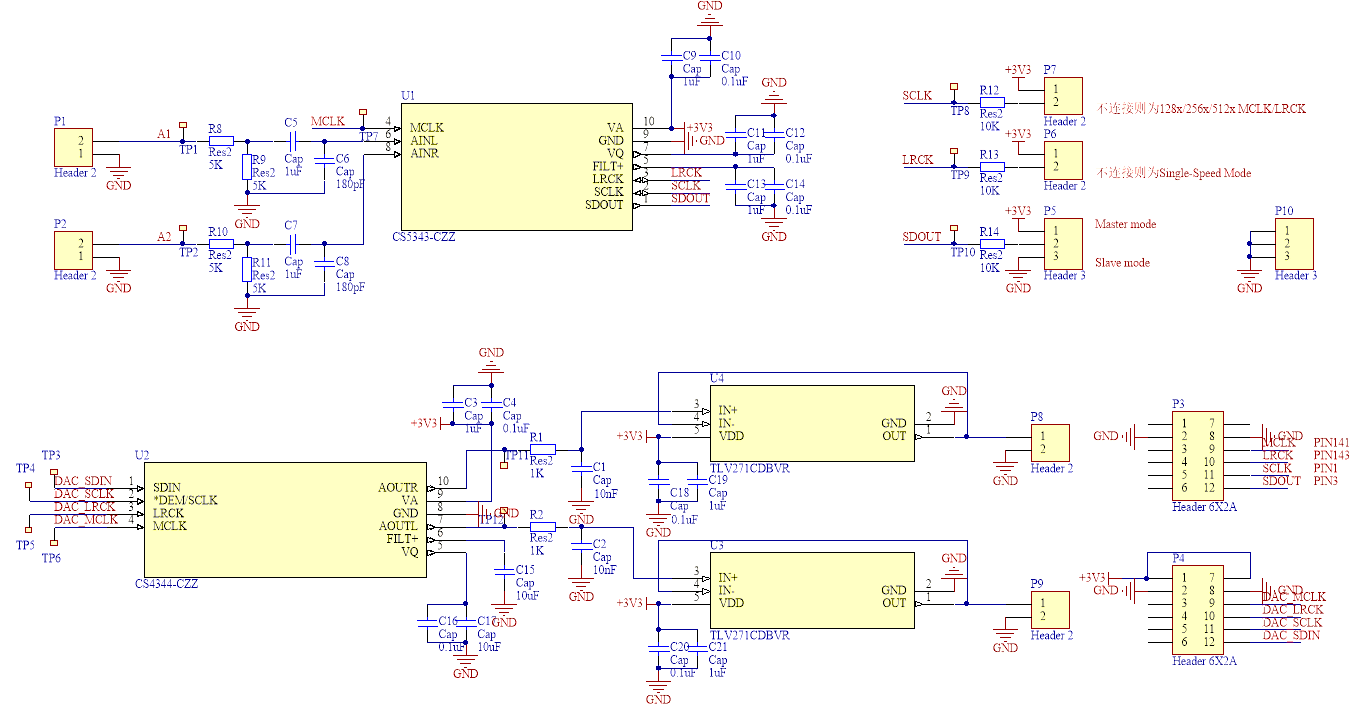

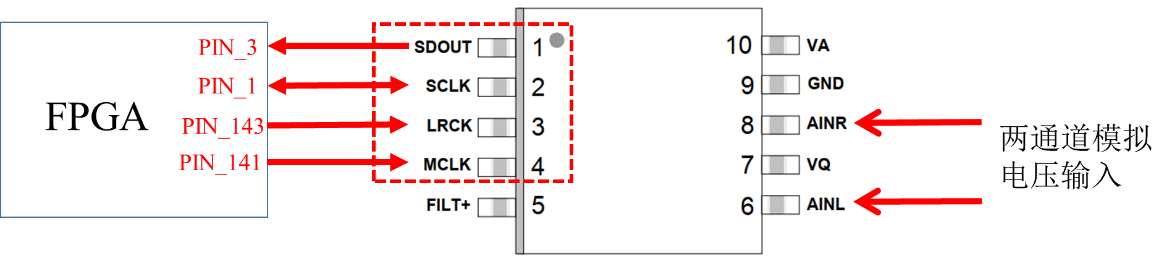

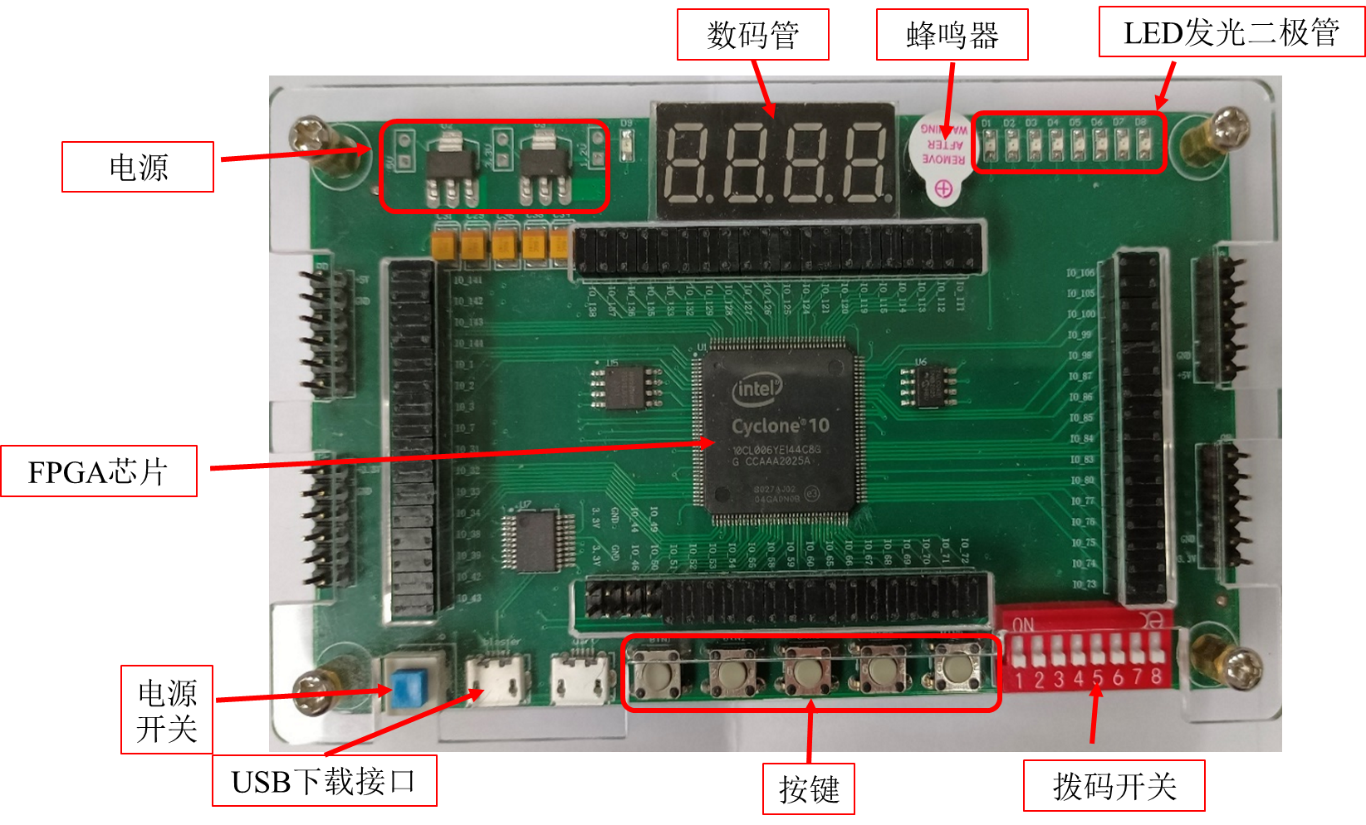

ADC接口电路有一定的输入范围要求(偏置电压3.3V,输入电压峰峰值4V),转换后的采样值为二进制补码格式。图2所示为ADC接口电路图。

图2 ADC接口电路原理

ADC芯片的PIN1~4分别与FPGA的PIN3/2/143//141相连。连接示意图如图3所示。

图3 ADC芯片与FPGA的连接示意图

7.2 时序约束和时序图分析 {#时序约束和时序图分析}

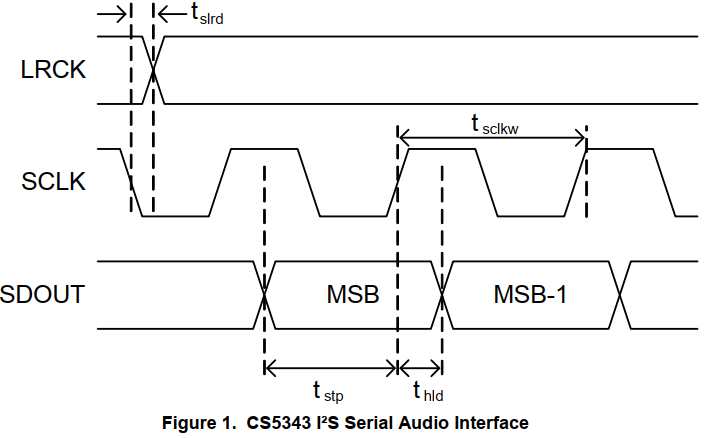

ADC芯片的LRCK、SCLK与SDOUT之间有严格的时序约束要求,譬如建立时间tstp(最小值10ns)和thld(最小值40ns),见图4。

图4 时序约束

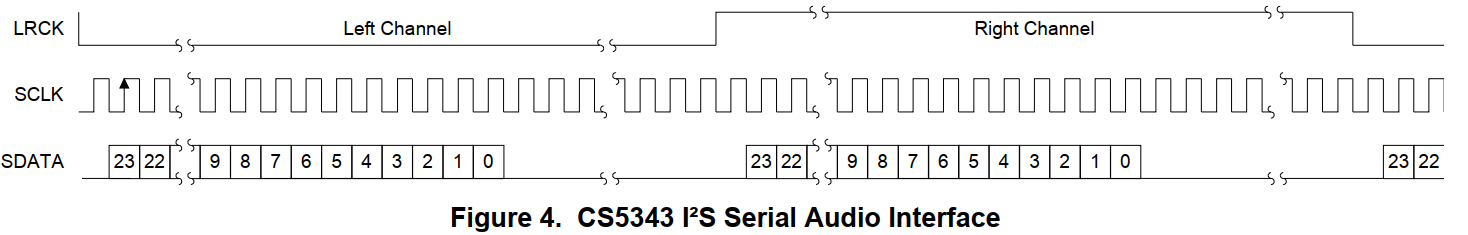

ADC芯片的MCLK是ADC的工作时钟,直接给FPGA的系统时钟(25MHz)即可。LRCK用于通道控制(低电平时是左通道,高电平时是右通道),当选定通道后,在第2个SCLK的上升沿,会通过SDOUT连续、依次送出当前采样值对应的24位数据。时序图如图5所示。

图5 ADC数据输出时序图

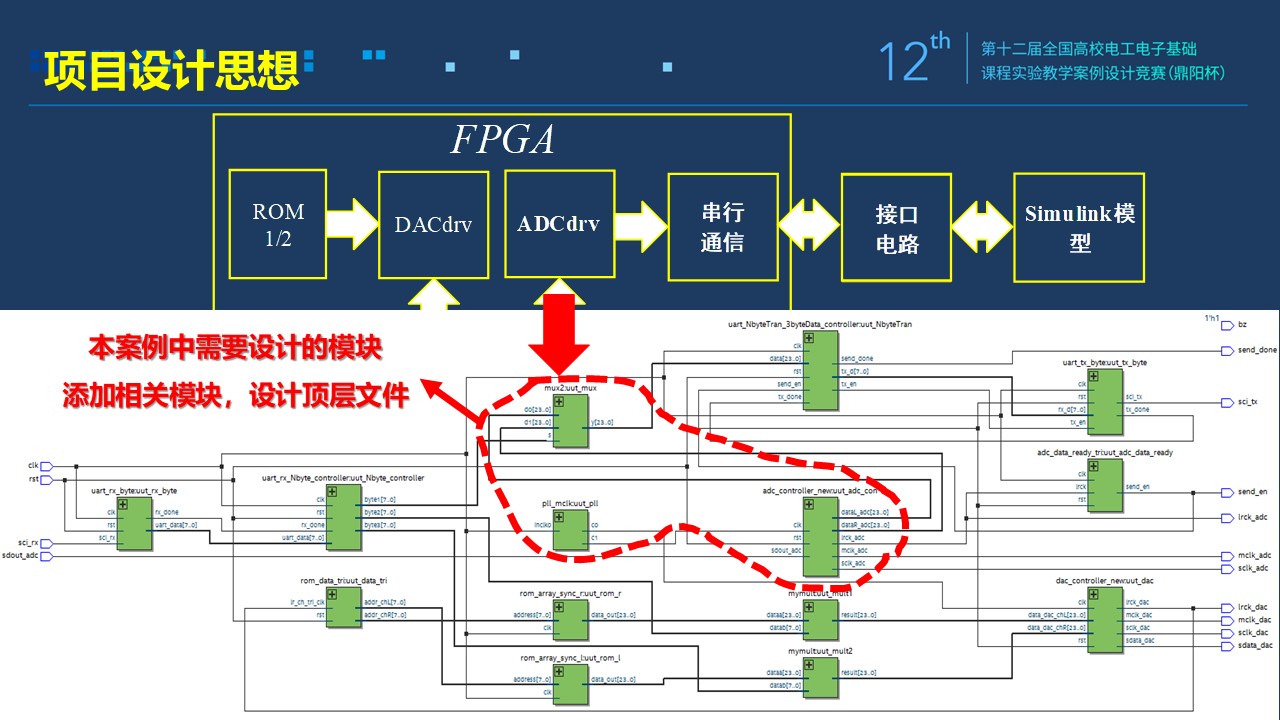

7.3设计模块的关键参数及与系统的连接关系 {#设计模块的关键参数及与系统的连接关系}

在单速模式下,ADC芯片要求其各控制信号的频率呈一定比例关系:

fMCLK/fLRCK=256,fSCLK/fLRCK=64

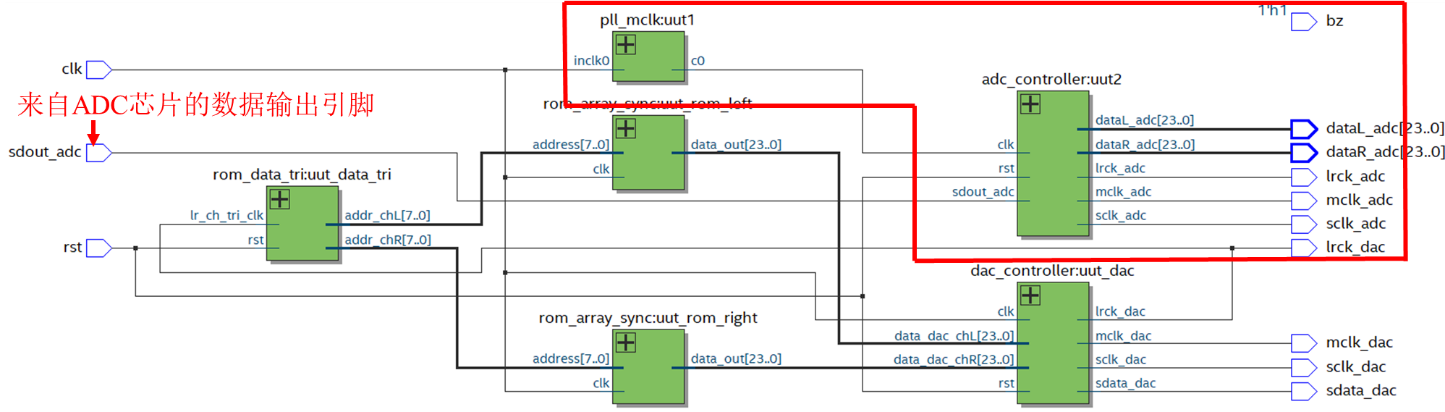

假如设置ADC采样频率为5kHz,则fLRCK=5kHz,fMCLK=1.28MHz,fSCLK=320kHz。基于图5所示时序图,用Verilog

HDL设计ADC接口逻辑电路adc_controller。在顶层文件中进行实例化,完成电路连接。然后,在Quartus

Prime中进行编译,用RTL

Viewer可以得到完整的电路连接图,其中ADC接口电路如图6中方框中所示。

图6 完整的电路图

图6中,ADC接口逻辑电路(adc_controller)的时钟来自pll_mclk模块,该模块可通过锁相环实现,将25MHz时钟分频为1.28MHz,作为MCLK。

7.4 逻辑分析仪的使用 {#逻辑分析仪的使用}

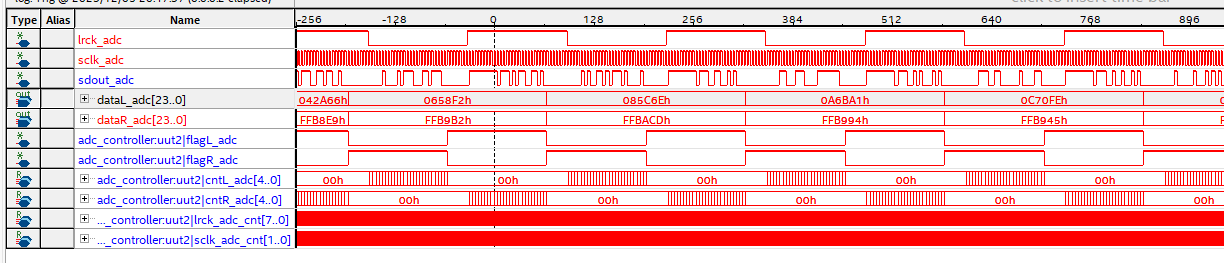

在SignalTap中,以MCLK为触发信号,可以到图7所示时序图。

图7 利用SignalTap查看波形

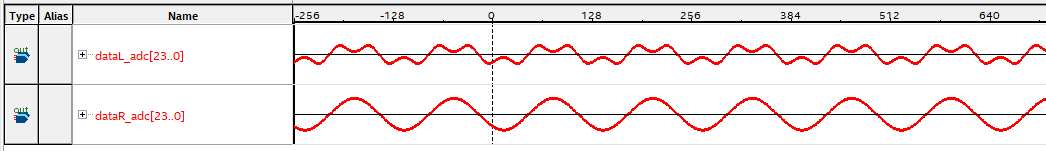

在ADC/DAC接口板上,将DAC的输出连接到ADC的输入上。在SignalTap中,以lrck_adc为触发信号,可以得到采集到的波形信号,如图8所示。左通道(dataL_adc)为带3/5/7次谐波的信号。

图8 ADC采样到的波形信号

7.5 用示波器捕捉时序图 {#用示波器捕捉时序图}

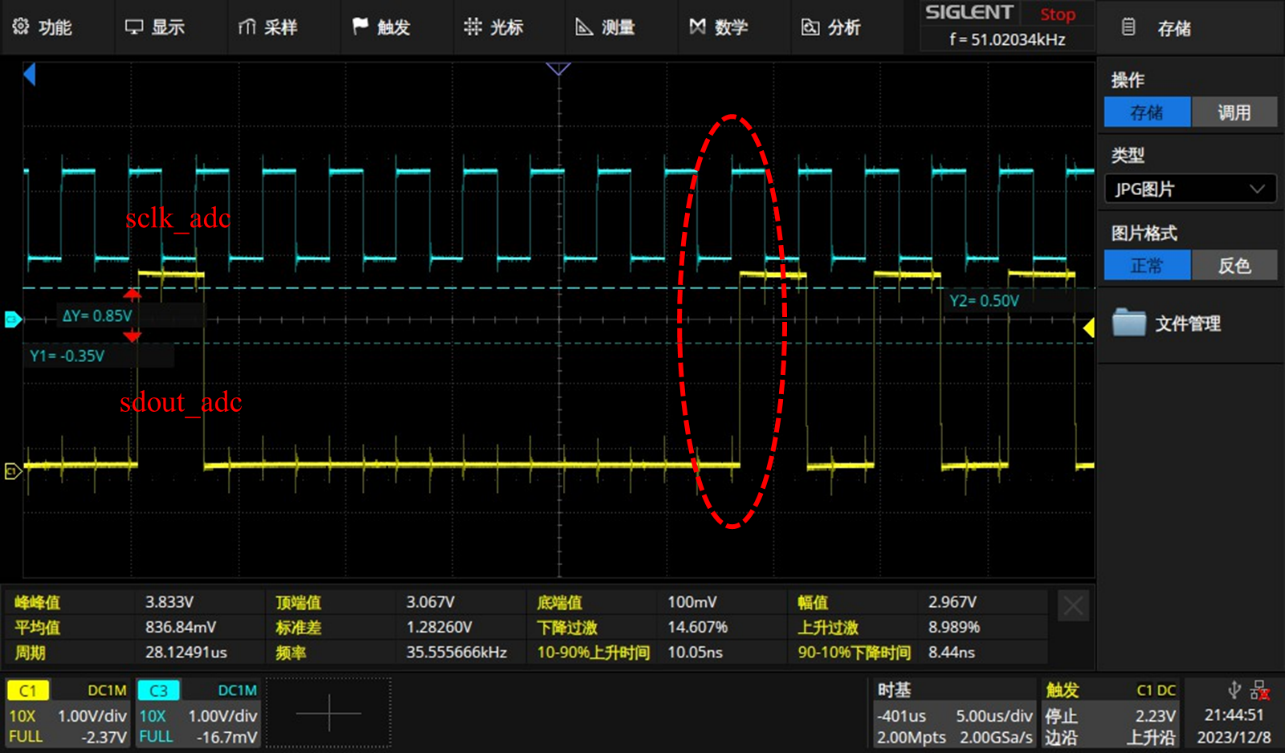

用示波器从ADC/DAC接口板上测量sclk_adc和sdout_adc的波形,时序图如图9所示。

图9 用示波器测量sclk_adc和sdout_adc

7.6 添加串行通信接口,实现与上位机通信 {#添加串行通信接口实现与上位机通信}

上面只是实现了通过SignalTap逻辑分析仪来查看ADC采样结果,如果要将其通过串行通信接口送至PC机,需要在FPGA中增加串行通信的模块。串行通信相关的模块可以直接使用上次实验课完成的电路。在Quartus Prime中添加后完成编译,可以在RTL Viewer中查看完整的电路框图。如图10所示。

串行通信接口

ADC

DAC

图10 带串行通信接口的完整电路

图10中,rom_data_tri模块用于修改dac rom的地址,同时用作lrck_dac做触发源;pll_mclk实现用锁相环产生两路时钟,分别控制adc和dac;rom_array_sync_l和rom_array_sync_r,存储DAC的波形数据;uart_NbyteTran_3byteData_controller用于实现将ADC采样值数据组帧;adc_controller_new是ADC接口电路模块;dac_controller_new是DAC接口电路模块;uart_tx_byte是串口发送模块;adc_data_ready_tri模块用于给出串口发送的send_en,取lrck_adc的边沿。所有这些电路均可用之前课上实现的模块。

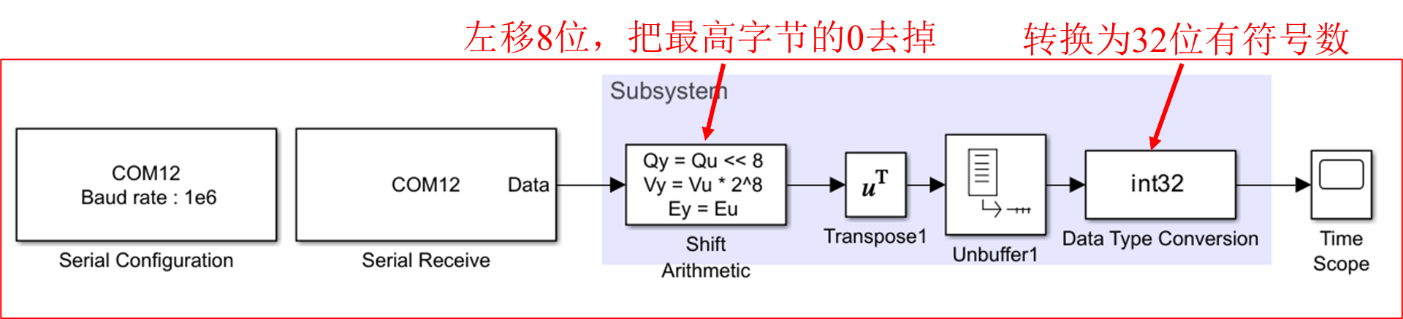

7.7 上位机simulink模型修改及波形显示 {#上位机simulink模型修改及波形显示}

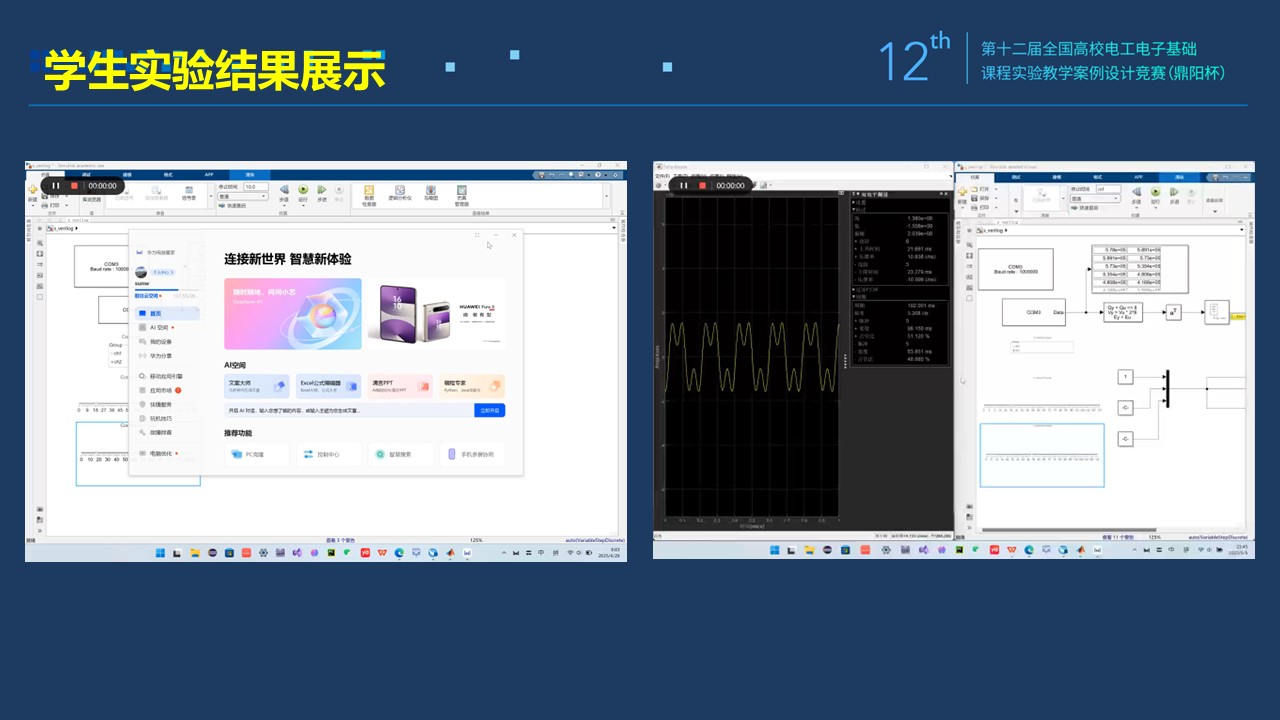

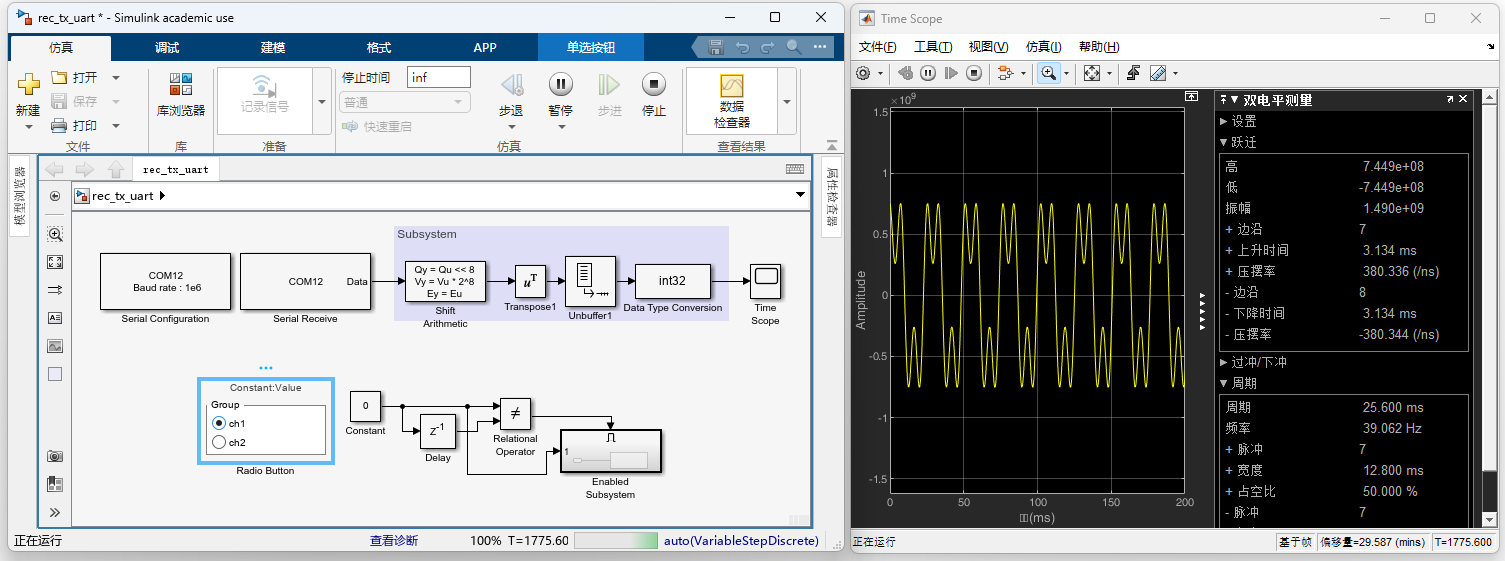

修改并完善simulink模型,实现对ADC采样数据的接收和显示。这个模型只能显示一个通道的数据,可以通过将DAC的两个输出分别连接到ADC的相应通道上,得到图11所示的波形图。

图11 通过simulink看波形

要实现双通道的同时显示,不但要修改simulink模型,而且要修改FPGA中串口发送部分的相关代码。这部分内容将作为作业,在下次课之前完成。

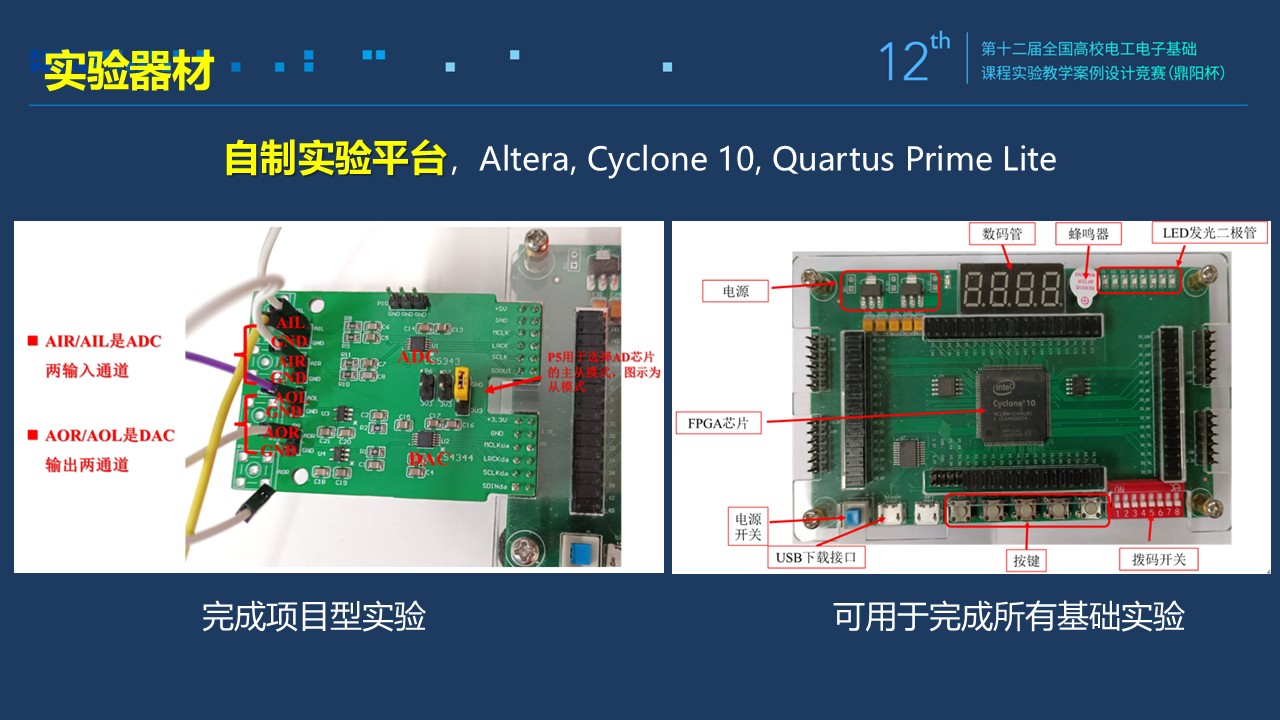

7.8 用到的实验器材 {#用到的实验器材}

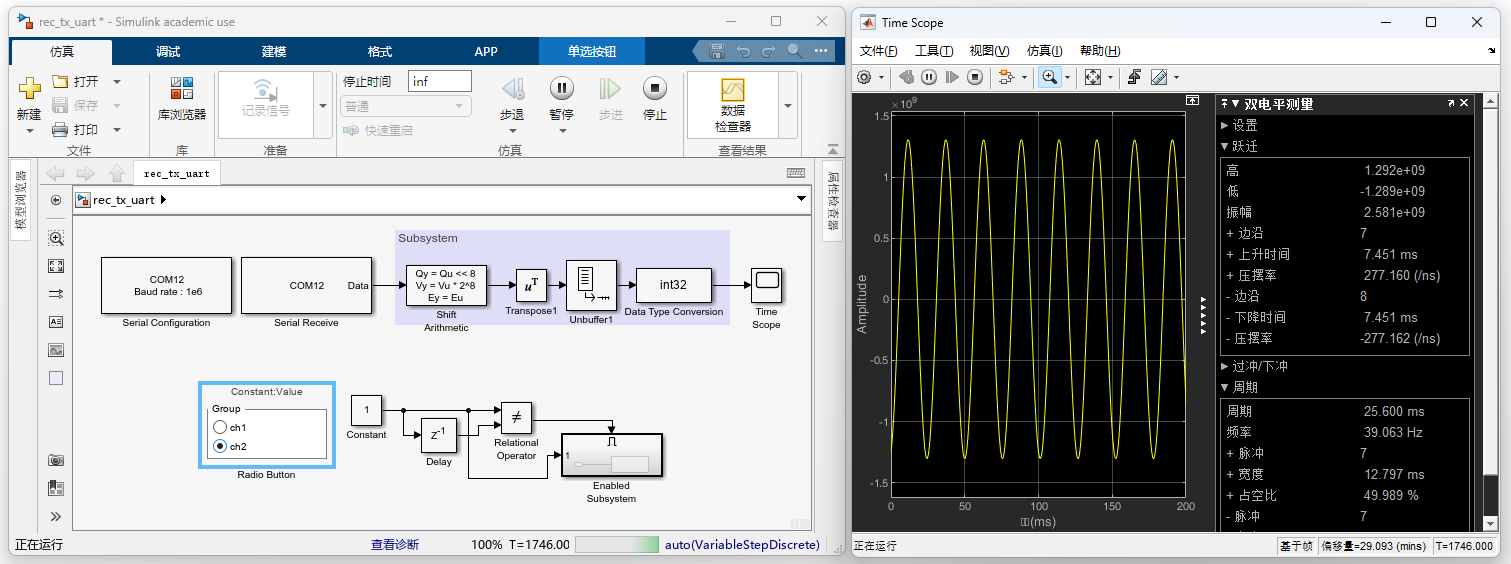

FPGA开发版 1台

ADC/DAC接口板 1块

数字示波器 1台

计算机 1台

FPGA开发与ADC/DAC接口板如图12所示:

图12 FPGA开发板与ADC/DAC接口板

7.9 注意事项 {#注意事项}

1)要求先用示波器确认DAC的输出波形;然后再进行ADC采样过程的调试。

2)注意:DAC有两个输出通道AOL和AOR;用示波器测量时,应采用针孔线,不要把示波器表笔直接勾在电路板上,以免造成短路。

3)本实验时序逻辑较为复杂,并且需要时序配合,要充分发挥SignalTap的作用。

教学实施进程

8.1预习环节 {#预习环节}

1)预习报告应要求在实验课前完成;

2)预习报告中应标明ADC控制引脚的时序关系和相关的比例参数设置;

3)预习报告中,还应有待实现ADC接口逻辑的实现框图(这一点非常重要!);

4)预习报告中,应写出调试方法和可能遇到的问题及其解决方案。

[开始上课10分钟前]{.underline},组织助教检查预习完成情况,对预习的既定环节没有完成者,要根据评分细则扣分。

预习需要严格要求,否则有些学生会认为本课程管理不严,易造成懒散的“课风”,导致后期的上课效果会大打折扣。

8.2课程教学环节 {#课程教学环节}

1)与学生课前交流

教师应**[提前30分钟]{.underline}**到实验室,在课堂教学前,与提前到的学生进行交流,对上次作业的完成情况以及本次实验的预习情况有个大体的了解。

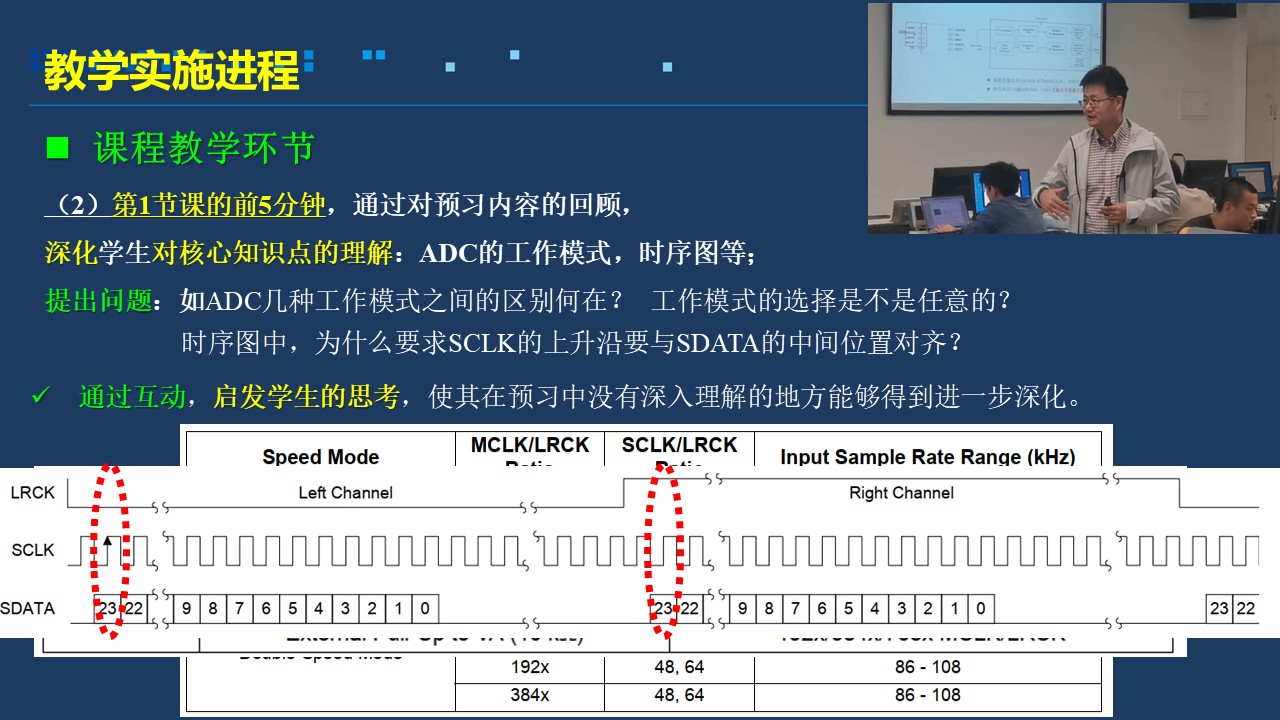

2)[第1节课的前5分钟]{.underline},通过对预习内容的回顾,深化学生对核心知识点的理解

结合预习内容,深化学生对核心知识点,如ADC的工作模式(主模式/从模式;单速模式/倍速模式)和时序逻辑的理解。应通过提问的方式与学生进行互动,譬如:

ADC几种工作模式之间的区别何在?工作模式的选择是不是任意的?时序图中,为什么要求SCLK的上升沿要与SDATA的中间位置对齐?

通过几次互动,进一步启发学生的思考,使其在预习中没有深入理解的地方能够得到进一步深化。

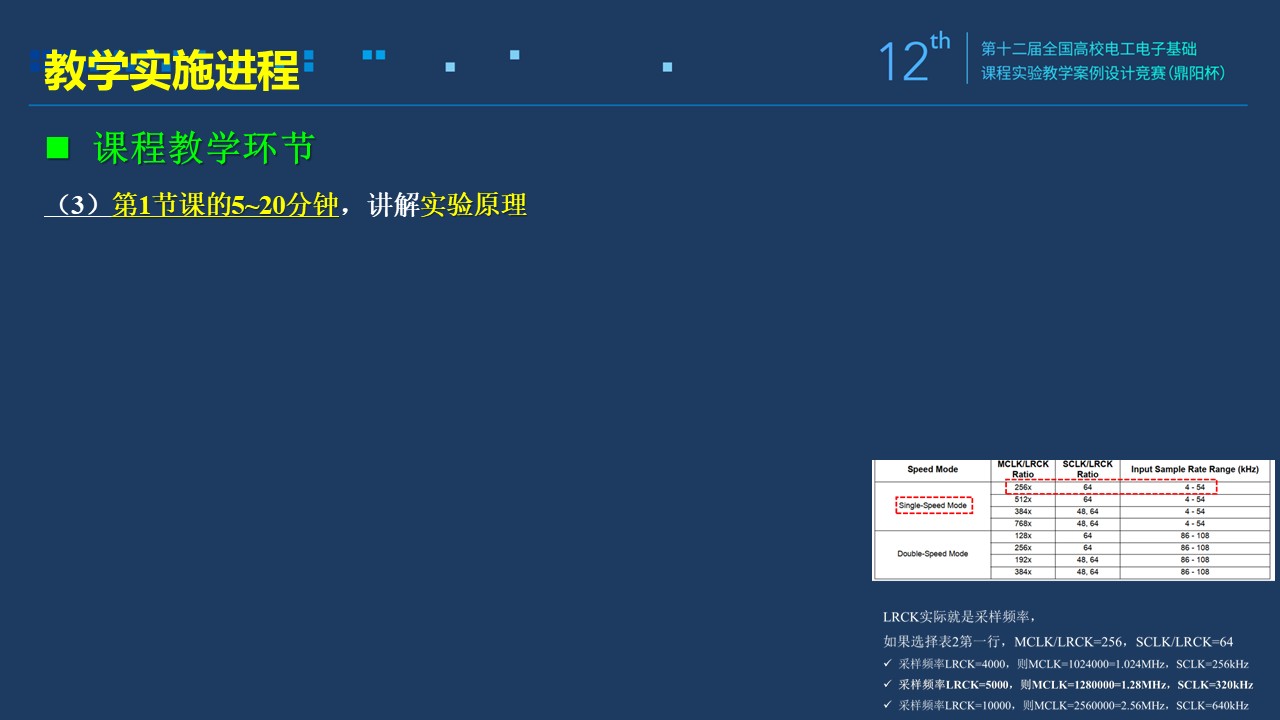

3)[第1节课的5~20分钟]{.underline},讲解实验原理

课堂讲解时,应对实验任务进行分解,抓关键点和难点。本次课的难点是时序图和时序约束。此外,由于涉及到对真实器件的控制,必须严格满足时序约束,才能得到正确的结果,所以要结合时序图详解MCLK、LRCK、SCLK与SDOUT的时序关系。

原理讲解部分,包括硬件接口电路,时序约束和时序图分析,设计模块的关键参数及与系统的连接关系。同时,通过这些非常具体的问题,教会学生代码的编写应与实际电路严格保持一致,以及加强对理论课中针对时序电路的建立时间、保持时间等时序约束条件的理论知识的理解。这些问题对随后的电路设计和硬件调试过程也是非常重要的。只有透彻地理解了这些问题,才能确定各个信号之间的约束关系。要明确一些技术细节,如LRCK不但用于通道控制,而且可以决定ADC的采样频率,MCLK与LRCK以及SCLK与LRCK之间都有固定比例关系的要求等等。通过对这些具体参数的解读,教会学生高效阅读芯片文档的方法。此外,还应结合always语句的特点,通过举例的方式,介绍LRCK和SCLK的产生方法。

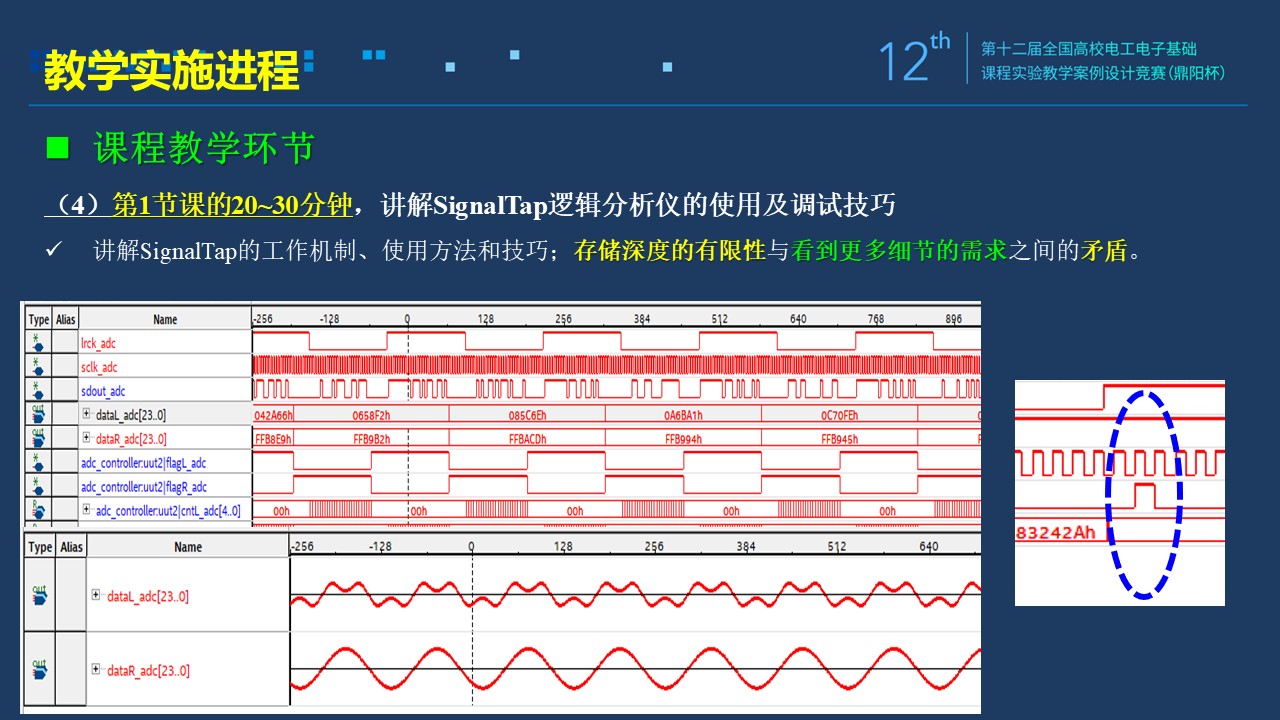

4)[第1节课的20~30分钟]{.underline},讲解SignalTap逻辑分析仪的使用及调试技巧

结合实例,讲解SignalTap的工作机制和使用方法。Quartus Prime中的SignalTap虽然简单易用,但使用中,还是有一些技巧的。因为它要占用FPGA的逻辑资源,存储深度是有限的。如何在有限的逻辑资源下,看到更多的细节以有助于调试过程,是需要综合考虑多种因素的。

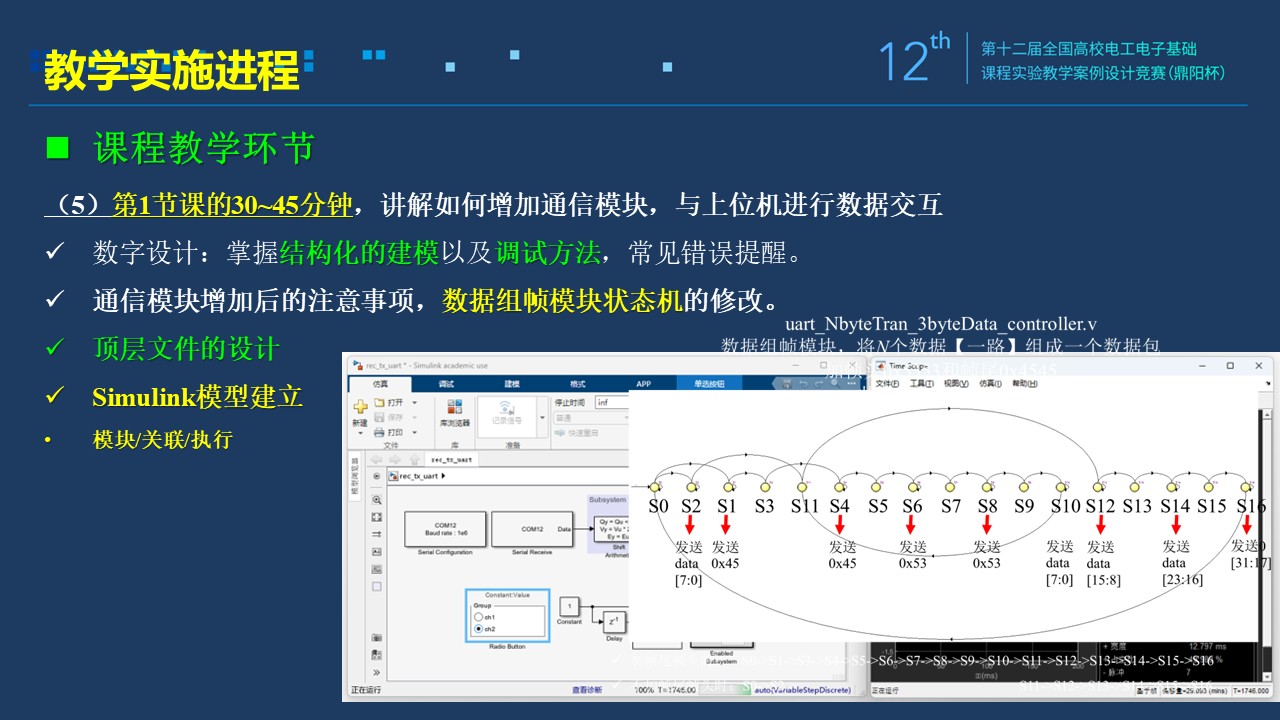

5)[第1节课的30~45分钟]{.underline},讲解如何增加通信模块,与上位机进行数据交互

基于FPGA使用Verilog HDL来进行复杂数字电路设计,关键点是掌握结构化的建模以及调试方法。在讲解中应重点强调一个电路对应一个module,一个module对应一个文件,以及在顶层文件中实例化模块、完成模块间连线,尽量不在顶层文件中写逻辑等结构化建模的基本要求。此外,还应强调顶层文件设计中的常见错误,譬如忘记声明中间信号等低级但又很难发现的错误(特别是在复杂的设计中)。

增加通信模块后,整个电路就会比较复杂(见7.6节的图10)。虽然这部分内容在前面的课程中已经完成了,但由于模块较多,模块间的连接关系必须非常清楚,才能构建出最终的系统。讲解中,应将重点放在模块在系统中的作用以及信号流通路,对数据组帧模块(uart_NbyteTran_3byteData_controller)的实现,特别是其中状态机的实现,应重点介绍。同时,应复习顶层文件的编写方法,并指出容易犯的错误,譬如忘记声明某个中间信号等。

由于在前面的课程中,已经完成上位机simulink模型的编写,本次课只是直接使用,简单介绍即可。

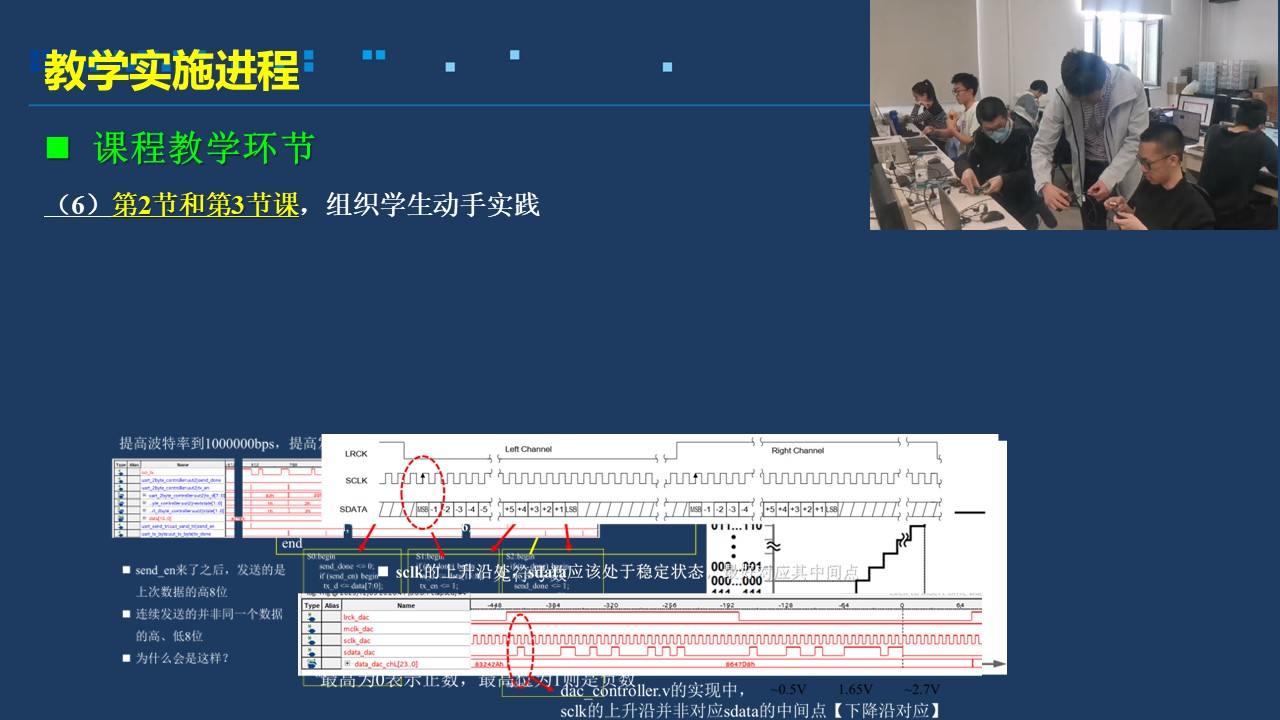

6)[第2节和第3节课]{.underline},组织学生动手实践

学生开始ADC接口逻辑电路的编写和调试。此时,有部分学生可能已经完成的代码的编写,在次过程中,教师应密切关注这些学生,通过交流了解学生对时序图的理解情况。

在实验指导中,应逐步引导学生使用逻辑分析仪进行调试,因为很多学生急于任务的完成,通常是进行盲调(直接下载看结果),这种只关注结果的方式是不利于知识的系统把握的,很多时候只能是知其然而不知其所以然。在调试中,还要指导学生如何使用示波器抓时序图,结合SCLK和SDATA来分析数字信号的采样窗口,强化时序电路的时序约束概念。

在实践过程中针对学生调试中出现的共性问题或有启发性的问题,至少组织2~3次专题讨论,深化学生对核心知识点的理解。讨论中,要反复强调调试方法的重要性,遇到问题,应主动思考,根据课前制定的预案进行应对。

8.3工作任务 {#工作任务}

1)教师

(1)明确实验的目的是掌握时序电路的设计方法,培养学生进行复杂数字设计的能力。

(2)主动去发现学生的问题,特别是不太爱交流的学生,应引导学生应用各种手段来解决问题。因为涉及到硬件调试,设备使用及软件配置等方面的问题,应及时予以解决。

(3)鼓励学生提出问题,通过学生的问题,判断其对知识的掌握情况,进行针对性地指导。

2)学生

(1)完成实验任务,给出逻辑分析仪的输出结果以及示波器测试的时序图。

(2)能清晰地根据时序图分析电路;

(3)能熟练的根据需要修改电路参数,譬如采样率的修改等。

实验报告要求

实验报告需要反映以下工作:

1)按预习任务要求撰写预习报告,明确ADC的工作模式及各控制信号之间的时序关系;

2)接口逻辑的设计框图,接口逻辑的实现代码及详细注释。

3)顶层文件的设计框图、实现代码及详细注释。

4)结合逻辑分析仪得到的时序图,进行时序分析,判断是否满足时序约束要求。

5)概括本实验的要点,给出结论;总结经验并提出改进方案。

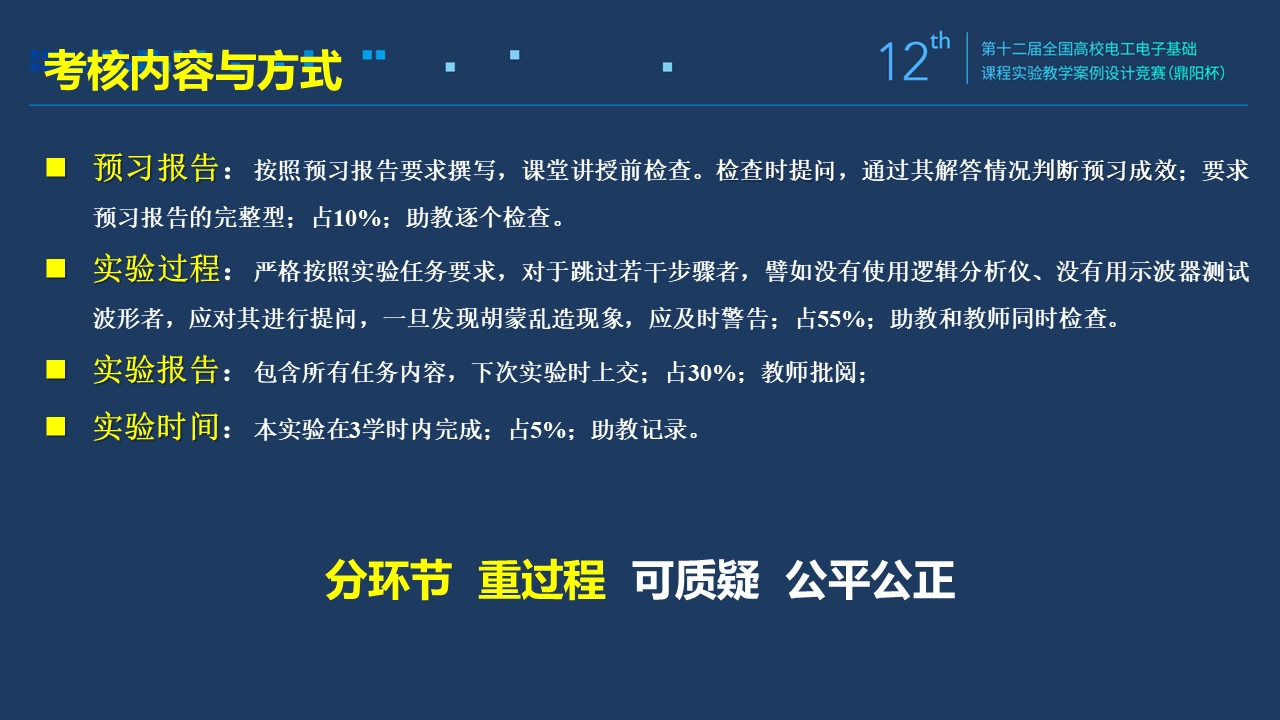

考核要求与方法

1)预习报告:按照预习报告要求撰写,课堂讲授前检查。检查时提问,通过其解答情况判断预习成效;要求预习报告的完整型;占10%;助教逐个检查。

2)实验过程:严格按照实验任务要求,对于跳过若干步骤者,譬如没有使用逻辑分析仪、没有用示波器测试波形者,应对其进行提问,一旦发现胡蒙乱造现象,应及时警告;占55%;助教和教师同时检查。

3)实验报告:包含所有任务内容,下次实验时上交;占30%;教师批阅;

4)实验时间:本实验在3学时内完成;占5%;助教记录。

项目特色或创新

1)本案例内容层层推进,环环相扣,厚基础、重应用;任务看似简单,却暗藏“陷阱”。涉及实际芯片的接口逻辑电路,对深入理解时序电路的时序图、时序分析等基本概念,加深对核心知识点的掌握有很好的促进作用。

2)本案例基于数字设计,采用结构化建模方法,在FPGA上构建了一套实用电子系统,并结合MATLAB/Simulink工具实现了上位机通信模型,是对电子技术理论课核心概念的深化和拓展。

3)本案例具有很强的综合性和实战性,不但能提高学生综合应用所学知识进行数字设计的能力,还能开拓学生的视野。