基于FPGA的波形发生器设计

实验题目:基于FPGA的波形发生器设计

------"芯"火相传、"波"动世界 {#芯火相传波动世界}

课程简要信息

课程名称:FPGA及电子CAD

课程学时: 24学时

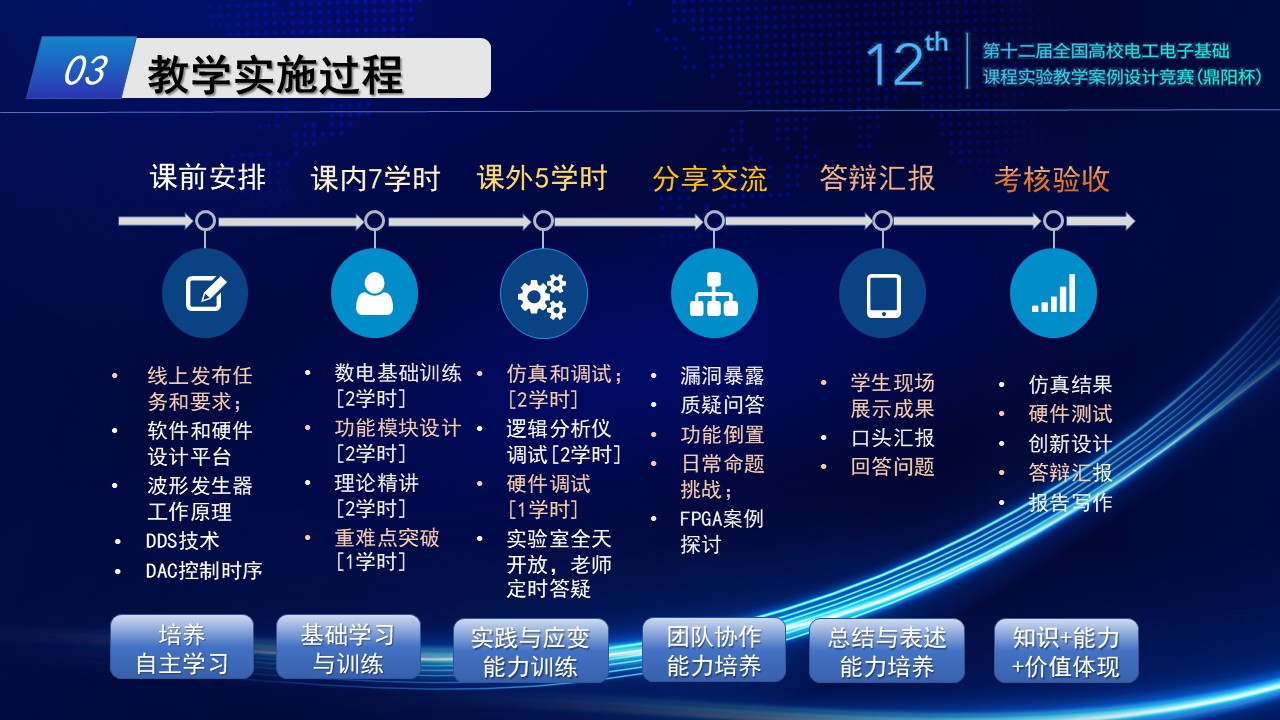

项目学时:12学时(课内7学时+课外5学时)

适用专业:电气工程及其自动化、自动化、智能电网信息工程等

学生年级:(二年级,春季学期)

实验内容与任务(限500字,可与“实验过程及要求”合并)

本实验要求使用可编程逻辑器件FPGA设计一个波形发生器电路,使用EDA工具实现电子设计自动化,了解硬件描述语言和现代电子技术的设计技巧。使用AIGC贯穿实验全过程,搜索相关文献和辅导资料,在理解和掌握组合逻辑电路、时序逻辑电路等知识点的基础上,通过阶梯递进式的实验任务,引导学生完成高阶性和创新性实验设计。教学过程中教师利用AIGC进行智能辅助教学,制作知识图谱和思维导图,因材施教,个性化答疑;学生利用AI进行预习和解决实验问题。

①实验基本要求:用硬件描述语言VHDL编程实现电路功能,能够产生锯齿波、三角波、方波以及正弦波四种波形,并且可以根据需求选择输出其中一种波形,同时具备调频、调幅、调占空比的功能。

②实验提高要求:虚实融合,虚拟仿真和硬件测试。

-

七段数码管显示实时数据;

-

液晶LCD显示字符和简易图形;

(3)QUARTUSII软件进行vwf波形仿真;

(4)通过逻辑分析仪进行波形调试;

(5)掌握DAC9767接口控制时序,通过开发装置扩展子卡连接示波器显示。

③实验拓展性要求:

(1)基于DSP BUILDER的DDS实现波形发生器;

(2)自主开发设计其他任意波形,要求产生的波形具有相噪好、频率步进低、输出电平分辨率小和相位可调等优点。

实验过程及要求(限300字)

(1)团队分组,分工合作;

(2)分析系统工作原理,选择合理方案,根据开发装置,设计实验原理框图;

(3)掌握DE2-115装置和 QuartusII 功能和操作;

(4)根据知识图谱学习 FPGA

知识,学习VHDL编程语言,采用层次化设计方法,设计各功能模块,并进行仿真及优化;依据实验方案,设计五个功能模块:波形数据产生模块、波形选择模块、频率控制模块、幅度控制模块和波形输出控制模块。

(5)将各功能模块组成完整系统,进行编译和管脚分配,进行系统级虚拟仿真;

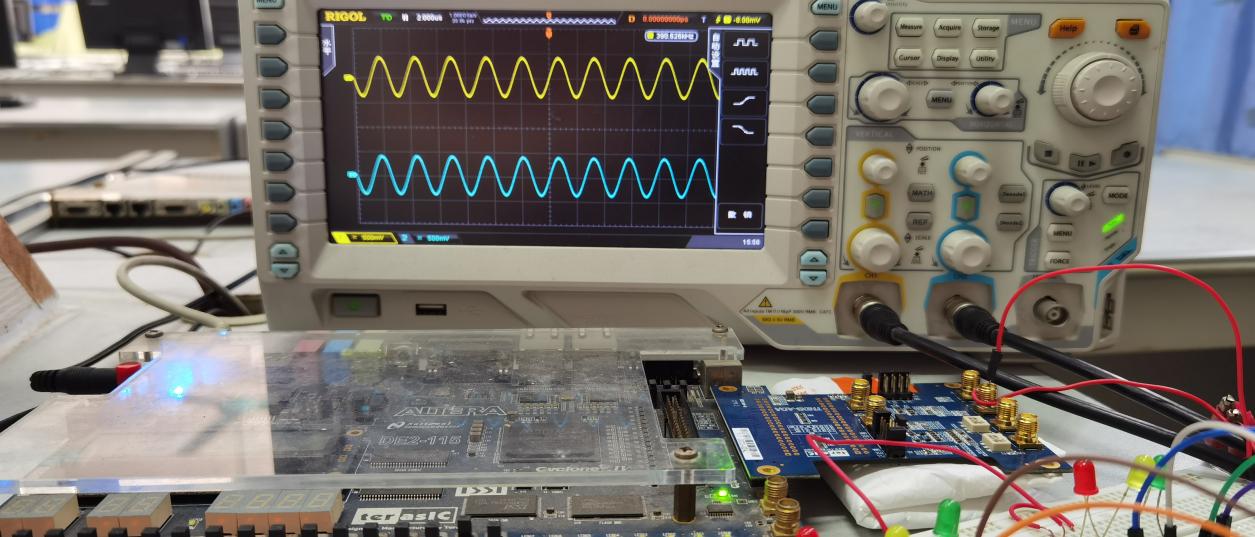

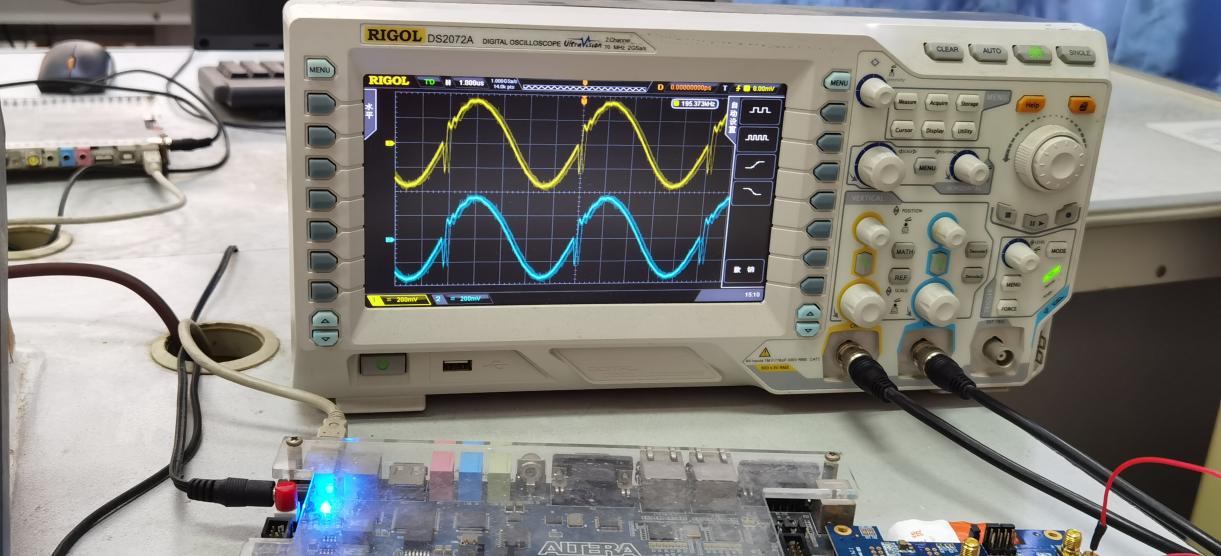

(6)将电路下载到FPGA,连接子卡ADA和示波器,进行硬件功能测试,调试参数,优化方案,鼓励优秀小组进行创新设计;

(7)分享交流,案例探讨,验收与考核;

(8)撰写设计报告,演讲答辩。

相关知识及背景(限150字)

对标专业认证标准,聚焦"数字系统设计能力"培养。FPGA是现代数字系统设计的核心载体,全球市场规模年增10.8%,国产化率30%,波形发生器是通信和测控等领域的基础模块。学生已掌握VHDL基础和QUARTUSII开发流程,但缺乏系统性项目开发经验及对DDS理解抽象化。为此,采取了系统级的EDA设计方法,完整的闭环开发过程, 虚实融合的教学将DDS具象化。

实验环境条件

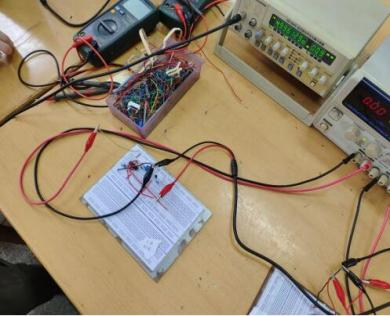

项目实施需要的实验资源,包括实验室开发装置,设计软件工具,配套实验室仪器设备设备(稳压电源、毫伏表、万用表、示波器、信号源等)以及实验所需的各种元器件。

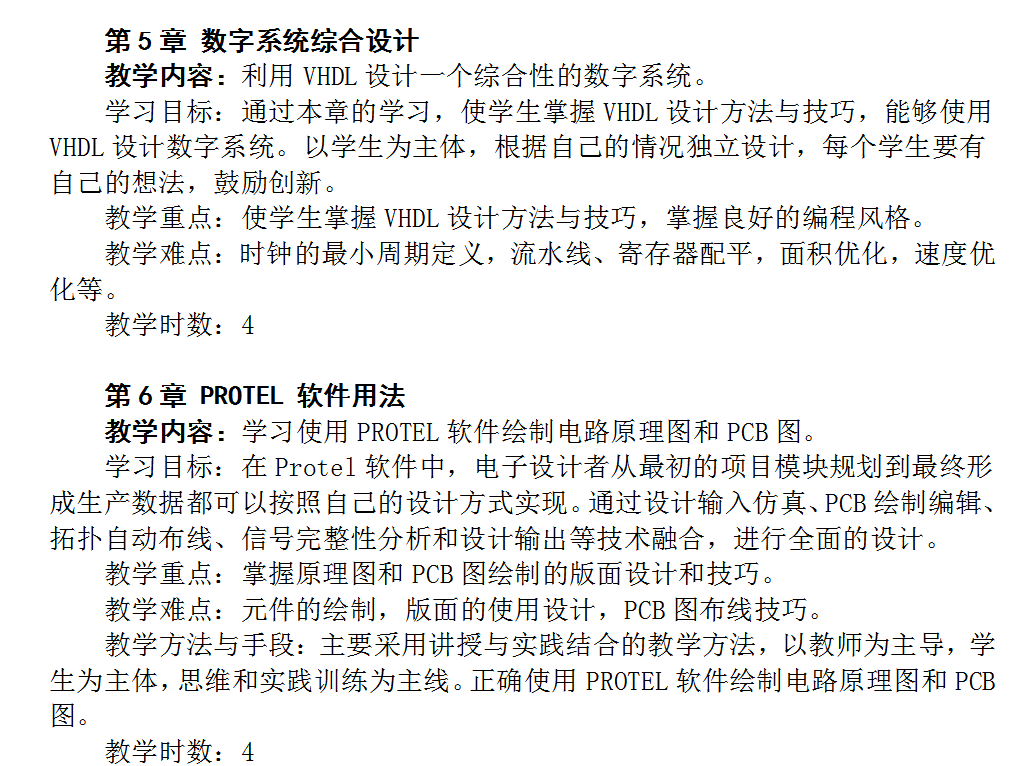

(1)硬件环境:

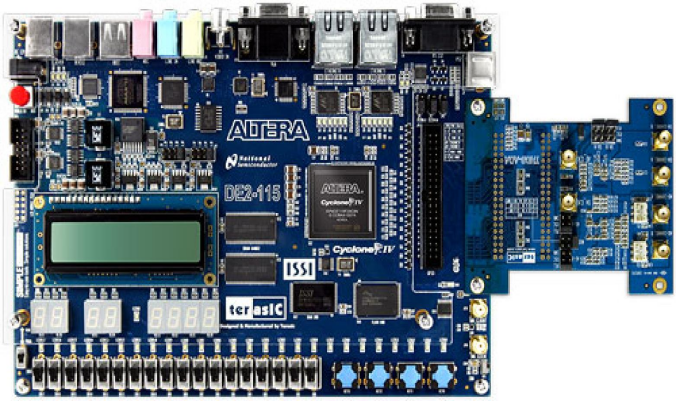

硬件平台需要计算机、FPGA 开发装置、USB 传输线。其中,FPGA 采用

DE2-115开发板,该板集成了EP4CE115F29c7芯片;板上 USB Blaster 用于编程。

EP4CE115F29c7 包含 114480个逻辑单元,2MB SRAM,2 片 64MB SDRAM,8MB

闪存,SD 卡插槽,4 个按钮开关,18 个滑动开关,18 个红色 LEDs, 9 个绿色

LEDs,8 个七段显像管,50MHz 晶振提供给时钟源,24-bit CD-品质声道 CODEC

带有线路输入, 线路输出和麦克风输入接口, VGA DAC (8-比特高速三通道 DACs)

带有 VGA 输出接口, TV 解码器 (NTSC/PAL/SECAM) 和 TV 输入接口, 2

千兆以太网 PHY 带 RJ45 连接器, 带有 A 类和 B 类 USB 接口的 USB

主从控制器, RS-232 收发器和 9 针连接器, PS/2 鼠标/键盘接口,IR 收发器, 2

个 SMA 接头,用于外部时钟输入/输出, 1 个 40-pin 扩展口,带二极管保护,1

个 HSMC 连接器,16x2 LCD 模组。

图 1 DE2-115开发板及扩展子卡ADA-HSMC

(2)软件环境

本实验需要用到的软件工具主要包括: FPGA 开发软件采用 QuartusII ,FPGA

仿真软件ModelSim,MATLAB 等。

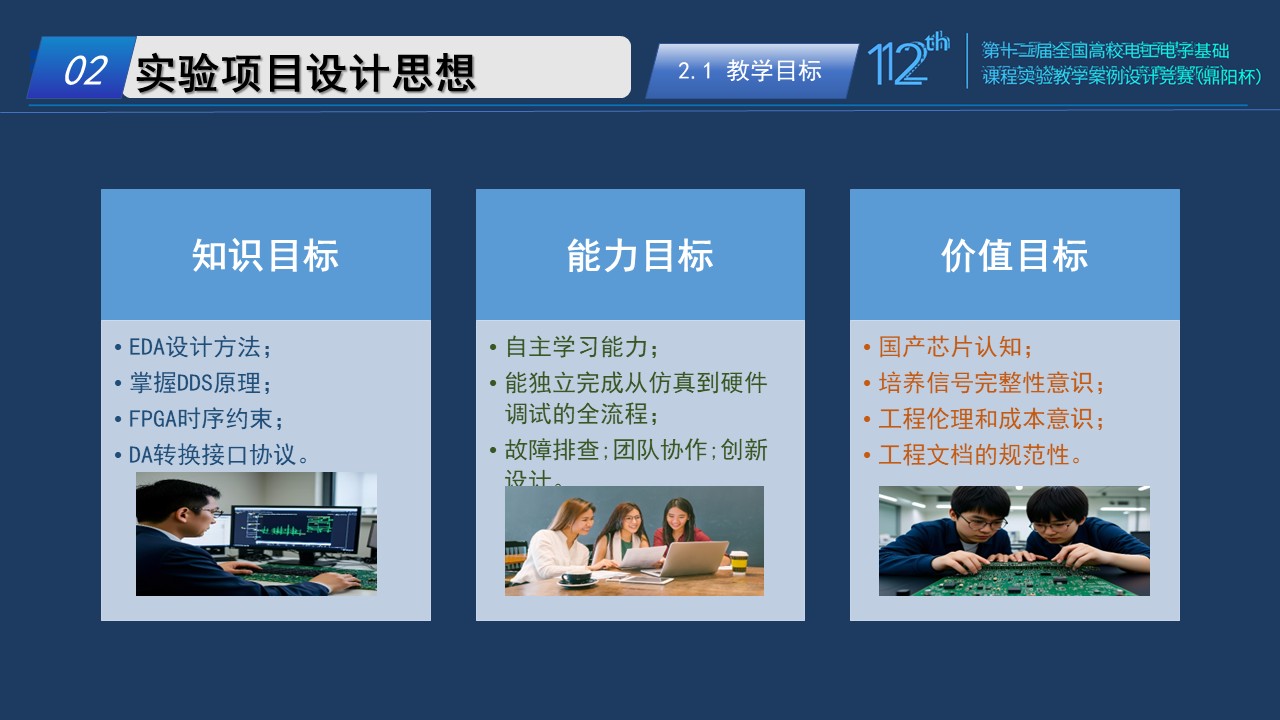

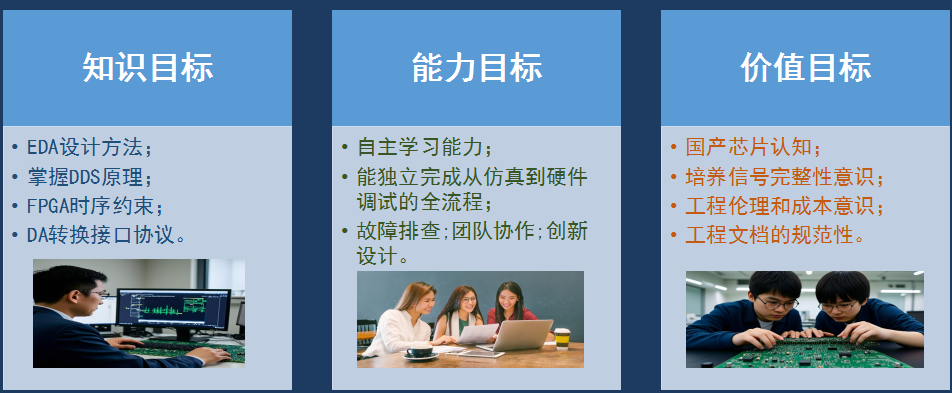

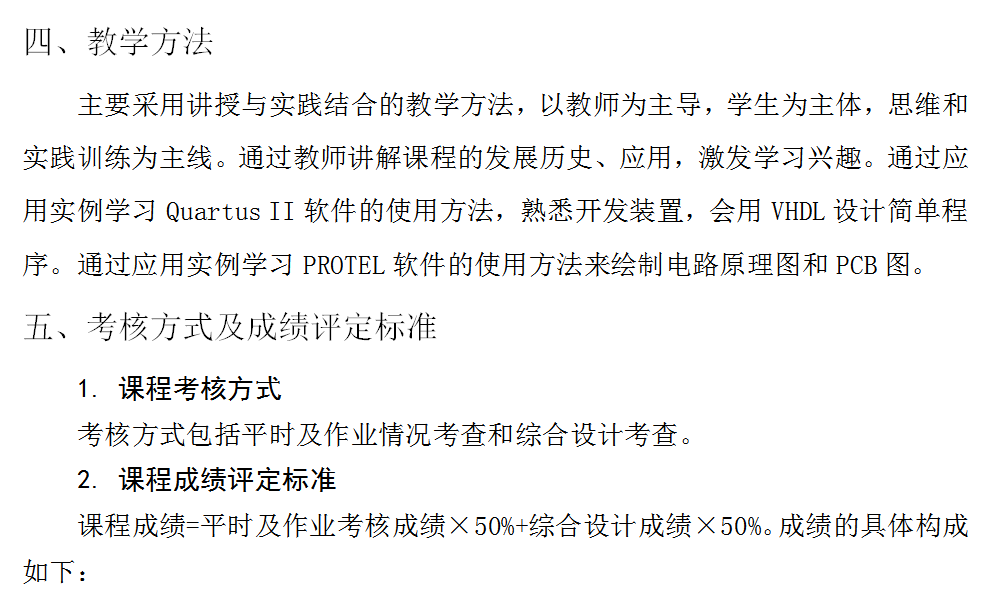

教学目标与目的(限150字)

围绕知识、能力、价值三维目标,通过一个完整的“波形发生器”工程项目,培养学生系统性工程项目设计能力。AI赋能,引导学生完成方案分析、电路设计、软件到硬件调试全过程;采用虚实双驱教学手段,引导学生突破核心技术,培养创新思维;通过分享交流、团队协作、实验报告写作和答辩演讲,培养学生工程实践能力。

图2 教学目标

教学设计与实施进程

本课程的实验过程是一个比较完整的工程实践工程,需要经历原理预习、参数论证、电路性能测试、现场调试、数据测量、波形观察、设计总结及项目拓展等过程。

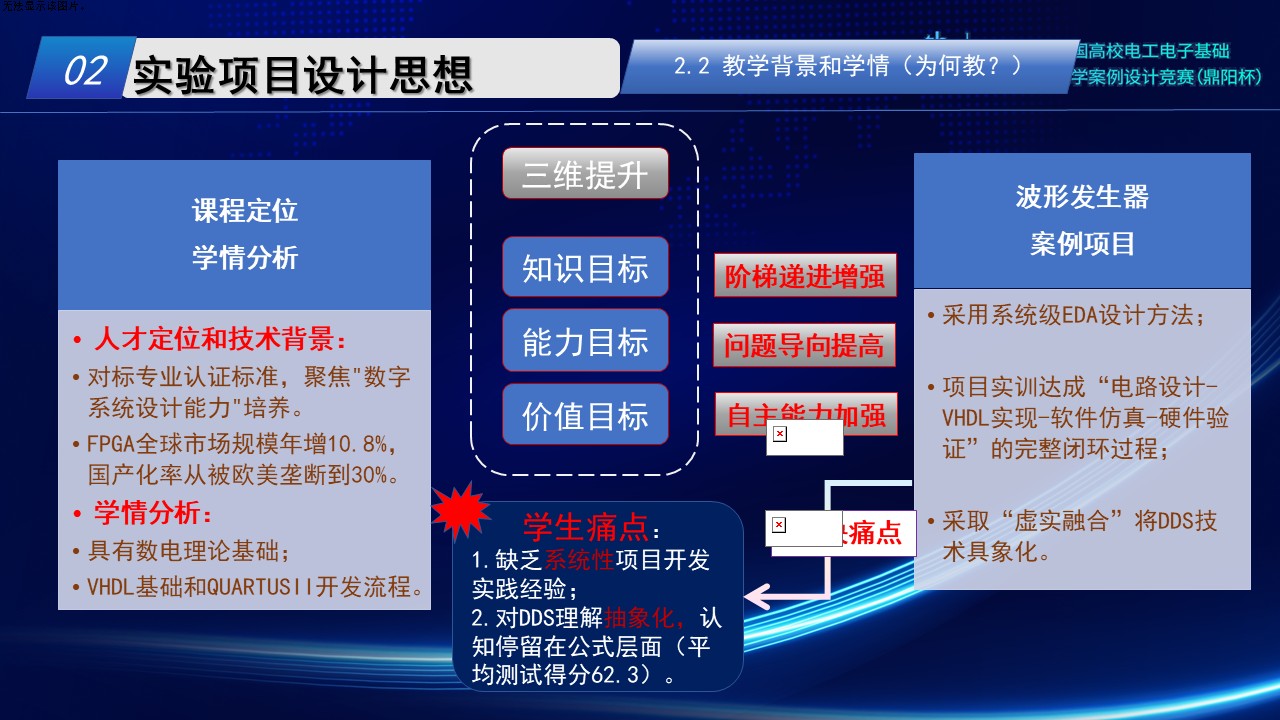

7.1 项目设计思想:

①教学背景和学情(为何教?)

人才定位和技术背景:对标专业认证标准,聚焦"数字系统设计能力"培养。FPGA全球市场规模年增10.8%,国产化率从被欧美垄断到30%。

学情分析:学生经过前置课程的学习,已具有数电理论基础,并掌握了VHDL基础语法和QUARTUSII开发流程。学生薄弱点在于缺乏系统性项目开发实践经验以及对DDS理解抽象化,认知停留在公式层面(平均测试得分62.3)。

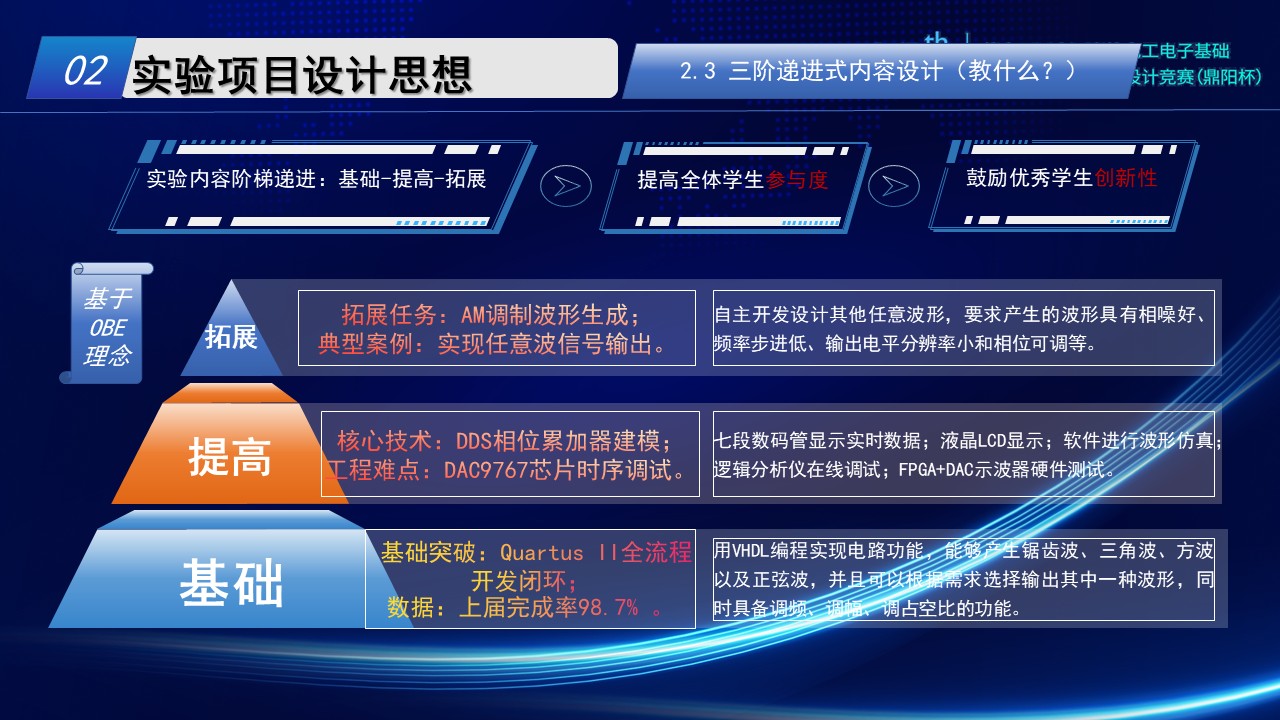

②三阶递进式内容设计(教什么?)

基于OBE理念,实验内容设计阶梯递进:基础-提高-拓展。目的是为了提高全体学生参与度,同时鼓励优秀学生进行创新拓展。

基础内容设计:用VHDL编程实现电路功能,能够产生锯齿波、三角波、方波以及正弦波,并且可以根据需求选择输出其中一种波形,同时具备调频、调幅、调占空比的功能。进行Quartus II全流程开发闭环,激发学生兴趣。

提高内容设计:七段数码管显示实时数据;液晶LCD显示;软件进行波形仿真;逻辑分析仪在线调试;FPGA+DAC示波器硬件测试。解决核心技术即DDS相位累加器建模以及DAC9767芯片时序调试。

拓展任务设计:AM调制波形生成,实现任意波信号输出,要求产生的波形具有相噪好、频率步进低、输出电平分辨率小和相位可调等。

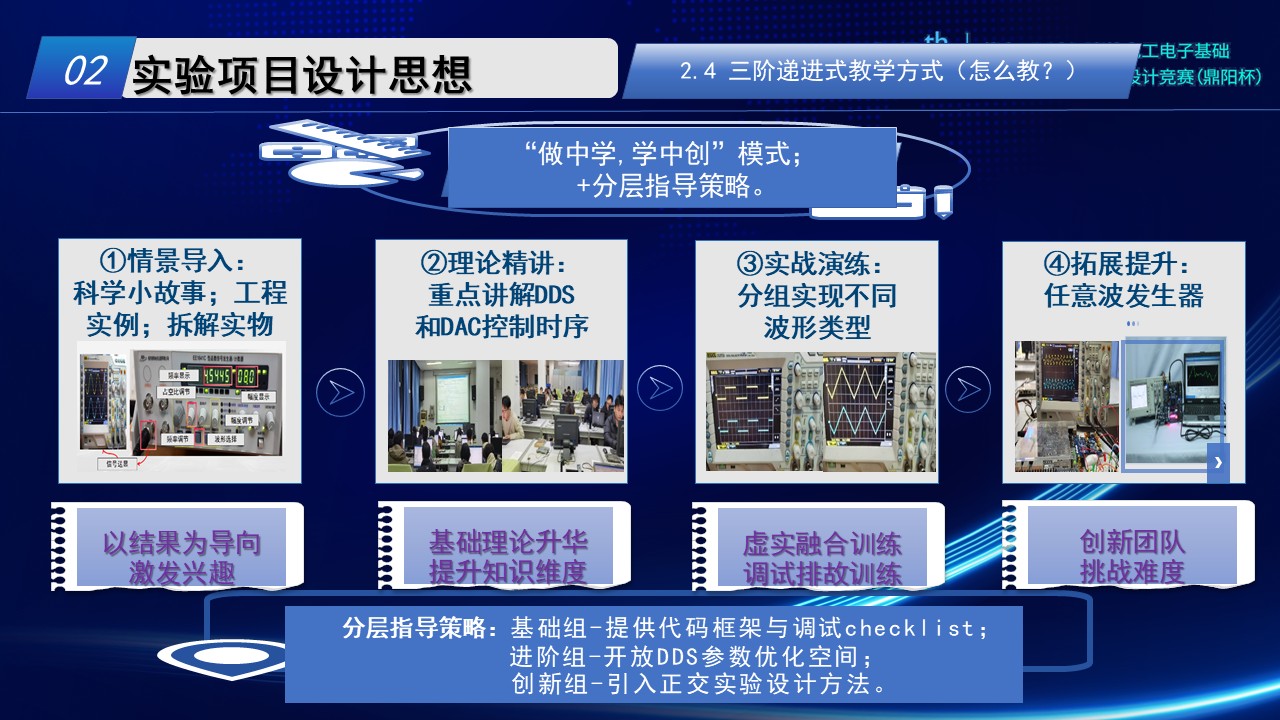

③ 阶梯递进式教学方式(怎么教?)

采取“做中学,学中创”模式以及分层指导策略。

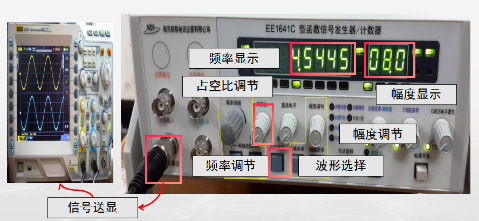

- 情景导入:以科学小故事、工程实例为导引激发学生兴趣;拆解信号发生器实物,以结果为导向。

此处思政融入点:引入华为海思、北斗导航等芯片开发强调自主可控性,激发学生科技报国的使命感,以及对于5G、量子通讯等增强国家科技实力的认同感。

图3 信号发生器实物

-

理论精讲:重点讲解DDS原理和DAC控制时序,提升学生知识维度。

-

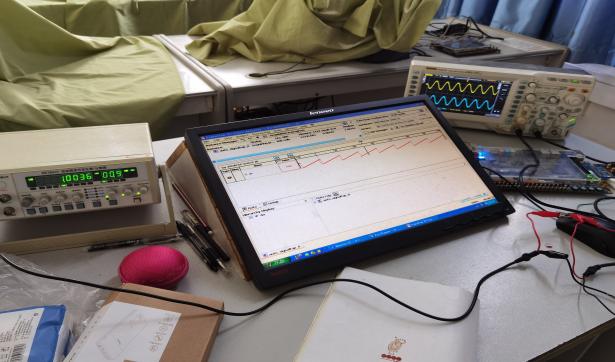

实战演练:分组实现不同波形类型,讨论互评,进行虚实融合训练和调试排故训练。用ModelSim进行虚拟仿真,用SignalTap II进行在线调试,用开发板加示波器进行硬件测试。全天开放实验室,让学生“练”起来,“调”起来,按钮调节参数,仿真软件和硬件演示波形变化,具象化DDS,使之可视可触。

此处思政融入点:强调环节和细节的重要性,注重实验操作的规范性,在调试实操环节反复优化方案,培养学生耐心、抗压能力和责任感,体现精益求精的工匠精神。

- 拓展提升:鼓励创新团队挑战难度,融合交叉学科,设计任意波发生器。

分层指导策略: 基础组-提供代码框架与调试checklist;

进阶组-开放DDS参数优化空间;

创新组-引入正交实验设计方法。

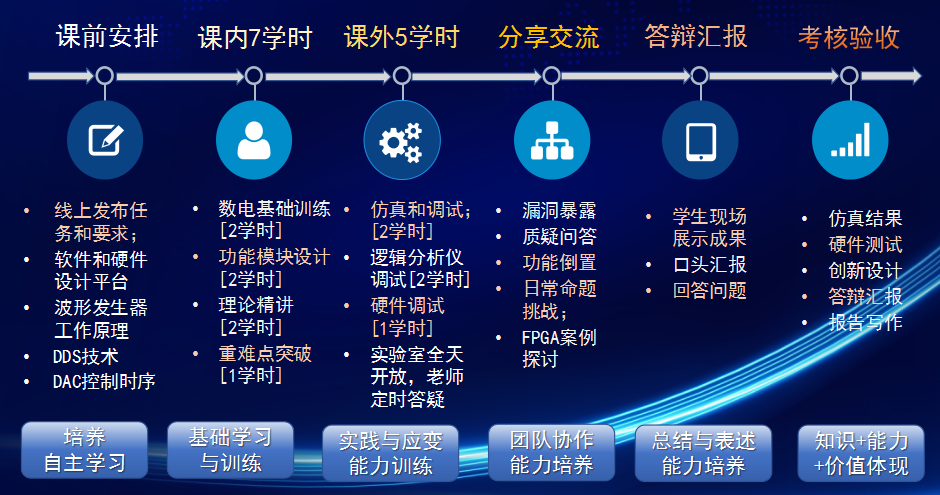

7.2教学实施过程:

图

4 实验课题实施流程

图

4 实验课题实施流程

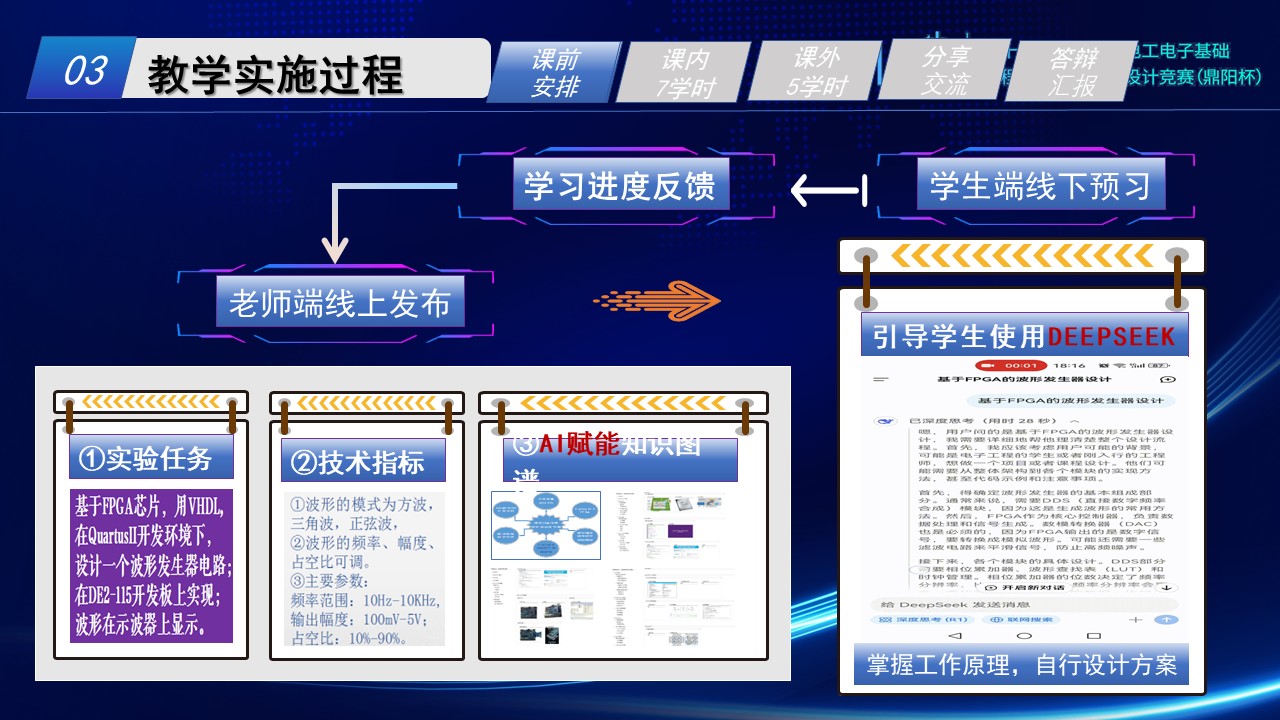

①课前安排:

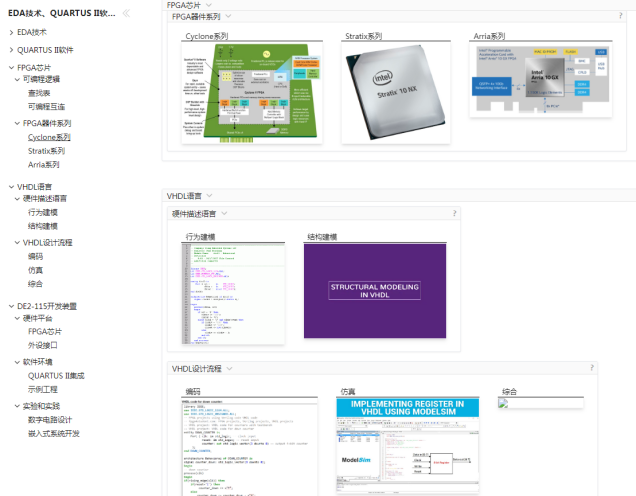

线上线下混合教学,长江雨课堂和QQ群布置课题任务书,发送实验室主要仪器设备的说明书以及操作视频等。要求学生预习数字电路理论知识,根据文献资料设计几种不同波形发生器设计方案,了解FPGA设计流程,熟悉QUARTUSII软件用法,了解开发装置DE2-115使用方法,学习VHDL语言编程规则。教师利用AI软件制作EDA技术相关软硬件知识图谱让学生快速入门。学生利用AI软件学习波形发生器工作原理,DDS技术。

图5 EDA技术相关软硬件知识图谱

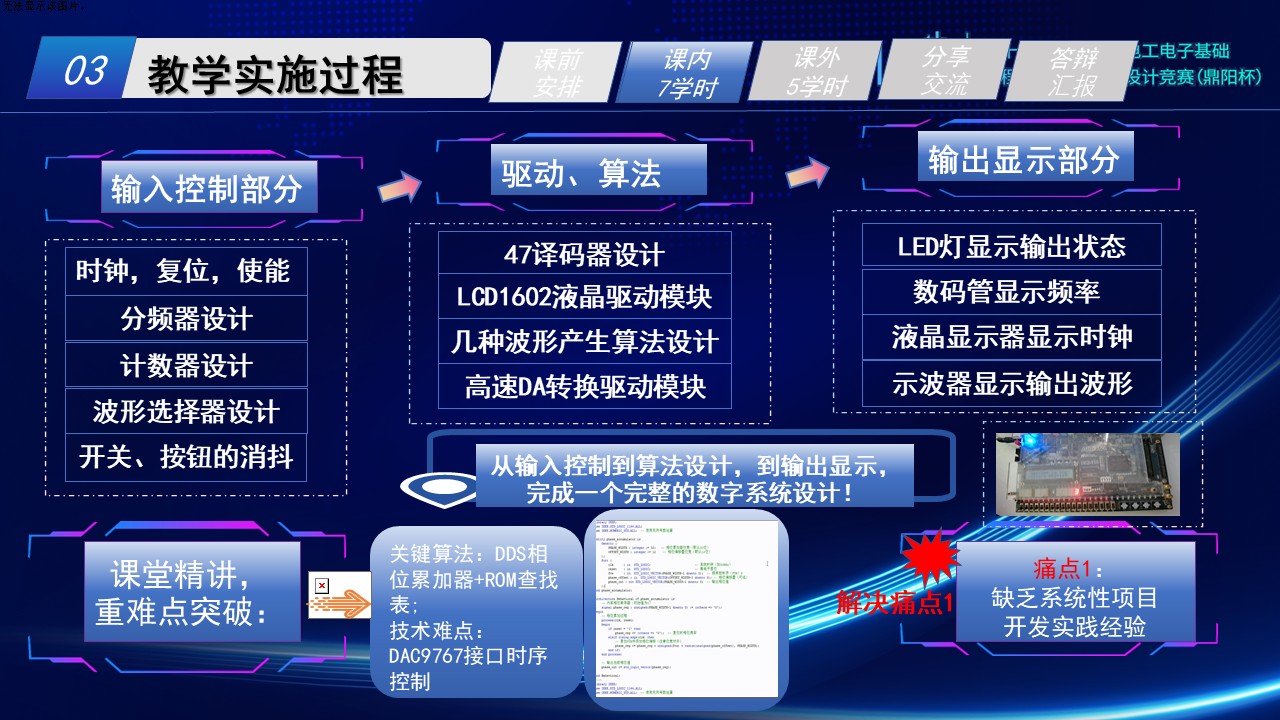

②课内7学时安排:

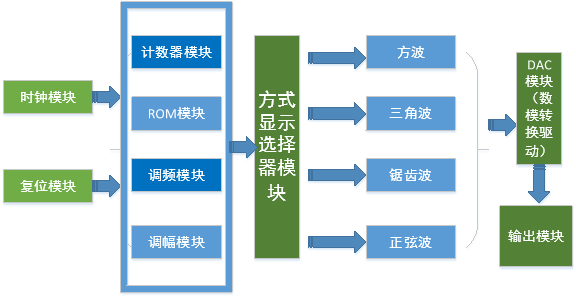

方案的确定:复习组合逻辑电路和时序逻辑电路的工作原理,掌握数字电路的设计原则。引导学生根据任务书要求确定实验方案,画出波形发生器的设计框图,思考如何用VHDL语言实现各主要功能模块,比如波形数据产生模块、波形选择模块、频率控制模块、幅度控制模块和波形输出控制模块等。从输入控制到算法设计,到输出显示,完成一个完整的数字系统设计!

(1)输入控制部分设计包括:分频器设计;计数器设计;波形选择器设计;开关、按钮的消抖。

(2)DAC驱动、DDS算法部分设计包括:47译码器设计;LCD1602液晶驱动模块;几种波形产生算法设计;高速DA转换驱动模块。

(3)输出显示部分设计:LED灯显示输出状态;数码管显示频率值;液晶显示器显示时钟;示波器显示输出波形。

(4)课堂精讲,进行重难点突破:关键算法即DDS相位累加器+ROM查找表的原理,DAC9767接口时序控制逻辑的掌握。

(5)引导学生对照波形发生器系统功能框图与开发装置的对应关系,熟悉硬件开发套件上的电路布局,确定装置外设(如晶振、LED灯、拨动开关、按钮、七段数码管、液晶LCD1602、扩展子卡THDB_ADA)等与 FPGA 芯片EP4CE115F29C7的电路管脚分配关系。

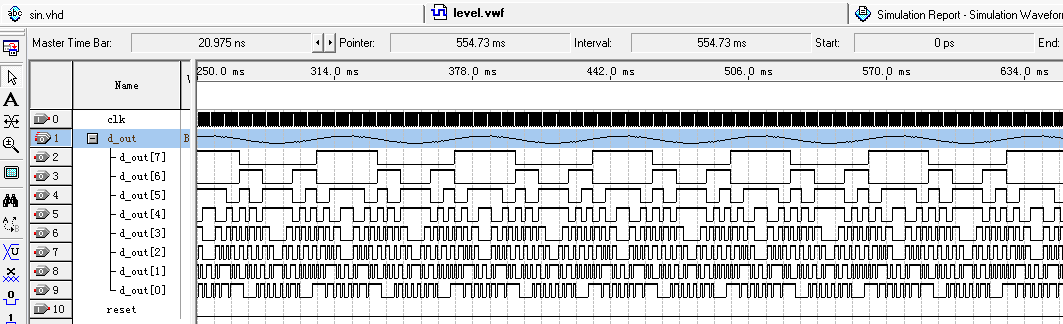

(6)各功能模块设计好后,引导学生完成各功能模块的功能验证,比如晶振要如何分频以及系统采样频率需要多少是合适的,方波、三角波、正弦波是如何编程完成的,波形仿真如何显示输出波形,如何用开关和选择器模块完成波形的切换,调频和调幅功能要如何完成等。

(7)引导学生思考如何完成系统的各种显示功能,比如如何用LED灯显示输出的状态;如何用七段数码管显示数值的大小;如何使用液晶LCD1602显示字符图形;如何使用逻辑分析仪进行动态仿真;如何使用扩展子卡将数字量转换成模拟量从而在示波器上显示波形等;

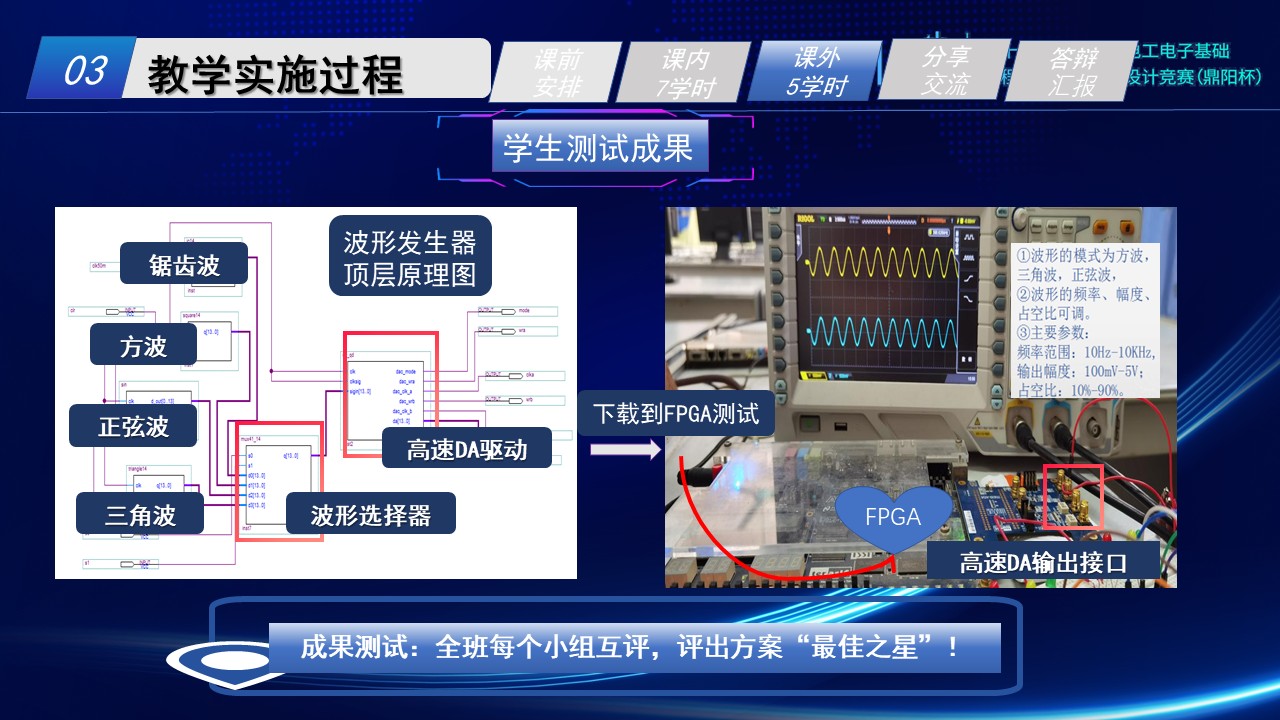

(8)引导各个小组设计不同的方案,将各个功能模块用原理图方式连接起来形成完整的顶层原理图,经过编译、管脚分配后下载到FPGA芯片,用开发装置进行功能性验证;分析数字量仿真波形结果和示波器模拟量波形结果的差别,实验中遇到问题要如何解决,分析问题根源并设计解决方案,加以验证,老师进行引导和协助。

③课外5学时安排:

-

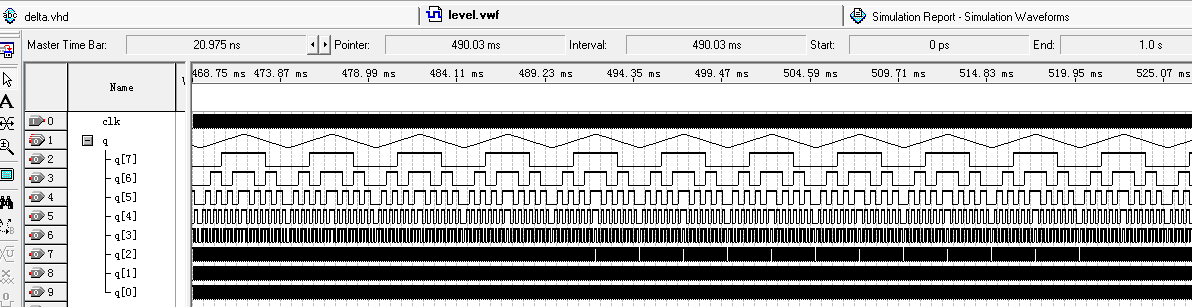

用ModelSim进行虚拟仿真;

-

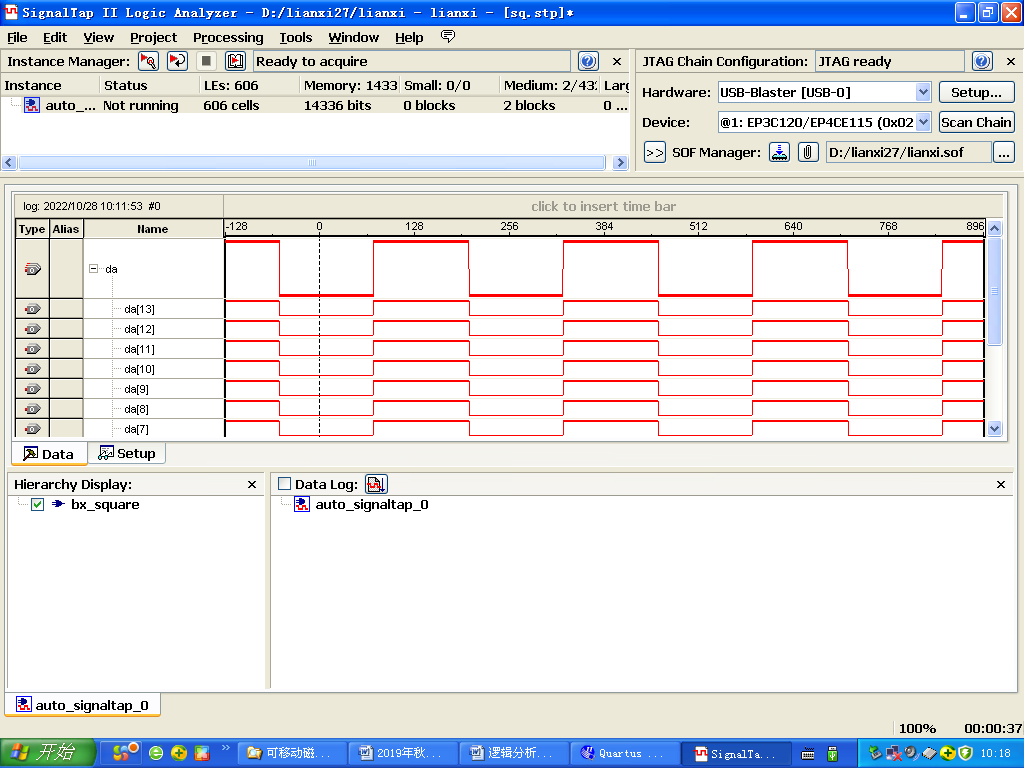

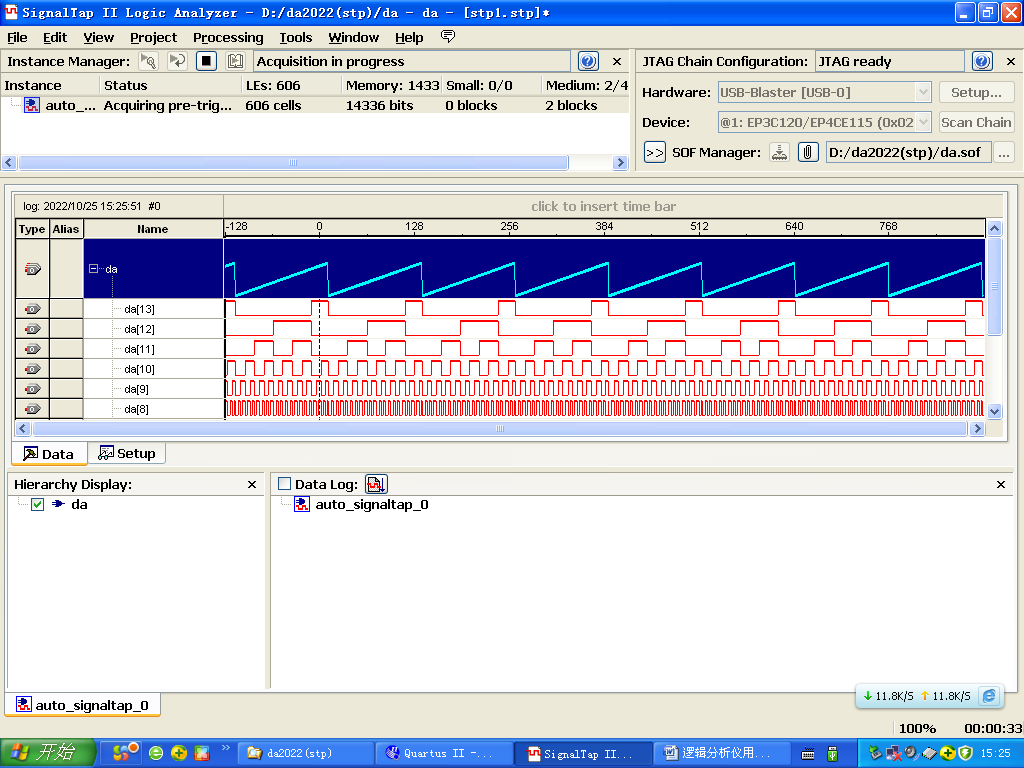

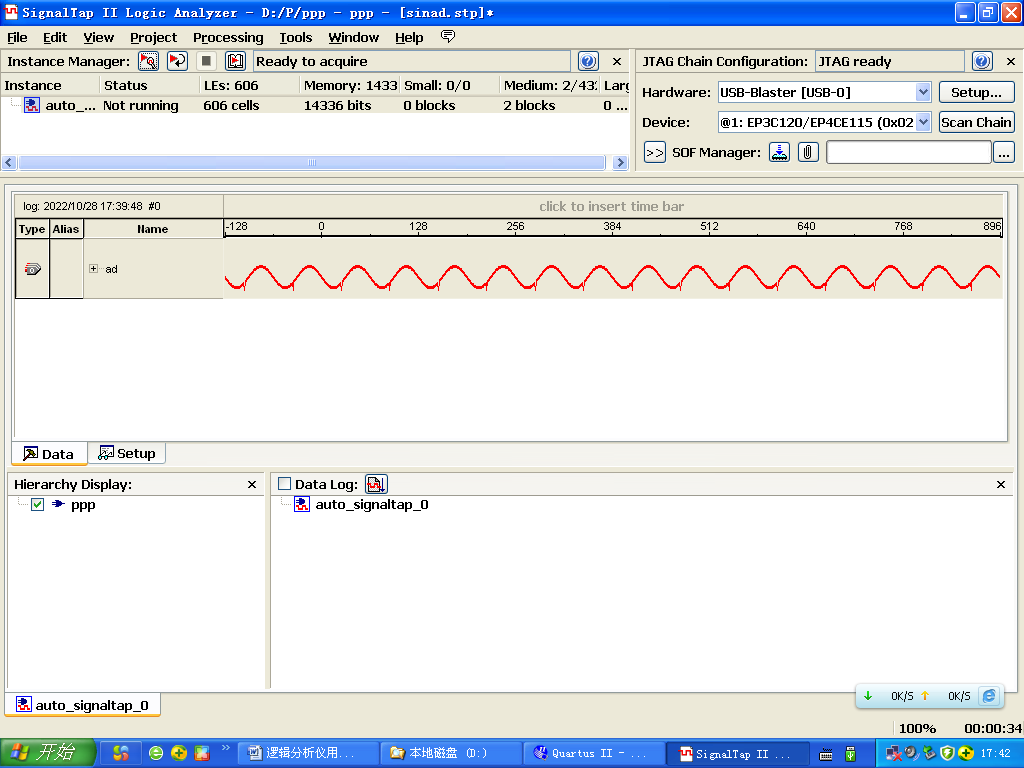

用SignalTap II进行波形在线调试;

-

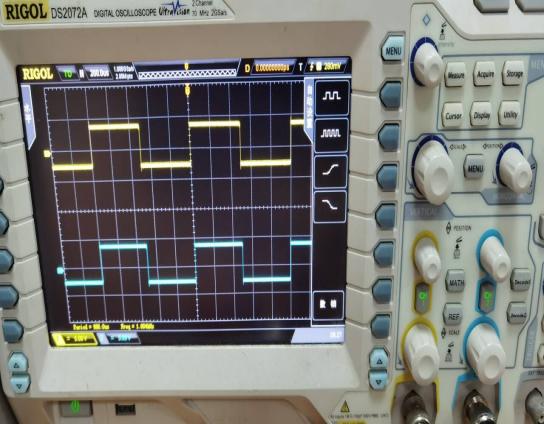

用示波器进行硬件测试。

-

虚实双驱,仿真与实测波形对比,各指标参数如频率和幅度以及占空比的调节是否满足任务书的指标要求。通过动态演示,学生能够直观理解DDS如何将数字控制参数转化为高精度模拟波形,同时掌握频率分辨率、相位噪声等关键概念,为实际系统设计提供可视化验证手段。

-

知行合一,数智赋能,进行排故能力训练。故障注入方波不平坦、三角波线性差、正弦波阶梯失真等,引导学生学习AI诊断原因,逐一排查,进而解决问题。让学生在实验室“练”起来,“调”起来,锻炼实操能力。

-

成果测试:全班每个小组互评,评出方案“最佳之星”!

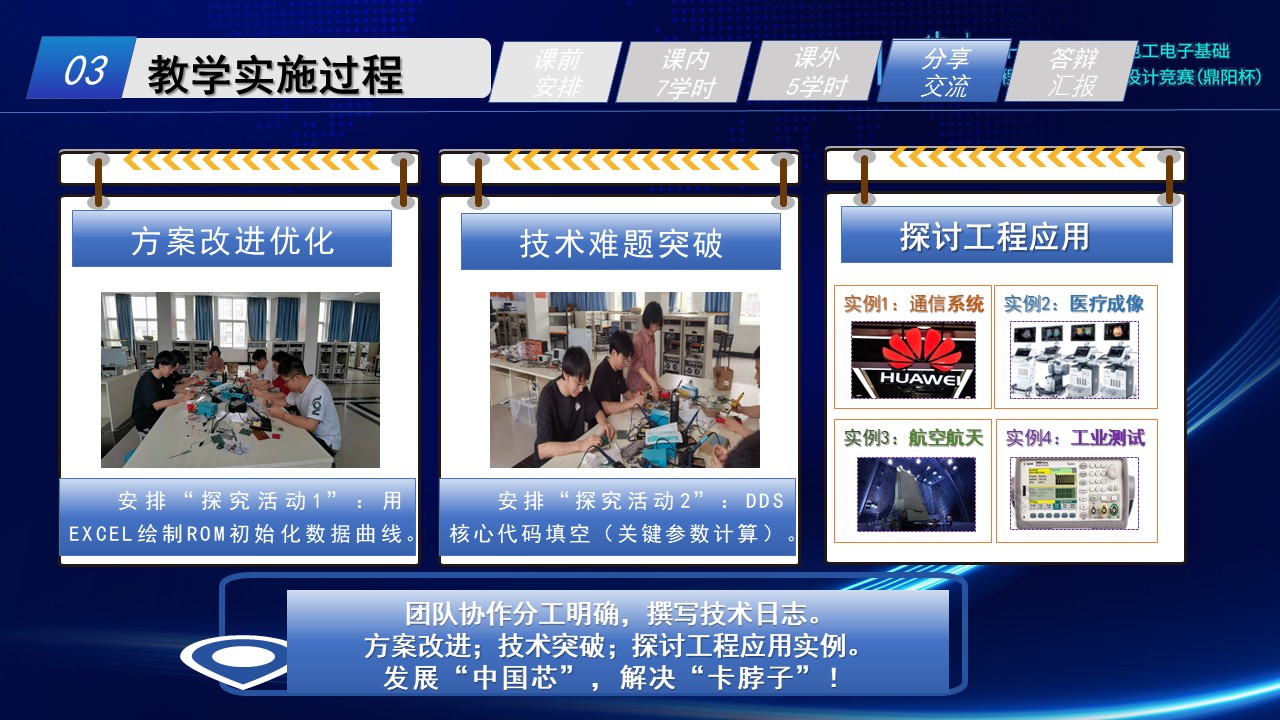

④分享交流:

团队协作分工明确,撰写技术日志。每次讨论安排探究活动作为主题。小组团队进行方案改进优化,关键技术的探讨和突破,探讨工程应用实例等,比如FPGA在通信系统、医疗成像、航空航天、工业测试等领域的技术突破和发展,发展“中国芯”,解决“卡脖子”。

(1)安排“探究活动1”:用EXCEL绘制ROM初始化数据曲线。

(2)安排“探究活动2”:DDS核心代码填空(关键参数计算)。

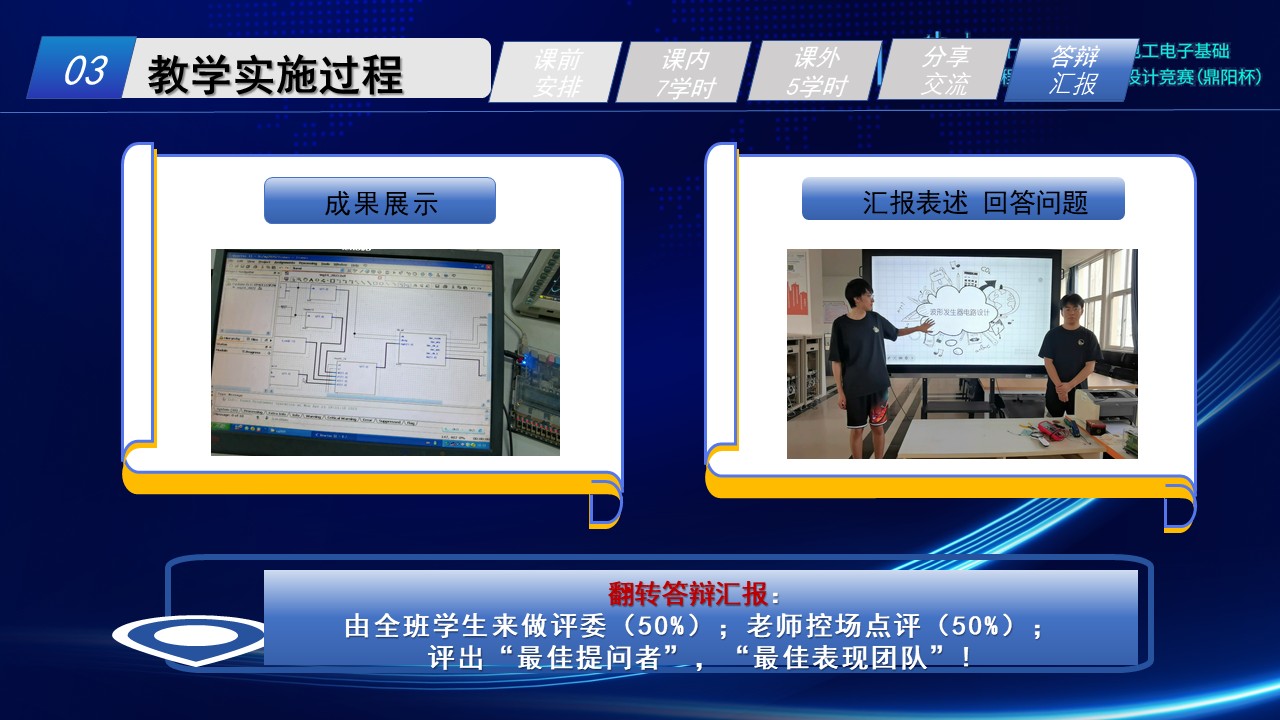

⑤答辩汇报:

(1)学生进行实验整体回顾与总结,写出实验报告,准备汇报答辩。

(2)教学设计翻转答辩汇报:由全班学生来做评委(50%);老师控场点评(50%);

全班评出“最佳提问者”,“最佳表现团队”!

实验原理及方案

本节介绍实验的基本原理、设计依据、完成任务的思路方法,可能采用的方法、技术、电路、器件。

8.1基本理论梳理:

(1)总体任务要求:借助EDA工具和自顶向下设计方法,学习用VHDL语言用编程的方法来设计一个波形发生器电路,使用可编程器件FPGA进行电路的仿真分析和硬件测试。技术要求:波形的模式为方波,三角波,正弦波,波形的频率、幅度、占空比可调。主要参数:频率范围:10HZ-10KHZ,输出幅度:100mv-5v;占空比:10%-90%。硬件测试要求:使用逻辑分析仪测试及通过扩展子卡的DA转换输出到示波器显示波形。

图 6 波形发生器系统基本功能框图

(2)掌握嵌入式逻辑分析仪的使用方法,对系统进行测试:

SignalTap II嵌入式逻辑分析仪是集成到Quartus II中的一个辅助调试工具, 它用于数字系统的检测和故障分析,它可以随设计文件一起下载于目标芯片中, 用以捕捉设计者感兴趣的目标芯片内部信号节点处的信息。

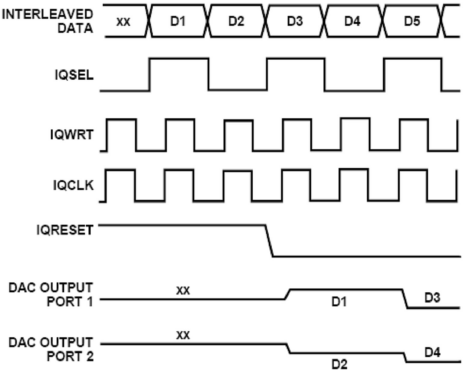

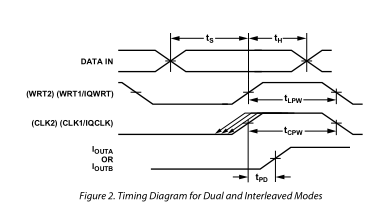

(3)掌握AD子卡AD9767数模转换工作原理和驱动模块的编写:

DAC9767集成了两个14位的TxDAC+核心,并具有双端口输入,同时支持高达125 MSPS的刷新率。双通道使其能够向两个独立端口传输不同数据,且更新率不同。

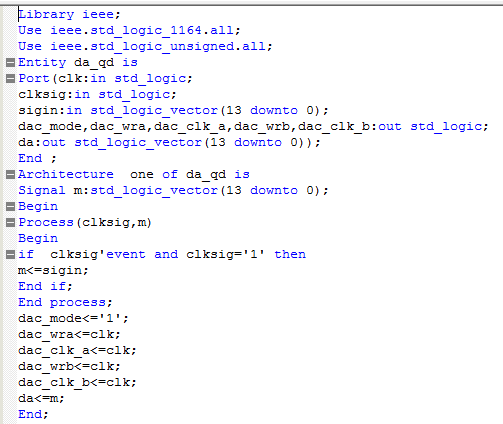

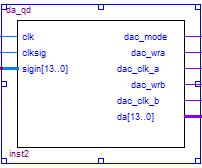

本实验项目重难点在于DAC驱动程序的编写。要求学生按照用户手册说明编写接口控制代码。

图7 用户手册数模转换模式时序图

根据ADA的分辨率和数模转换模式时序编写合适的驱动程序,部分代码和符号如下。

图8 ADA驱动模块设计

8.2电路各功能模块设计

①波形模式选择器:功能可以使用两路开关任意选择输出波形,要求掌握控制信号进行选择输出的编程方法。

②分频器设计:要求掌握如何将开发板提供的50M晶振时钟经过分频设计成任意频率的时钟信号。VHDL编程思路:分频器能够将将高频信号分割成较低频率的信号,将输入的时钟信号频率降低到原来的一个因数,这个因数被称为分频比。

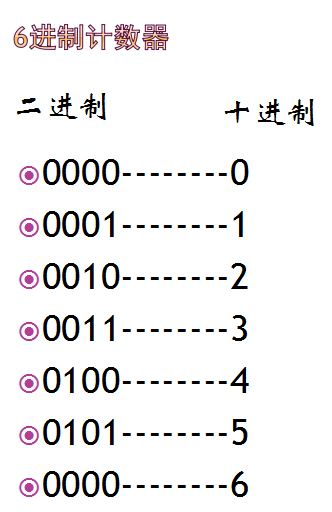

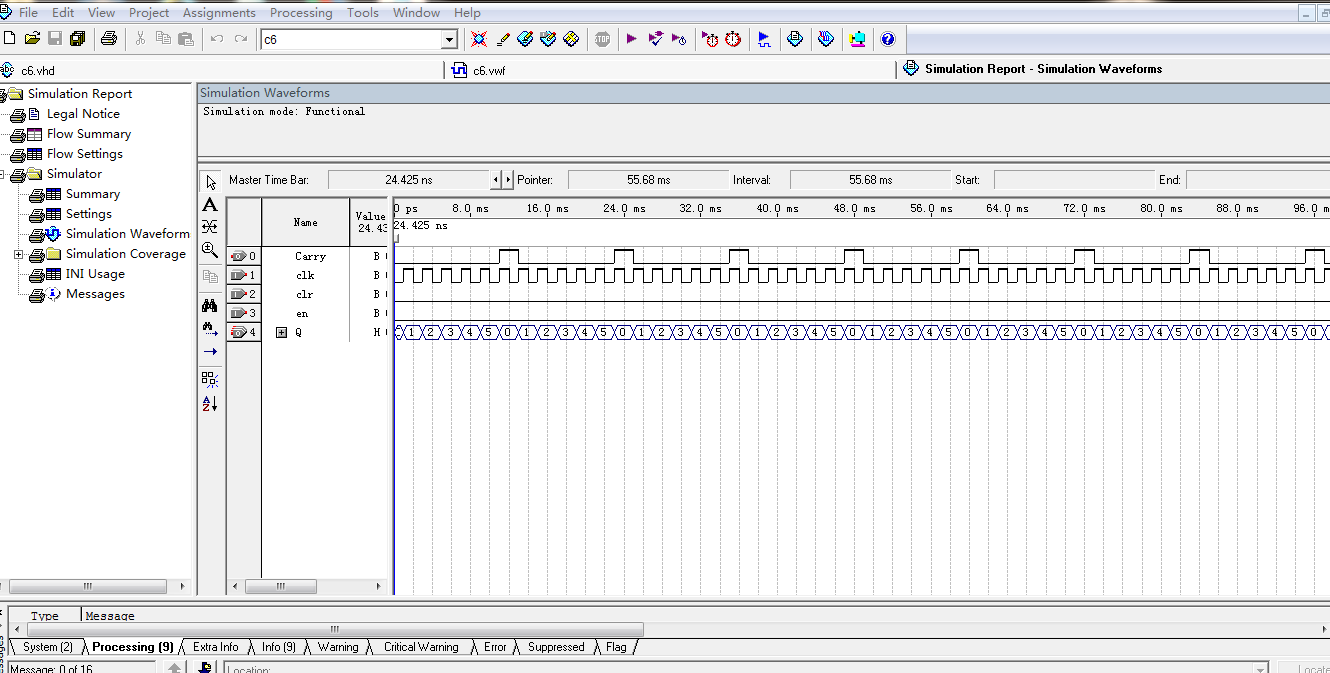

③计数器设计:

当输入脉冲进入计数器时,它会按照设计的逻辑被各个计数单元接收和存储。在掌握6进制计数器的设计过程基础上,要求能够设计任意进制的计数器。

图9 6进制计数器设计原理及仿真结果

④47译码器设计和LCD1602液晶显示驱动模块设计:

用VHDL来设计47译码器,用于将BCD码输入转换为七段码输出。掌握如何通过译码器的真值表和七段数码管硬件结构来编写代码。

用VHDL来编写液晶LCD1602显示模块,了解其驱动工作原理。

⑤分频计数译码小系统训练:

通过基本训练引导学生掌握电路设计流程,包括波形仿真和DE2-115开发装置各种外设的使用和硬件测试:

图10 开关和按钮控制方式,LED灯,七段数码管,LCD1602液晶显示

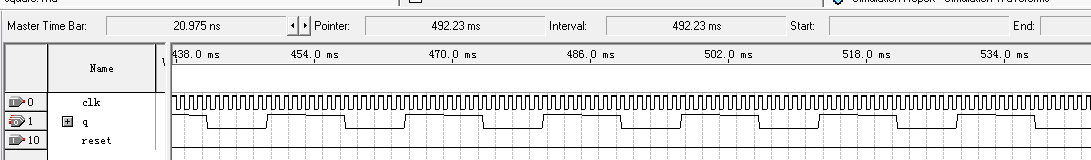

⑥方波程序设计:

工作原理:通过计数器或时钟分频来产生所需的频率,然后根据计数值切换输出电平。

基本实现思路:使用系统时钟作为输入; 通过计数器对时钟周期进行计数; 当计数值达到预设值时,翻转输出电平; 重置计数器,开始新的周期。

参数设计:定义常数指定方波频率和占空比;计算所需的计数器最大值。

引导学生设计改进方向:可以通过输入端口动态调整频率和占空比;设计多个独立可调的方波输出通道;增加相位调整功能;使用更精确的计数方法提高频率精度。

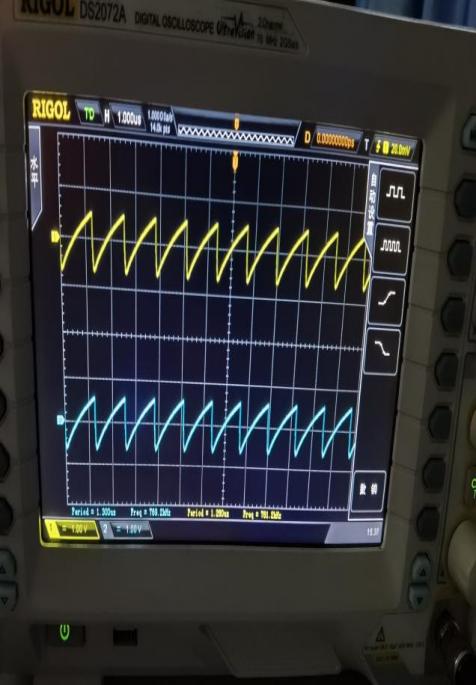

图11 方波的虚拟仿真,逻辑分析仪,示波器测试结果

⑦三角波(锯齿波)设计:

工作原理:三角波发生器是一种产生线性上升和下降波形的数字电路,其核心工作是通过可逆计数器实现数值的递增和递减,然后将计数值转换为模拟信号(或直接作为数字三角波输出)。

基本实现思路: 使用系统时钟作为输入; 通过可逆计数器实现数值的增加和减少;

当计数值达到上限时转为递减模式; 当计数值达到下限时转为递增模式; 输出计数器的值作为三角波信号。

参数设计:定义计数器位宽决定波形分辨率; 定义计数步长控制波形斜率;定义上下限值确定波形幅度。

图12 三角波(锯齿波)的虚拟仿真,逻辑分析仪,示波器测试结果

⑧正弦波程序设计:

工作原理:正弦波发生器是一种产生连续周期性正弦波形的数字电路,采用查表法或数字振荡器算法来完成。

查表法:预计算正弦波样本值并存储在ROM中;通过相位累加器生成地址索引; 从ROM中读取对应相位点的幅值。

数字振荡器算法:使用递推公式实时计算正弦值,比如CORDIC算法或差分方程法。

图13 正弦波的虚拟仿真,逻辑分析仪,示波器测试结果

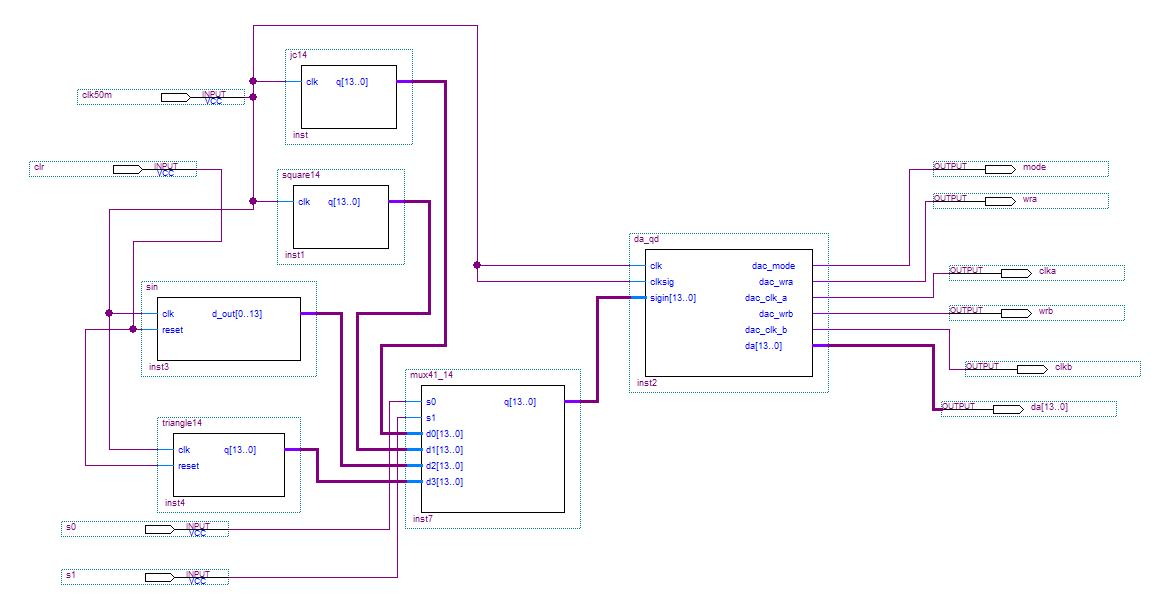

⑨波形发生器顶层原理图:

图14 波形发生器顶层原理图

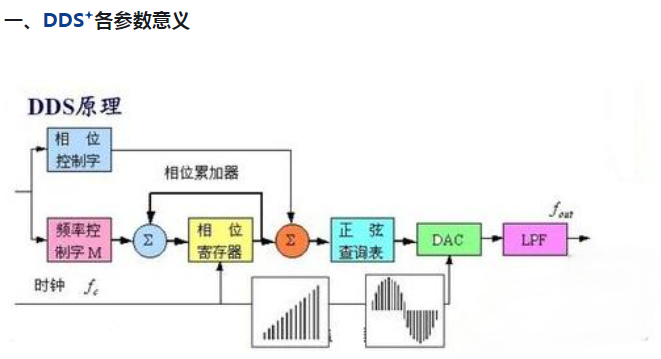

8.3 掌握DDS技术:

DDS技术是一种从相位概念出发直接合成所需波形的一种新的全数字频率合成技术,主要由相位累加器、正弦波形表、D/A转换器、低通滤波器组成。其基本原理:根据奈奎斯特采样定理,从连续信号的相位出发将一个信号取样、量化、编码,将采样值数字化后存入存储器作为查找表,然后通过查找表将数据读出,经过D/A转化器转化成模拟量,将存入的波形重新合成输出。

图15 DDS原理框图

输出频率:fout = (fclk * FTW)/(2^N)

其中FTW为频率控制字,fclk为参考时钟频率,N为相位转化器的字长。在实际应用过程中,通过改变读取ROM的地址数目来改变输出频率。通过修改ROM中的波形数据,可生成任意自定义波形(如调制信号、噪声等)。

8.4故障注入和学生排故能力训练:

故障问题:学生小组在实验过程中发现用VHDL编程设计的电路,软件仿真结果是正确的,但是通过数模转换后信号在示波器上显示的波形出现一些问题,方波不平坦、三角波线性差、正弦波阶梯失真等问题。

图16 实验测试波形失真图

原因的寻找:同学们借助AI工具探索原因。波形失真的原因可能包括DA转换器分辨率不足、时钟抖动、滤波器设计不当、阻抗不匹配、建立时间不足、量化误差、电源噪声或DA转换器的非线性误差等等。

问题的解决:学生通过实验逐一排查这些因素,最后有效改善了波形质量。

思政融入点:要求撰写技术日志,记录问题,探索原因,优化代码,反复调试,培养团队协作和责任担当精神。

实验报告要求

实验报告需要反映以下工作:

(1)分析波形发生器系统功能要求,国内外现状及需求分析,进行方案论证,绘制系统总体框图和流程图;

(2) 用VHDL编程设计各功能模块的代码、符号及波形仿真结果及性能分析;

(3) 顶层原理图文件设计图,总体软件波形仿真结果及性能分析;

(4)

FPGA芯片选择,传输设置,各输入输出信号的管脚配置,下载到DE2-115验证测试结果,示波器显示结果,调频调幅调占空比的结果及性能分析;

(5)

撰写工作日志,记录在实验过程中系统软件仿真或硬件测试中出现的问题、原因及解决的方法、效果等;

(6) 团队分工,进度安排,个人任务分解,实验过程设计;

(7)实验特色与创新,总结与反思,结论与展望;

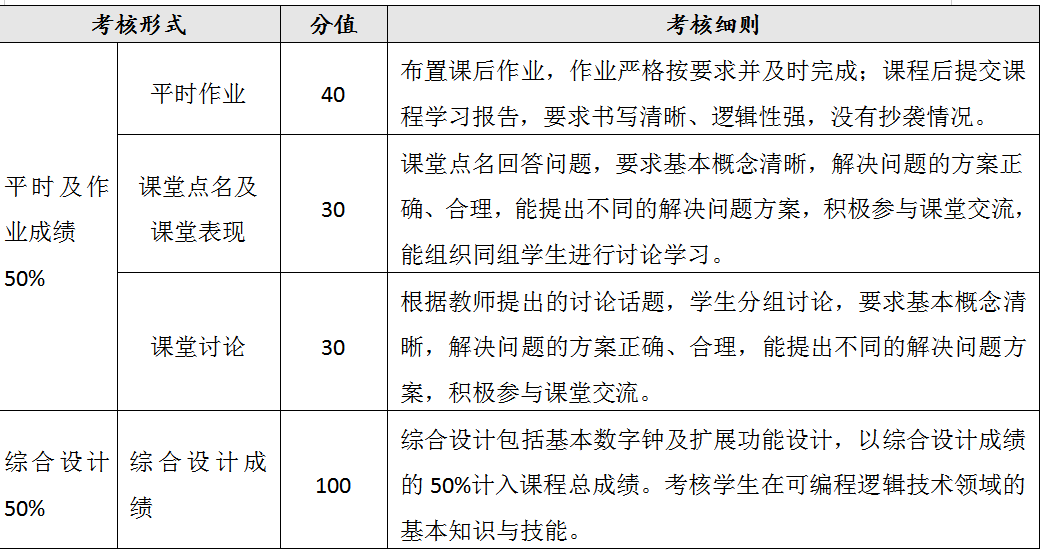

10.考核要求与方法(限300字) {#考核要求与方法限300字}

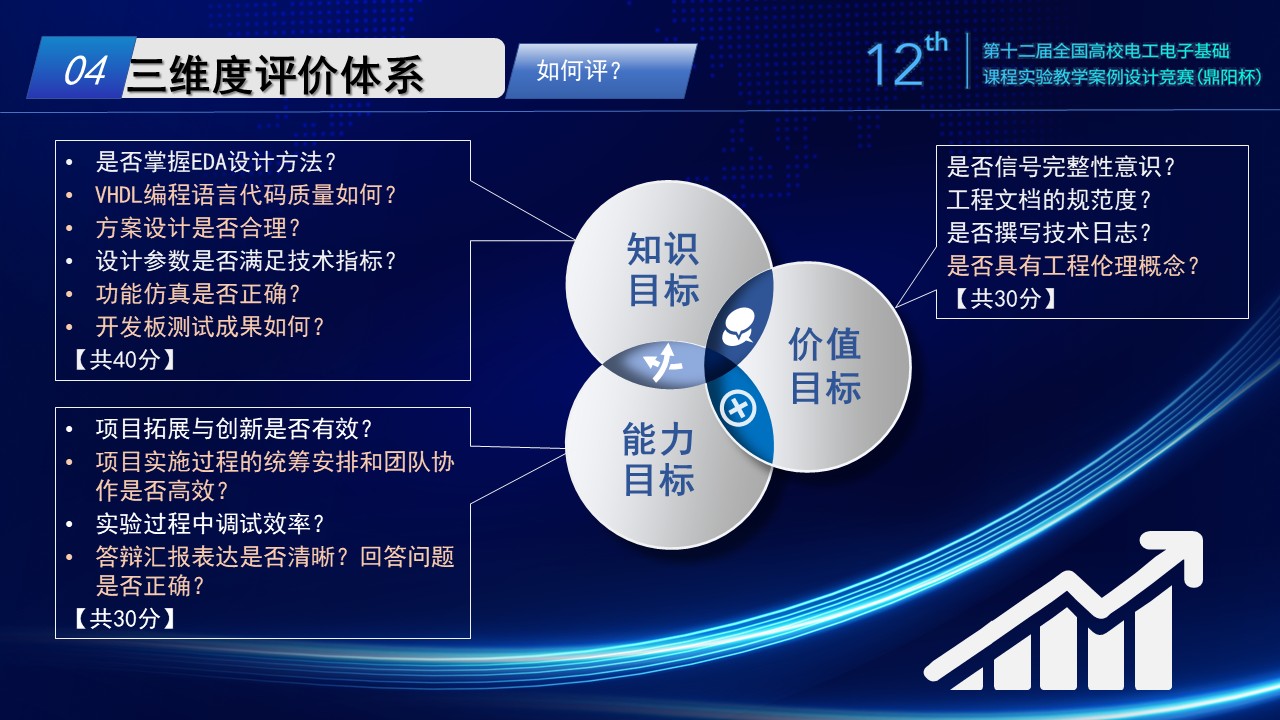

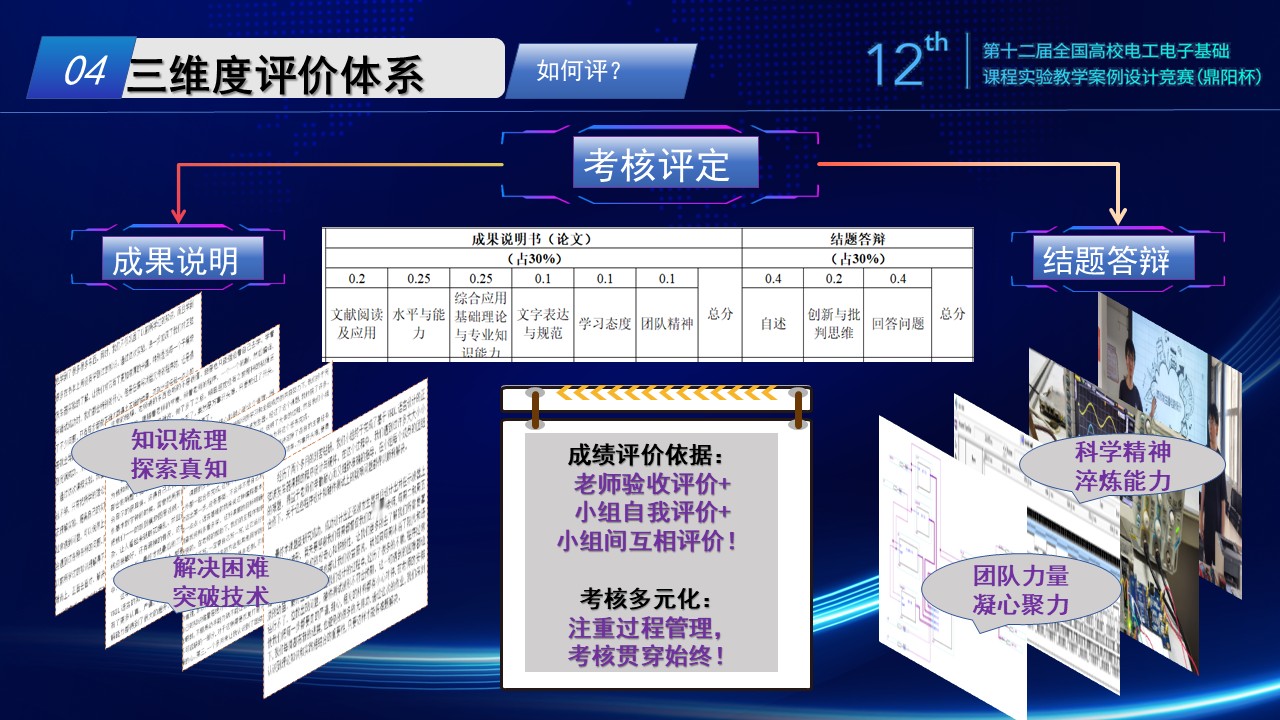

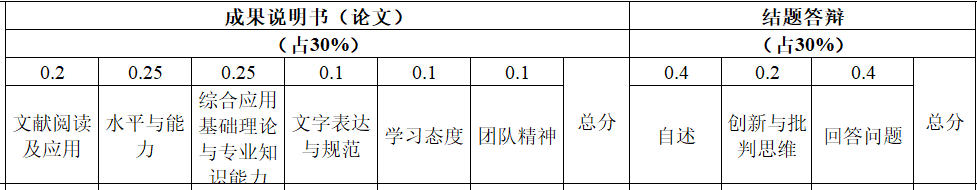

围绕知识、能力和价值三维度建立评价体系,采用多元考核评价机制,综合评估学生的创新探索、工程实践、自主学习等综合素质,成绩评定主要由实验预习、过程管理、实验验收、实验报告、答辩汇报等五部分成绩总和构成。

(1)知识目标:是否掌握EDA设计方法?VHDL编程语言代码质量如何?方案设计是否合理?设计参数是否满足技术指标?功能仿真是否正确?开发板测试成果如何?(共40分)

(2)能力目标:项目实施过程的统筹安排和团队协作是否高效?实验过程中调试效率?答辩汇报表达是否清晰?回答问题是否正确?(共30分)

(3)价值目标:是否具有信号完整性意识?工程文档的规范度?是否撰写技术日志?

是否具有工程伦理概念?(共30分)

图17 实验考核明细图

工程教育创新特色(150字)

①基于OBE理念,AI赋能,虚实双驱——动态演示,具象化DDS核心技术;

②剖析中外FPGA技术,探讨芯片工程应用,激发科技强国使命感——思政融合;

③锻炼工匠精神,孵化多支省级竞赛团队——赛教融合;

④项目实训达成“电路设计-VHDL实现-软件仿真-硬件验证”的完整闭环过程——系统性工程闭环。

11.实验项目佐证:

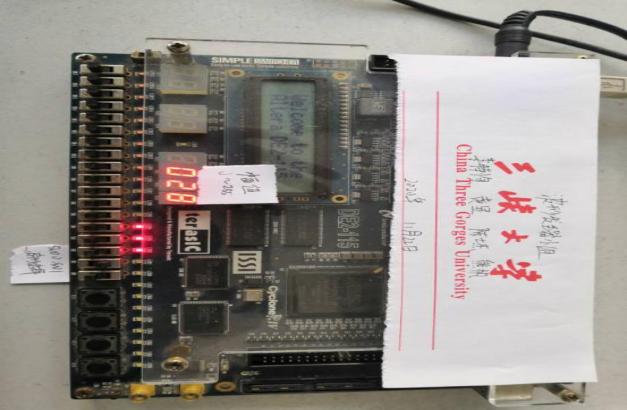

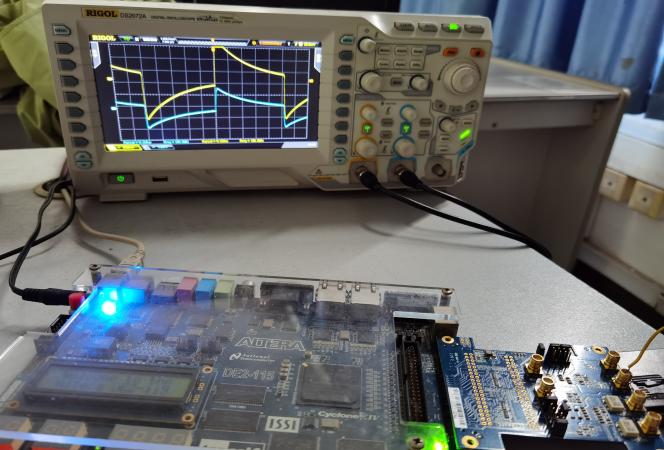

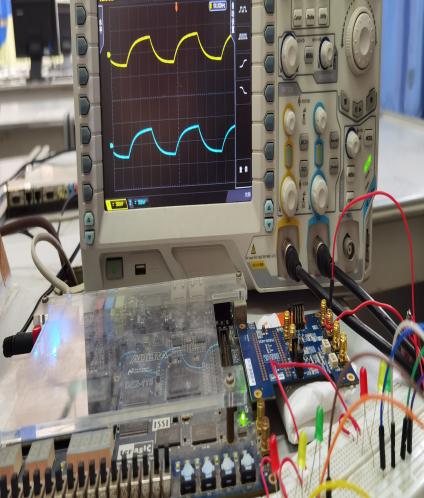

11.1 现场实验照片:

图18 实验室课中课后场景

11.2课程教学大纲:

图 19 课程教学大纲

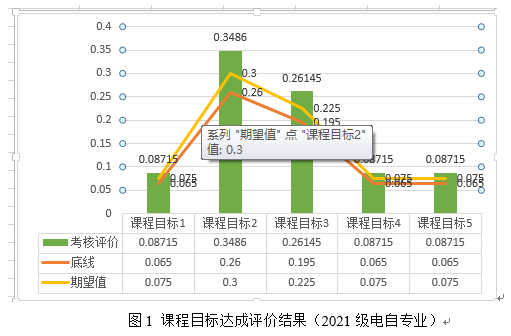

图20 课程目标达成评价结果

11.3实验报告

图21 学生的部分实验报告

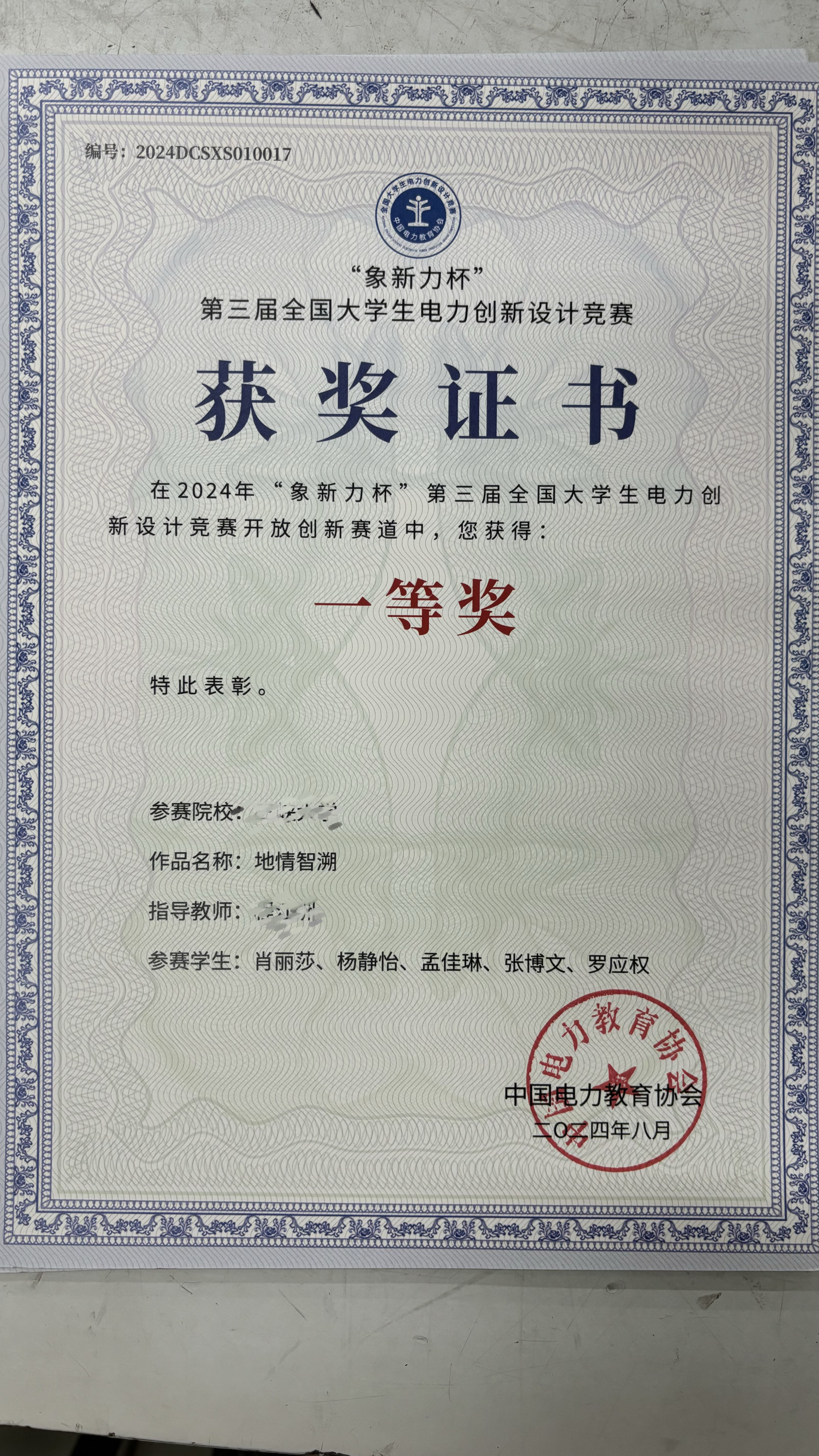

11.4获奖证书:

图22 获奖证书