数字钟的设计

实验题目:数字钟的设计

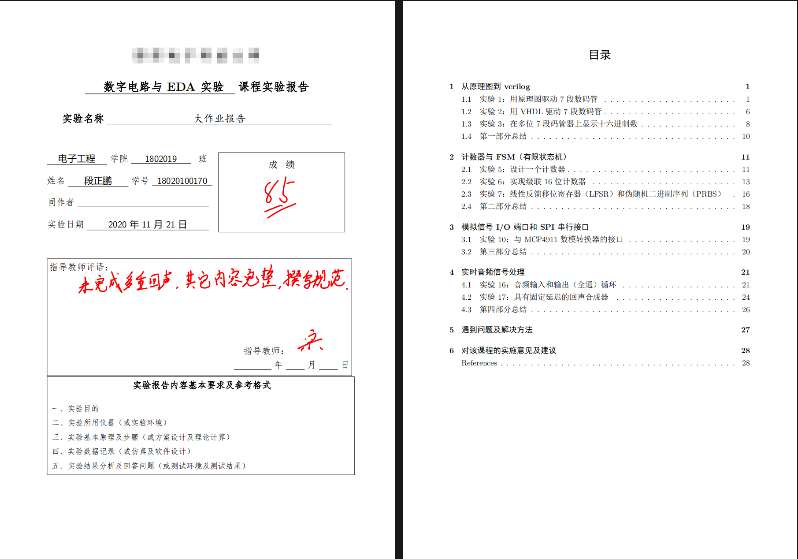

课程简要信息

课程名称:电子电路实践

课程学时:20学时

项目学时:课内12学时,课外8

适用专业:电子信息工程、电子信息工程(中外)

学生年级:大二下学期

实验内容与任务(限500字,可与“实验过程及要求”合并)

项目需要完成的任务(如需要观察的现象,分析某种现象的成因、需要解决的问题等);是否设计有不同层次的任务。

设计一个电子钟,具有正常的时、分、秒计时功能,能进行手动校时和整点报时,并具有闹钟功能、定时、整点报时等功能。

1)基本要求:

准确计时,以数字形式显示时、分、秒的时间;

使用计数器芯片实现60进制(秒/分)和24进制(时);

利用两个单刀双掷开关分别对时位和分位进行校准;

- 进阶要求:

小时的计时要求可切换为12进制(时);

手动校时可分为快调和慢调两种;

整点报时可报整点时数或触摸报时;

能实现自定义闹钟,闹钟响声时间可调。

- 拓展要求:

基于FPGA开发平台及硬件描述语言程序编写等功能

实验过程及要求(限300字)

如对学生在实验过程中在需求分析、资料查询、自学预习、思考讨论、方法设计、进程规划、软件仿真、平台构建、器件选择、表格设计、现象观察、数据测试、问题分析、总结报告、验收答辩、演讲交流等各方面的要求。

-

确定方案:教师课前将项目内容发布给学生,学生提前查阅资料,确定一个初步方案。教师课内让学生汇报自己的方案,讨论,最终确定总体方案和框图。

-

实验箱或者面包板电路搭建:学生可以先利用对各个模块电路分布调试,然后再进行联调。

-

电路仿真:利用仿真软件Protues,完成电路图的虚拟链接,通过仿真学习振荡器的设计、分频器电路的设计、时、分、秒计数器的设计、显示电路设计、校时电路的设计等,并对各个设计进行验证。

仿真检查通过后,方可领取器件进行实际电路的搭建。

4)小规模搭建电路:学生可直接利用AD软件或立创EDA软件进行原理图和PCB绘制,再进行工厂制板。

5)电路的测试与调试:

小规模集成电路调试:确保电路焊接无误后,接通电源,测试电源是否正常工作。电源正常工作后,分级调试,如各级都调试无误后,可以进行全面电路性能测试,边测量、边记录、边分析。

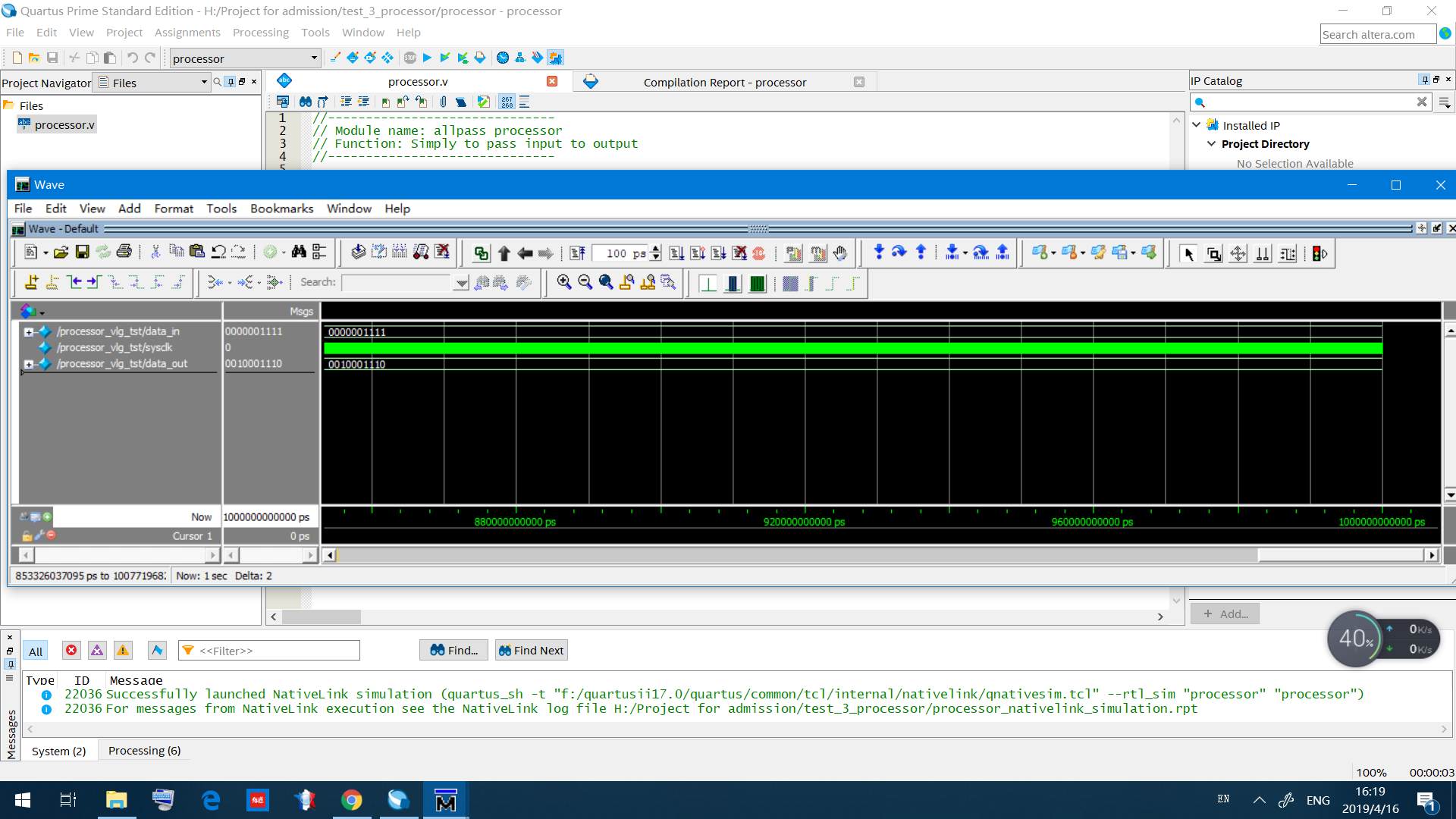

6)FPGA开发板调试:学生利用EDA软件对各个小模块进行HDL语言编写、仿真、综合调试和在开发板上进行调试。

7)撰写设计总结报告,并通过分组演讲,学习交流不同解决方案的特点。

相关知识及背景(限150字)

项目涉及所需的知识方法、实践技能、应用背景、工程案例。

这是一个针对数字系统的典型应用,需要学生在明确选题所需实现的电路功能和主要指标等训练任务后,自主查阅参考资料,完成功能电路的原理设计、软件仿真、实物制作和运行测试四个环节,提交电路板实物,并撰写总结报告。通过本课程训练,加深学生对典型模拟电路、数字电路、EDA设计的理解,掌握常用电子电路的分析、设计和应用方法。

实验环境条件

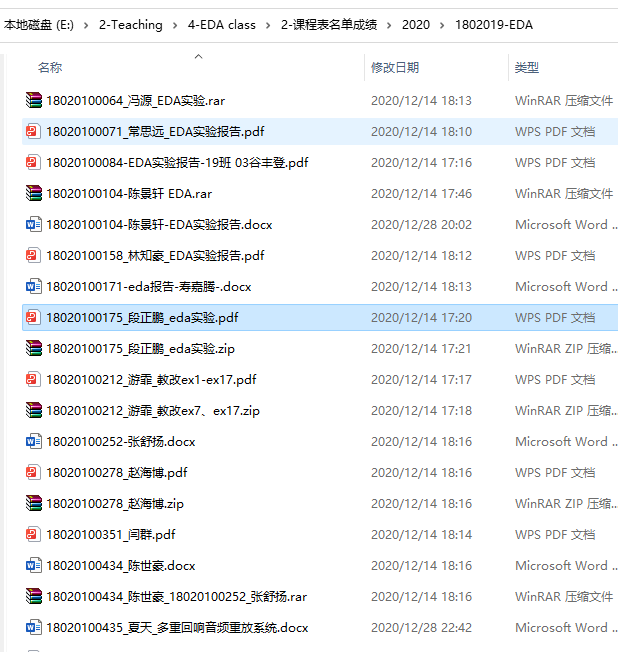

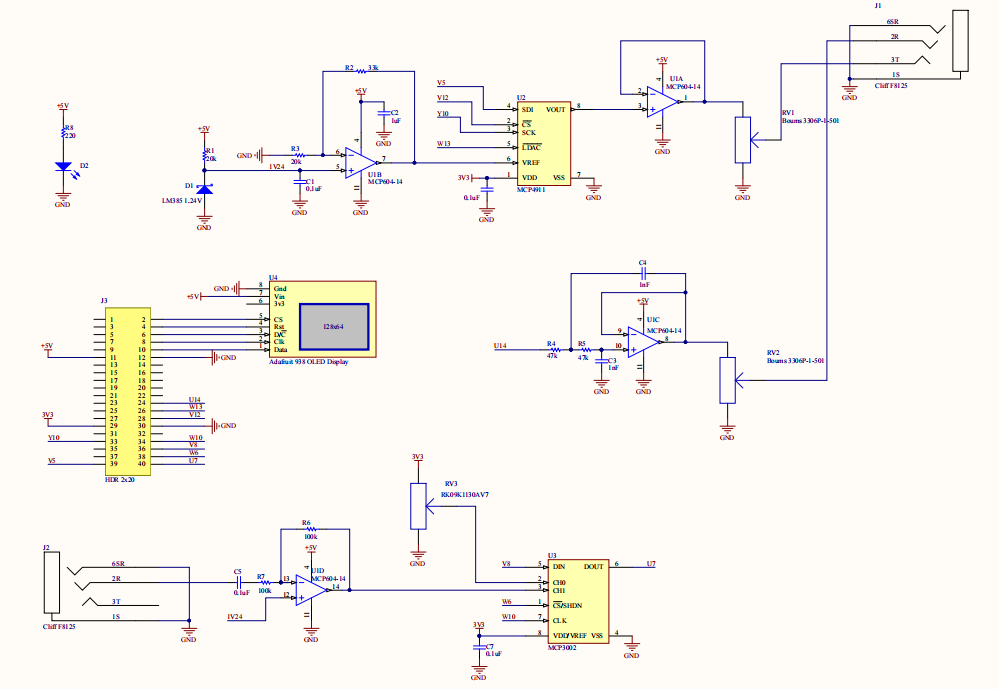

硬件资源如图所示。为该项目实施提供DE2开发板、高云F0开发板、高云自制平台、74LS04、74LS00、74LS90、74LS48、CD4013、CD4046、直流稳压电源、锂电池充电器、数字万用表、示波器等仪器;实验室电脑均配置安装Altium Desiner软件开发平台、EDA软件、Protues等软件。

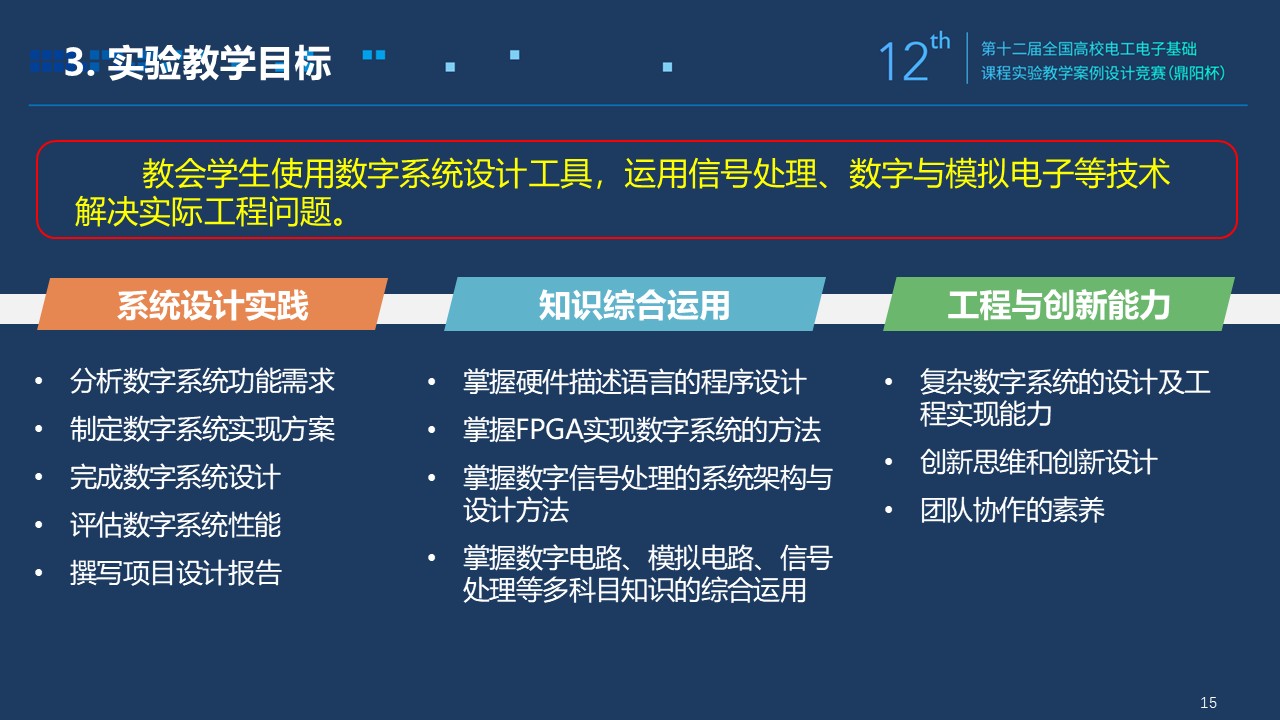

教学目标与目的(限150字)

如学习、运用知识、技术、方法等;培养、提升技能、能力、素质等。

利用所学的模拟电路与数字电路相关理论知识,从数字钟的选题入手、到原理设计、软件仿真,最后完成实物制作和功能测试,在系统的电子电路实践过程提高学生的工程应用和操作能力,培养学生严谨的实验态度和科学素养;课程结合工程应用实际,通过分析问题,解决问题,发挥学生主观能动性,培养学生探索精神;使用现代行业专业工具分析测试,培养良好的职业规范和专业素质;加强沟通交流、语言表达和撰写报告的能力。

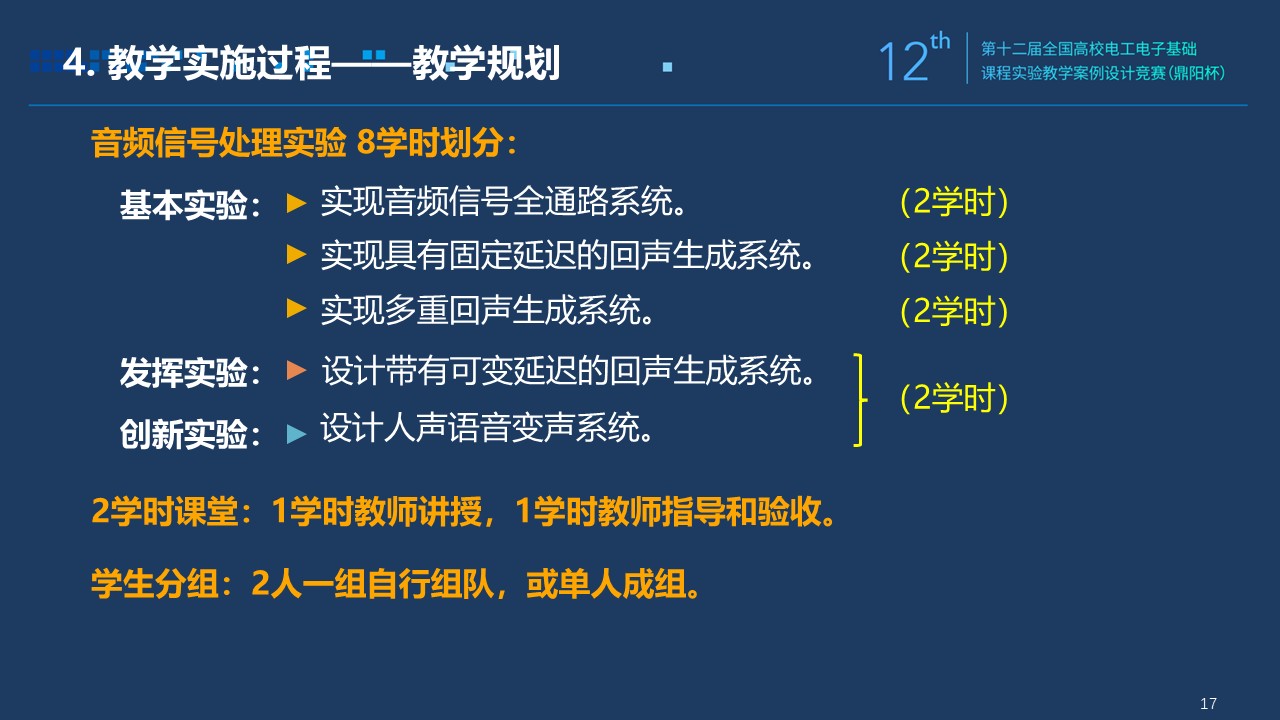

教学设计与实施进程

课堂知识讲解、方法引导、背景解释;实验中的方法指导,问题设置、思路引导等。教学模式、实验渠道、研讨主题、观察节点、验收重点、质询问题等方面设计等。实验实施进程的各个环节(如任务安排、预习自学、现场教学、分组研讨、现场操作、结果验收、总结演讲、报告批改等)中教学设计的思路、目的,教师、学生各自需要完成的工作任务,需要关注的重点与细节。

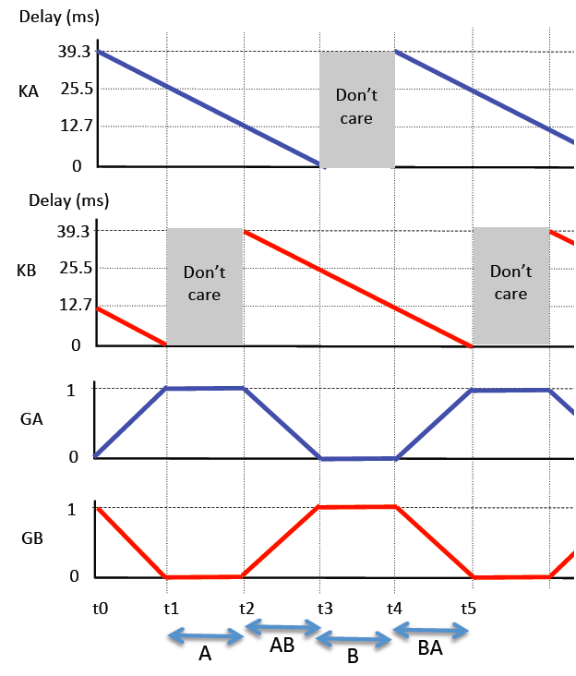

- 项目数字钟的教学设计思路如图所示,项目按照三阶段来进行。

2)一阶段(逻辑验证+单元调试)

老师提前发布任务,学生自行完成组队,确认硬件电路分工,登记信息,通过阅读教师提供的参考文献、查阅资料,完成需求分析及初步方案设计。

该阶段由指导老师给学生简单讲解数字钟的相关知识、特点,演示数字钟的功能,对技术指标进行讲解,让学生了解其工程背景;教师邀请同学上台进行初步方案的分享,过程中引导学生进行方案选择的深层次思考,如振荡器的精度、抗干扰能力,学生需要从晶振温漂、分频电路累积误差参数分析。对典型问题及反馈的共性问题作出回答。学生对基本要求功能可以在实验箱、万用板进行验证。最后学生对各个独立单元模块进行调试,完成数字钟基本功能设计。教师完成学生实验箱和面包板搭建的验收,记录分频器、计数器、校时电路等指标。

3)二阶段(系统仿真+综合设计)

系统仿真:学生经过第一阶段的搭建,能确定数字钟的设计实现方案,开始进行整个系统的Protues仿真验证,并将仿真方案在课堂上进行分享,教师进行点评。然后学生开始进行原理图和PCB设计。

综合设计:教师针对项目电路的特征及共性问题,讲解画 PCB

板应注意的事项,了解元器件布局时需要注意封装、放置位置的影响,实际电路在制板时需要预留电源接口、测试口、接地口等。

学生根据课堂讲解和教师点评等反馈内容进一步优化电路原理图设计,经验收后下单制板。

教师提针对电路板讲解不同封装元器件的焊接注意事项。调试时,引导学生按照信号传输方向逐级调试,通过现象分析问题、从而排查定位问题。

学生完成电路板焊接,并进行电路调试。调试遇到问题时,可请教教师。在电路调试完成后,利用实验室仪器完成整个电路的指标测试。

教师对成品电路板进行指标验收,验收过程中对焊接技术、资源使用、电路指标等进行记录。根据验收数据,分档进行评分。

4)三阶段(编程实现)

**编程实现:**教师先进行基础知识铺垫,讲解FPGA开发流程和硬件电路基础,再对数字钟的分频模块、计数模块、数码管显示模块进行讲解;学生完成各个模块的HDL语言编写和仿真调试讲解,最后进行系统集成和调试,教师对学生的成品进行指标验收。

实验原理及方案

实验的基本原理、设计依据、完成任务的思路方法,可能采用的方法、技术、电路、器件。

- 系统结构

系统结构框图如图1所示。

图1 系统结构框图

数字钟电路系统由主体电路和扩展电路两大部分所组成 ,振荡器产生的稳定的高频脉冲信号,作为数字钟的时间基准,再经分频器输出标准秒脉冲,秒计数器计满60后向分计数器进位,再通过译码器电路控制数码管显示。扩展电路,包含定时控制,防电台报时,报整点时数和触摸整点报时。

- 小规模集成电路实现方案

① 振荡器的设计

振荡器是数字钟的核心。振荡器的稳定度及频率的精确度决定了数字钟计时的准确程度,通常选用石英晶体构成振荡器电路。一般来说,振荡器的频率越高,计时精度越高。晶体振荡器电路图如图2所示。如图所示为电子手册集成电路(如5C702)中的晶体振荡器电路;常取晶振的频率为32768Hz,因其内部有15级2分频集成电路,所以输出端正好可得到1Hz的标准脉冲。

图2 晶体振荡器电路图

如果精度要求不高也可以采用由集成逻辑门与RC组成的时钟源振荡器或由集成电路定时器555与RC组成的多谐振荡器,如图3所示。

图3 NE555多谐振荡电路

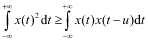

② 分频器的设计

分频器的功能主要有两个:一是产生标准秒脉冲信号; 二是提供功能扩展电路所需要的信号,如仿电台报时用的1kHz的高音频信号和500Hz的低音频信号等 。秒脉冲产生电路的设计如图4所示。振荡器中的非门和分频电路通常由一块集成电路CD4060(14位二进制串行计数器)实现。

图4 秒脉冲产生电路的设计图

③ 时、分、秒计数器的设计

分和秒计数器都是模M=60的计数器,小时计数器是一个“24进制”的特殊进制计数器或者是一个“12翻1”的特殊进制计数器。

可采用的芯片:

4位二进制同步加法计数器芯片74X161、74X163;

4位二进制同步可逆计数器芯片74X191、74X193;

8421BCD码同步加法计数器芯片74X160等等。

计数器设计图如图5-6所示。

图5 模60计数器 图6 模24计数器

④ 译码显示电路设计

74LS47、74LS48为BCD—7段译码/驱动器。74LS47可用来驱动共阳极的发光二极管显示器示器;74LS48则用来驱动共阴极的发光二极管显示器。显示电路图如图7所示。

图7 显示电路图

⑤ 校时电路的设计

校时电路的设计如图8所示。

图8 校时电路的设计图

在图中,如果校时脉冲由单次脉冲产生器提供,则可以进行“慢校时”,当S1或S2分别为“0”时可进行“快校时” 。其中S2为校“时”用的控制开关 ,S1为校“分”用的控制开关。需要注意的是,校时电路是由与非门构成的组合逻辑电路,开关S1或S2为“0”或“1”时,可能会产生抖动,接电容C1、C2可以缓解抖动。必要时还应将其改为去抖动开关电路。

⑥ 定时控制电路的设计

例:要求上午7时59分发出闹时信号,持续时间为1分钟。

解:7时59分对应数字钟的时个位计数器的状态为(Q3Q 2Q 1Q 0)H1=0111,分十位计数器的状态为(Q3Q2Q1Q0)M2=0101,分个位计数器的状态为(Q3Q2Q1Q0)M1=1001。若将上述计数器输出为“1”的所有输出端经过与门电路去控制音响电路,可以使音响电路正好在7点59分响,持续1分钟后(即8点时)停响。

定时控制电路的设计如图9所示。数字钟在指定的时刻发出信号,或驱动音响电路“闹时”。

图9 定时控制电路的设计图

由图可见上午7点59分时,音响电路的晶体管导通,则扬声器发出1kHz的声音。持续1分钟到8点整晶体管因输入端为“0”而截止,电路停闹。

- 应用FPGA的实现方案

以FPGA为设计平台,数字钟的工作原理不变,但是实际设计时可采用硬件描述语言来实现,系统的搭建和调试更灵活、高效。系统的组成由以下的核心模块构成:秒脉冲模块、时分秒模块和显示译码器模块等。

① 秒脉冲模块的设计

FPGA开发板的时钟是50MHz,可通过分频器将高频时钟降到1Hz。因此需确定降频系数N,N=F

clk/Ftarget−1,例如50MHz时钟需分频至1Hz时,降频系数N为49,999,999。秒脉冲模块设计以EDA硬件描述语言来实现。参考如下:

module clk_div (

input clk, // 输入高频时钟(如50MHz)

input reset, // 复位信号

output reg clk_1hz // 输出秒脉冲

);

reg [32:0] counter; // 计数器位宽需满足分频系数(如50MHz需27位)

always @(posedge clk or posedge reset) begin

if (reset) begin

counter <= 0;

clk_1hz <= 0;

end else if (counter == 49999999) begin // 50MHz分频至1Hz

counter <= 0;

clk_1hz <= ~clk_1hz; // 翻转输出实现50%占空比

end else begin

counter <= counter + 1;

end

end

endmodule

② 时分秒模块的设计

时分秒的运行机制是时钟的核心模块。分和秒是60进制计数器,而小时是24进制计数器。在FPGA中实现时,为了方便在数码管中显示,采用BCD码设计模式。因此分和秒从零计数到59,归零,并输出溢出信号,以便于级联。

以分和秒的计数为例,计数器内部分为六进制(十位,0~5)和十进制(个位,0~9)。计数器模块设计,参考如下。

module counter60 (

input clk, // 系统时钟

input reset, // 异步复位(高有效)

input enable, // 计数使能(高有效)

output [7:0] bcd // 输出BCD码(高4位为十位,低4位为个位)

);

reg [3:0] cnt_units; // 个位计数器(0-9)

reg [3:0] cnt_tens; // 十位计数器(0-5)

// 个位计数逻辑

always @(posedge clk or posedge reset) begin

if (reset) begin

cnt_units <= 4'd0;

end else if (enable) begin

if (cnt_units == 4'd9) begin

cnt_units <= 4'd0;

end else begin

cnt_units <= cnt_units + 1;

end

end

end

// 十位计数逻辑(由个位进位触发)

always @(posedge clk or posedge reset) begin

if (reset) begin

cnt_tens <= 4'd0;

end else if (enable && (cnt_units == 4'd9)) begin

if (cnt_tens == 4'd5) begin

cnt_tens <= 4'd0;

end else begin

cnt_tens <= cnt_tens + 1;

end

end

end

assign bcd = {cnt_tens, cnt_units}; // BCD码输出

assign carry = (cnt_tens == 4'd5) && (cnt_units == 4'd9); // 进位信号

endmodule

小时是采用24进制的计数器,与上述的60进制计数器相似,只需将十位中的比较值由5改为1,即可换位小时专用的24进制的计数器。

③ 显示译码器模块的设计

时、分、秒的计数器输出为BCD码,因此可将数据显示与数码管或者液晶屏上。以6位共阴数码管为例,将时钟的时分秒的个位和十位分别显示于相应位的数码管上。其中数码管的段码,可以直接将数据放置段码输入端。参考设计如下。

module seg7_decoder (

input [3:0] bcd,

output reg [6:0] seg // 格式:abcdefg(低电平点亮)

);

always @(*) begin

case(bcd)

4'd0: seg = 7'b1000000; // 0

4'd1: seg = 7'b1111001; // 1

4'd2: seg = 7'b0100100; // 2

4'd3: seg = 7'b0110000; // 3

4'd4: seg = 7'b0011001; // 4

4'd5: seg = 7'b0010010; // 5

4'd6: seg = 7'b0000010; // 6

4'd7: seg = 7'b1111000; // 7

4'd8: seg = 7'b0000000; // 8

4'd9: seg = 7'b0010000; // 9

default: seg = 7'b1111111; // 灭

endcase

end

endmodule

而位码以一定的频率来刷新,实现稳定的显示效果。以6位数码管刷新为例,参考设计如下:

module scan_controller (

input clk_1khz,

input [23:0] time_data, // 时分秒BCD码拼接(hh:mm:ss)

output reg [5:0] sel, // 位选信号(低有效)

output [6:0] seg // 段码输出

);

reg [2:0] cnt_sel; // 数码管选择计数器(0-5)

reg [3:0] current_data; // 当前显示数据

// 动态扫描逻辑

always @(posedge clk_1khz) begin

cnt_sel <= (cnt_sel == 3'd5) ? 3'd0 : cnt_sel + 1;

case(cnt_sel)

0: begin sel = 6'b111110; current_data = time_data[3:0]; end // 秒个位

1: begin sel = 6'b111101; current_data = time_data[7:4]; end // 秒十位

2: begin sel = 6'b111011; current_data = time_data[11:8]; end // 分个位

3: begin sel = 6'b110111; current_data = time_data[15:12]; end // 分十位

4: begin sel = 6'b101111; current_data = time_data[19:16]; end // 时个位

5: begin sel = 6'b011111; current_data = time_data[23:20]; end // 时十位

endcase

end

// 实例化译码器

seg7_decoder u_decoder(.bcd(current_data), .seg(seg));

endmodule

最后,将所有的模块集成,为数字钟系统。如果加入时钟调整按键,可以加入异步时钟调整模块即可。

实验报告要求

实验报告需要反映以下工作:

-

实验分析:查阅、了解设计的意义及相关技术的国内外发展现状;

-

实现方案论证:对比、论证设计方案,确定技术路线;

-

实验过程设计:围绕设计目标完成特殊元器件选型与硬件电路设计,软件系统设计;

-

实验数据记录:硬件电路及软件系统的调试过程记录数据记录测试记录;

-

数据处理分析:以测试数据为基础,结合理论,按照科学分析方法对实验数据进行归纳、总结,获得相应的结论或结果,实验中出现的故障及解决方法;

-

实验结果总结:根据实验数据进行分析和问题的讨论与思考。

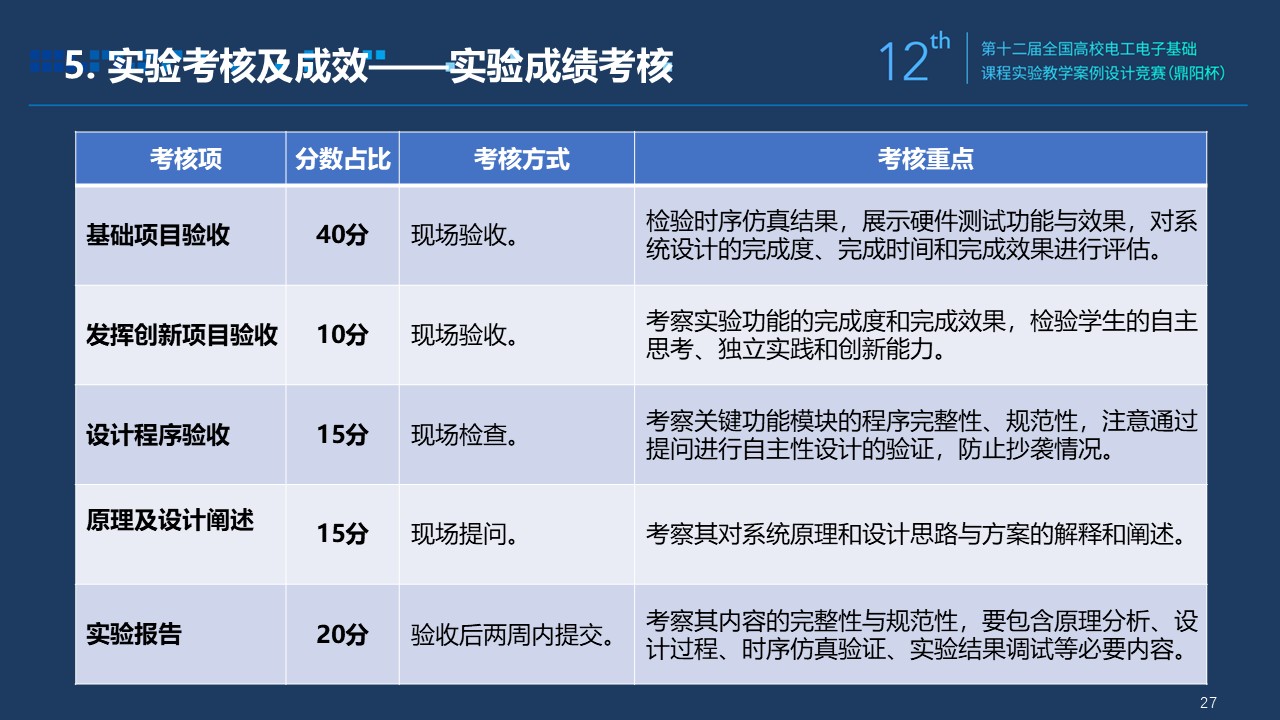

考核要求与方法(限300字)

-

实物验收:设计方案的合理性、系统的功能与性能指标的完成程度,完成时间长短;

-

实物质量:电路板外观、元器件布局、焊接质量、组装工艺、工作量等;

-

自主创新:电路设计的创新性;

-

仿真实现:是否能使用仿真软件进行正确仿真,是否能够对电路进行分析;

-

调试能力:是否具备独立思考能力,是否具备发现并解决问题的能力;

-

设计报告:设计报告图、表的规范性内容的完整性;

-

演讲答辩:PPT内容展示表达能力应变能力和回答的准确性。

项目特色或创新(可空缺,限150字)

本项目特色在于:

-

技术驱动实验平台升级:以FPGA平台取代实验箱构建硬件基础,集成工具链与仿真系统形成软硬协同生态,通过激励机制驱动创新力。

-

项目重构:将数字电路升级为跨域开放命题(融物联网/嵌入式等场景)。通过问题导向训练,强化系统架构与创新实践能力,实现电路→工程创新跃迁。

-

工程思维迁移:通过硬件架构与设计方法论的跨领域复用,将项目升维为"方法论训练载体",实现"解决个案→掌握通类"的能力跃迁。